Open-Source-Chipdesign

»Hardware so einfach wie Software entwerfen«

Als Keynote-Sprecher des Student Days der embedded world stellte Prof. Yungang Bao aus Peking die Aktivitäten in China und international zum Open-Source-Chipdesign vor. RISC-V ist dabei nur eine von drei wichtigen Säulen.

Die Einführung von Open-Source-Software hat die Softwarebranche umgekrempelt. Sie hat vor allem die Entwicklungs- kosten gesenkt und die Entwicklungszyklen beschleunigt. Kleine Gruppen von Softwareentwicklern sind nun in der Lage, ihre innovativen Ideen mithilfe von Open-Source-Paketen, -Bibliotheken und -Werkzeugen umzusetzen.

Inspiriert vom gemeinschaftlichen Ansatz der Open-Source-Softwareszene haben agile und quelloffene Chips in den vergangenen zehn Jahren in Wissenschaft und Industrie an Bedeutung gewonnen. Im Workshop »Architecture 2030« im Jahr 2016 entstand in Zusammenarbeit mit dem International Symposium on Computer Architecture (ISCA) die Vision eines Hardwaredesigns, das die Zugänglichkeit von Software widerspiegelt: »Hardware soll so einfach zu entwerfen/schreiben sein wie Software – quelloffen« [1]. Aufbauend auf dieser Vision brachte der SIGARCH Visioning Workshop der ISCA 2019 führende Köpfe zusammen, um »Agile and Open Hardware for Next-Generation Computing« [2] zu erforschen. Die anschließende Veröffentlichung der Sonderausgabe »Agile and Open-Source Chip« des Magazins IEEE MICRO im Jahr 2020 zeigte bedeutende Fortschritte in diesem Bereich auf. Mittlerweile ist das Konzept von Open-Source-Chips von der Theorie zur Realität geworden und ist im Begriff, technologische Vorgehensweisen umzugestalten.

Jobangebote+ passend zum Thema

Chipdesign in drei Stufen

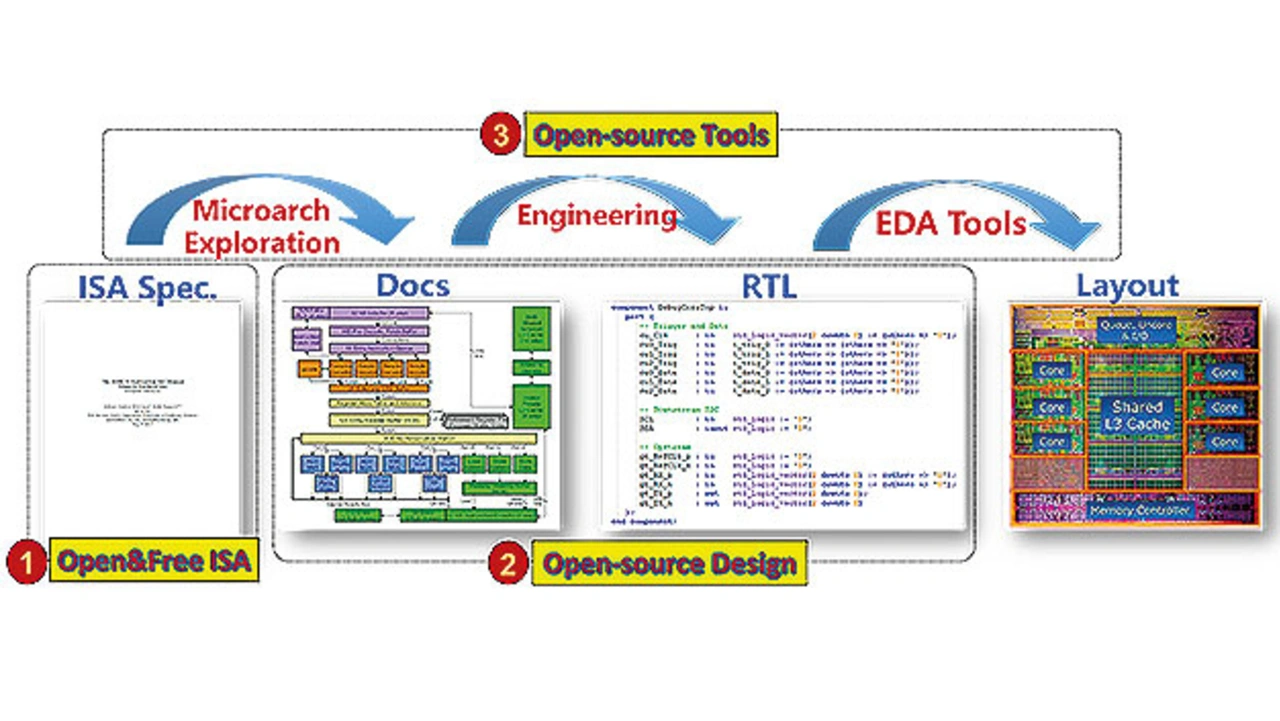

Im Gegensatz zum Open-Source-Software-Ökosystem, dessen Umfang in den Bereich zweistelliger Milliarden-Dollarsummen geht, steckt Open-Source im Chipdesign noch in den Kinderschuhen. Der traditionelle Weg zur Entwicklung eines Prozessors gliedert sich grob in drei Hauptphasen.

➔ Entwurf der Mikroarchitektur in Übereinstimmung mit einer Befehlssatzarchitektur (Instruction Set Architecture, ISA).

➔ Implementierung des Mikroarchitekturentwurfs mit erheblichem technischem Aufwand, in der Regel durch Codierung auf Register-Transistorebene zur Beschreibung der chipinternen Verdrahtung.

➔ Übersetzung des RTL-Designs in ein physisches Chiplayout mit EDA-Tools (Electronic Design Automation) als Vorbereitung für die Produktion.

Trotz des bemerkenswerten Einflusses der quelloffenen RISC-V-Architektur im Ökosystem bleibt eine erhebliche Lücke zwischen der Befehlssatzarchitektur und der Fertigstellung eines Chipdesigns. Um ein umfassendes Open-Source-Chip-Ökosystem zu schaffen, müssen alle drei Ebenen des Open-Sourcing berücksichtigt werden, wie in Bild 1 dargestellt.

➔ Ebene 1: Offene und freie Behlssatzarchitektur – Behlssatzarchitekturen dienen als Spezifikationen, die frei zugänglich sein sollten, sodass jedes Unternehmen sie ohne Einschränkungen für den Entwurf und die Implementierung von Prozessoren verwenden kann. Ein Beispiel dafür ist RISC-V.

➔ Ebene 2: Open-Source-Design – De- tails der Implementierungsebene sollten frei zugänglich sein, z. B. Quellcodes, Dokumente usw. In diese Kategorie fallen Projekte, wie RocketChip, BOOM und XiangShan.

➔ Ebene 3: Open-Source-Tools – Design- und Verifikationswerkzeuge, Plattformen und andere wichtige Tools sollten quelloffen sein. Beispiele auf dieser Ebene sind OpenRoad und die agile Entwicklungsmethodik »MinJie«.

Implementierungsdetails und EDA-Werkzeuge

Auch wenn RISC-V weltweit stark an Bedeutung gewonnen hat, ist die Zahl der erfolgreichen Open-Source-Chipprojekte der Ebenen 2 und 3 nach wie vor begrenzt. Daher seien hier zwei Projekte vorgestellt: die RISC-V-CPU XiangShan [3] und die agile-Entwicklungsmethodik MinJie [4], die beide Open-Source und frei zugänglich sind (veröffentlicht auf MICRO‘22 und ausgewählt als IEEE MICRO Top Picks). Es ist bemerkenswert, dass sowohl XiangShan als auch MinJie in der Branche breite Akzeptanz gefunden haben. Die Gründung des Beijing Institute of Open Source Chip (BOSC), einer Non-Profit-Organisation (NPO), die von 18 prominenten Unternehmen unterstützt wird, unterstreicht das Engagement, die Entwicklung von XiangShan und MinJie in Zusammenarbeit mit Industriepartnern voranzutreiben. Vorrangiges Ziel ist es, XiangShan zu einer beispielhaften Forschungsplattform zu machen, die zeigt, wie Wissenschaft und Industrie zusammenarbeiten können.

Die neueste Generation V3 von XiangShan hat sich als die leistungsstärkste CPU unter allen Open-Source-Prozessoren herauskristallisiert und eine wettbewerbsfähige Grundlage für die zukünftige Forschung in der Computerarchitektur geschaffen. Einerseits überwindet die Entwicklung der XiangShan-Prozessoren bedeutende Herausforderungen und fördert ein innovationsfreundliches Umfeld. Andererseits ist XiangShan mit dem MinJie-Entwicklungswerkzeug ein Beispiel für die Umsetzbarkeit dieses neuen Entwicklungskonzepts, das weitere Forschungs- und Entwicklungsteams ermutigen könnte, diesen Ansatz ebenfalls zu übernehmen. Wie im MICRO‘22-Beitrag gezeigt wird, hat ein Doktorand im dritten Jahr innerhalb weniger Stunden eine Mikroarchitekturtechnik auf XiangShan implementiert und ihre Leistungsfähigkeit mit MinJie-Tools validiert. Darüber hinaus erleichtert die Unterstützung durch die Industrie das Tape-out, also die Erstellung der Masken zur Halbleiterproduktion. Dadurch können Forschungsideen in erprobte Silizium-Muster umgesetzt werden, was die Zusammenarbeit zwischen Wissenschaft und Industrie beschleunigt.

Als Open-Source-Tool hat MinJie verschiedene Entwicklungswerkzeuge integriert und wird weiterentwickelt mit neuen Funktionen wie Leistungsmodellierung, formaler Verifikation und sicheren Enclave-Tools. In Verbindung mit XiangShan hat es das Potenzial, als aktive Plattform für die Validierung neuartiger Methoden auf realen, groß angelegten Chipdesigns zu dienen.

Fast das gesamte Chipdesign aus Open-Source

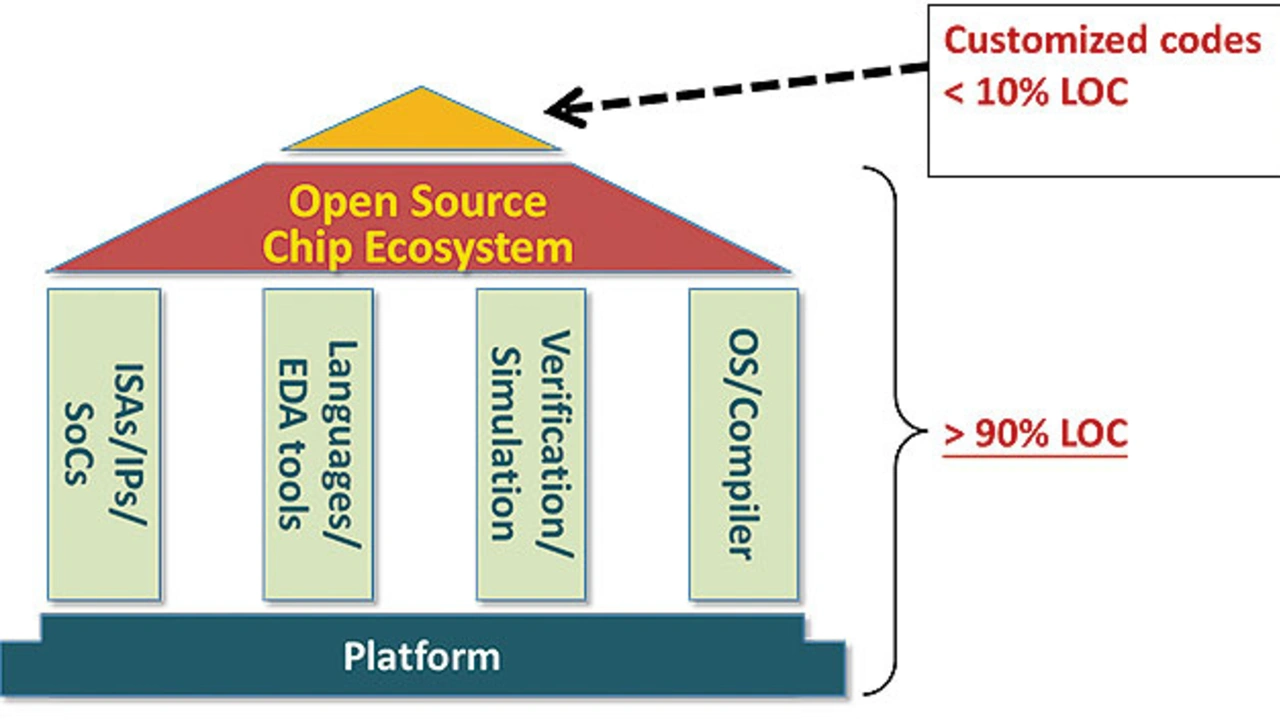

Seit 2016 sind acht Jahre vergangen, doch die Vision, »Hardware so einfach zu entwerfen/schreiben wie Software – quelloffen« ist nach wie vor lebendig. Wie wird der Stand des Open-Source Chip-Ökosystems in weiteren sieben Jahren sein?

Ich bin der festen Überzeugung, dass diese Vision irgendwann Wirklichkeit werden wird, wenn auch nicht bis 2030. Bis dahin ist es denkbar, dass bis zu 90 % der Codezeilen eines Chipdesigns aus einem in sich geschlossenen Open-Source Chip-Ökosystem stammen könnten, das eine Fülle von Open-Source-Komponenten für den agile Entwurf kundenspezifischer Designs umfasst (Bild 2).

Referenzen

[1] Ceze, L.; Wenisch, T.; Hill, M. et. al.: Architecture 2030 at ISCA 2016.

http://arch2030.cs.washington.edu/slides/arch2030_intro.pdf

[2] Agile and Open Hardware for Next-Generation Computing. SIGARCH Visioning

Workshop, 2019. https://sites.google.com/view/agile-and-open-hardware

[3] XianShan, Open Source RISC-V-Processor Project. https://github.com/OpenXiangShan/XiangShan

[4] Towards Developing High Performance RISC-V Processors Using Agile Methodology.

55th IEEE /ACM International Symposium on Microarchitekture (MICRO), 2022. https://github.com/OpenXiangShan/XiangShan-doc/blob/main/publications/micro2022-xiangshan.pdf

Der Autor

Prof. Yungang Bao ist stv. Direktor an der University of China‘s Academy of Sciences, Institute of Computing Technology (ICT).