Neue Debug-Schnittstellen: weniger Leitungen, mehr Information

Fortsetzung des Artikels von Teil 1

Neue Debug-Schnittstellen: weniger Leitungen, mehr Information

Verringerung der Debug-Signalleitungen

Von der Verringerung der für den Debug-Zugang notwendigen Signale profitiert übrigens auch der Anwender. Wegen des meist knappen Platzes auf der Serienleiterplatte und der Kosten für die Steckverbinder wird auf eine Debug-Schnittstelle oft ganz verzichtet. Denn weniger Signalleitungen bedeuten i.d.R. auch reduzierten Platzbedarf und kleinere Steckverbinder.

Jobangebote+ passend zum Thema

Ein weiterer Grund für die Suche nach neuen Ansätzen ist das Problem mit der zu kurzen Verbindungsleitung zwischen Mikrocontroller-Target und Debug-Tool, das meist im Feldeinsatz auftritt. Bei modernen 32-bit-Mikrocontrollern sind JTAG-Taktfrequenzen bis 100 MHz möglich. Damit das Signalkabel nicht zur Antenne wird, ist spätestens nach 25 bis 30 cm eine Signalkonditionierung erforderlich. Dies kann – wie mit dem JTAG-Extender des Universal Access Device 2+ (UAD2+) von pls – mit einem kleinen Konverter dicht am Target und nachfolgender Weiterleitung des aufbereiteten Signals über differenzielle Signalleitungen erfolgen (Bild 1). In jedem Fall ist bei „klassischem“ JTAG eine erste, zur Debug-Lösung gehörende Hardware dicht am Target erforderlich. So ergibt sich – unabhängig vom Hersteller – das bekannte Bild der Debug-Geräte-Lösungen mit dem sehr kurzen Flachbandkabel direkt am Gehäuse.

Ein dritter wichtiger Aspekt, der bei aktuellen Überlegungen der Hersteller eine wichtige Rolle spielt, ist die Erhöhung der Stabilität und Robustheit bei steigender Übertragungsfrequenz und -bandbreite. Im klassischen JTAG-Standard (IEEE 1149.1) gibt es keine Absicherung des Protokolls gegen Störeinflüsse auf die Übertragungsleitungen. Dies war bei der Entwicklung des Standards auch gar nicht vorgesehen, da die Übertragungsrate damals auf 40 MHz begrenzt war und man davon ausging, dass die zu testenden Komponenten immer auf einer Platine untergebracht sind.

Prozessor- und Tool-Hersteller nach neuen Ansätzen suchen. Besonders vielversprechend scheinen hier vor allem der Device Access Port (DAP) von Infineon, die „Serial Wire Debug“-Schnittstelle (SWD) von ARM sowie der herstellerunabhängige Standard IEEE 1149.7 (compact JTAG).

Device Access Port (DAP)

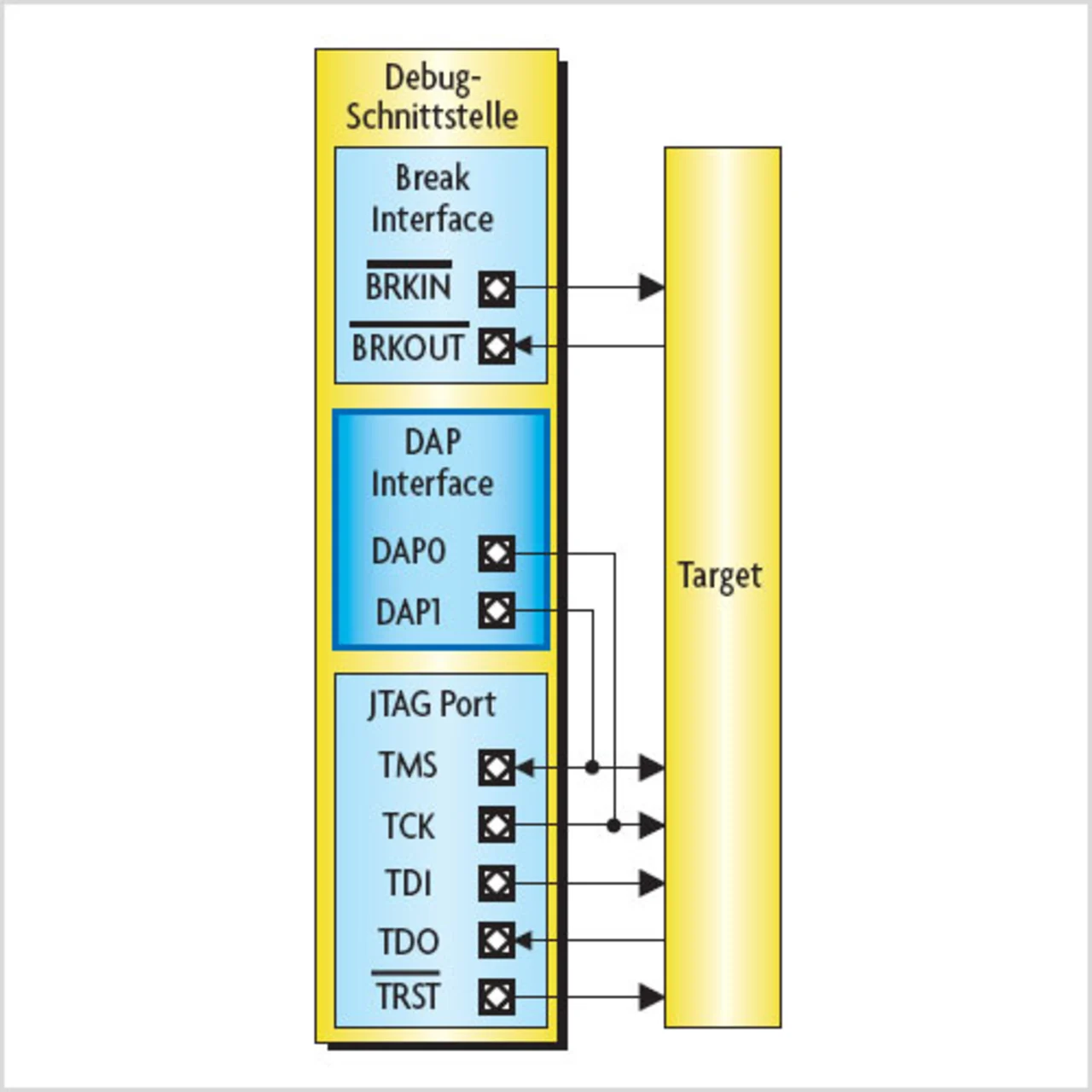

Beim Device Access Port, der von Infineon inzwischen in allen Mikrocontroller-Neuentwicklungen der XC2000/XE166-, TriCoreund XC800-Familien Verwendung findet, wurde die Anzahl der für die Übertragung des Debug-Protokolls erforderlichen Leitungen standardmäßig gegenüber JTAG von fünf auf zwei reduziert. Es handelt sich dabei um eine Taktleitung (DAP0) sowie um eine bidirektionale Signalleitung (DAP1). Die Implementierung erfolgt dabei parallel zum ebenfalls noch vorhandenen JTAG-Interface. Dabei werden die JTAGPins TMS und TCK alternativ zwischen JTAG und DAP benutzt (Bild 2).

Die restlichen drei, nicht mehr notwendigen JTAG-Pins können von der Applikation funktional zum Beispiel als Port-Pins genutzt werden. Der Anwender bekommt auf diese Weise eine hohe Flexibilität für den Umstieg auf DAP. Für Fälle, in denen eine Hochgeschwindigkeitsübertragung über differenzielle Leitungen (LVDS) erforderlich ist, kann Infineon optional zudem auf eine 3-Pin-Variante mit einer Taktleitung (DAP0) und zwei unidirektionalen Signalleitungen (DAP1 und DAP2) zurückgreifen. Für Mikrocontroller mit sehr geringer Anzahl an Pins ist außerdem noch eine Variante mit nur einer Signalleitung (Single Pin DAP – SPD) spezifiziert, die aber nur eine verringerte Übertragungsbandbreite umfasst. Ebenso wie eine parallele Implementierung von JTAG und DAP ist auch eine Kombination von DAP und SPD auf einem Baustein möglich. Dies verschafft dem Anwender hohe Flexibilität.

- Neue Debug-Schnittstellen: weniger Leitungen, mehr Information

- Neue Debug-Schnittstellen: weniger Leitungen, mehr Information

- Neue Debug-Schnittstellen: weniger Leitungen, mehr Information

- Neue Debug-Schnittstellen: weniger Leitungen, mehr Information