Neue Debug-Schnittstellen: weniger Leitungen, mehr Information

Fortsetzung des Artikels von Teil 3

Neue Debug-Schnittstellen: weniger Leitungen, mehr Information

compact JTAG

Der neue herstellerunabhänige Standard IEEE 1149.7 (compact JTAG oder cJTAG) ist entwickelt worden, um aktuellen und zukünftigen Anforderungen im Bereich des Board-/ System-Tests gerecht zu werden. Unter Beibehaltung der vollen Abwärtskompatibilität zum bisherigen IEEE-1149.1-Standard ist eine ganze Reihe neuer Eigenschaften hinzugekommen: Power-Management, Applikations-Debugging und die Geräte-Programmierung.

Jobangebote+ passend zum Thema

Insgesamt sind sechs Klassen definiert, welche durch IEEE-1149.7-kompatible TAP-Controller (TAP.7) implementiert werden können [1]:

- Klasse 0 definiert die Aufrechterhaltung der 1149.1-Kompatibilität,

- Klasse 1 führt ein zusätzliches Kommando-Protokoll für Reset- und Power-Management ein,

- Klasse 2 sieht einen Bypass vor für chip-interne TAPs zur Optimierung der Schiebekette,

- Klasse 3 definiert die Möglichkeit der Sternkopplung mehrerer TAP.7-Controller,

- Klasse 4 stellt neue Scan-Protokolle auf der Basis von nur zwei Signalleitungen zur Verfügung,

- Klasse 5 erlaubt die Verwendung von bis zu zwei applikationsspezifischen Datenleitungen, zum Beispiel für Echtzeit-Trace.

Für eingebettete Anwendungen, bei denen es in erster Linie auf Kosten und Performance ankommt, sind vor allem die Klassen 4 und 5 interessant. Hier sind nur zwei Pins zur Kommunikation notwendig und der Datendurchsatz wird durch mehrere optimierte Scan-Protokolle wesentlich erhöht. Der IEEE-1149.7-Standard ist noch neu und entsprechende Implementierungen sind rar. Ein vollständig synthetisierbarer IP-Core für cJTAG steht nach Erkenntnis des Autors bislang nur bei IPextreme zur Verfügung. Verschiedene andere Gremien, die sich ebenfalls mit Debug-Schnittstellen beschäftigen, unter anderem Nexus und MIPI, werden den cJTAG-Standard wohl aber berücksichtigen [2, 3, 4].

Unterschiedliche Ansätze erfordern modulare Test- und Debug-Tools

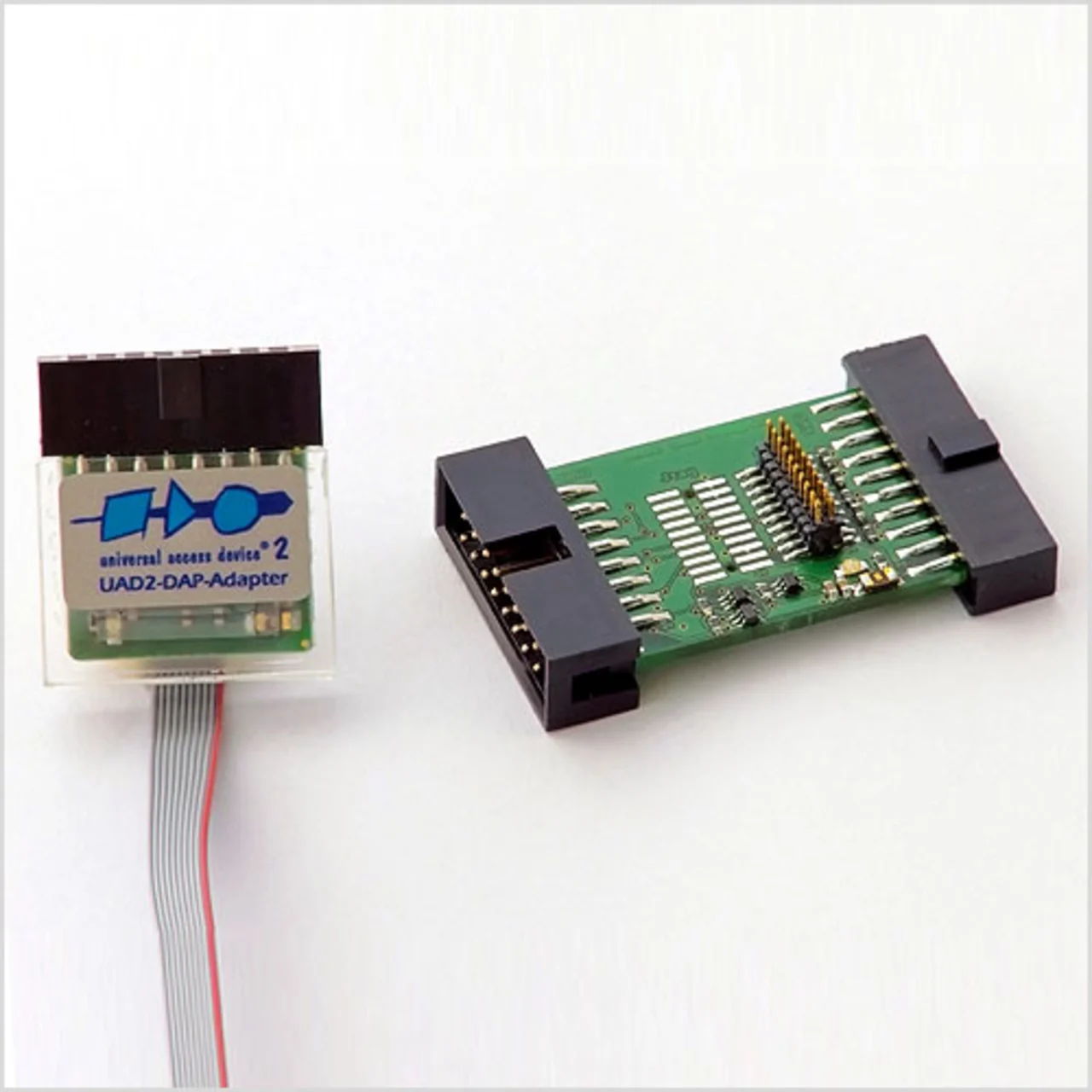

Dass der fast 20 Jahre alte JTAG-Standard heutigen Anforderungen an Geschwindigkeit, Pin-Anzahl und Robustheit nur noch bedingt gerecht wird, darüber sind sich die meisten Mikrocontroller-Anwender inzwischen wohl einig. Bleibt also die Frage nach der idealen Zukunftslösung. Wie die beschriebenen Beispiele zeigen, folgen unterschiedliche Hersteller und Interessengruppen auf der Suche nach der Antwort zwar ähnlichen Grundprinzipien, von einer echten Standardisierung kann allerdings keine Rede sein. Für Debugging- und Testwerkzeuge besteht die Herausforderung deshalb in der Unterstützung aller neuen Schnittstellen. Voraussetzung für solche universell einsetzbaren und gleichzeitig wirtschaftlich vertretbaren Lösungen ist aber neben einem modularen Adapterkonzept für die verschiedenen Steckverbinder (Bild 4) auch eine flexible Tool-Architektur. So lassen sich mit speziellen, mit einem FPGA ausgestatteten Debug-Geräten wie dem Universal Access Device 2 (UAD2) von pls schon heute nahezu alle beliebigen Debug-Protokolle ohne großen zusätzlichen Aufwand realisieren. Wer eine schnelle und flexible Unterstützung neuer Debug-Lösungen erwartet, wird wohl über kurz oder lang auch nicht auf Debug-Werkzeuge mit hoher Modularität verzichten können. jk

Literatur

[1] An Introduction to IEEE P1149.7. Texas Instruments, Southwest Design for Test Conference (SWDFT), Austin, Texas, April 2009.

[2] Offizielle Website von IEEE 1149.7: http://grouper.ieee.org/groups/1149/7/

[3] cJTAG Controller von IPextreme: html>www.ip-extreme.com/IP/cJTAG.html

[4] MIPI Test and Debug Interface Framework. White Paper, Approved Version: 3.2, MIPI Alliance, Inc., April 2006.

[5] ARM DDI 0314F, CoreSight Components Technical Reference Manual Rev. F, April 2008.

[6] ARM DDI 0337G, Cortex-M3 r2p0Technical Reference Manual Rev. G, Juni 2008.

- Neue Debug-Schnittstellen: weniger Leitungen, mehr Information

- Neue Debug-Schnittstellen: weniger Leitungen, mehr Information

- Neue Debug-Schnittstellen: weniger Leitungen, mehr Information

- Neue Debug-Schnittstellen: weniger Leitungen, mehr Information