Konfiguration komplexer On-Chip-Emulatoren

Klare Sicht auf den ARM-Core

Fortsetzung des Artikels von Teil 2

Klare Sicht auf den ARM-Core

Je nach On-Chip-Trace-Lösung lassen sich hierfür mehr oder weniger komplexe Filter- und Triggerbedingungen definieren, die entweder die Trace-Aufzeichnung starten oder stoppen. Üblicherweise sind das Adress- und Datenbereiche sowie Breakund Watchpoints. Die Auswertung der programmierten Filter- und Triggerbedingungen erfolgt dabei in Echtzeit durch die On-Chip-Trace-Hardware selbst. Die eigentlichen Core-Komponenten sind nicht involviert, sodass keine Mehrbelastung der Systemressourcen entsteht und das Laufzeitverhalten unbeeinflusst bleibt. Neben der reinen Tracedaten-Aufzeichnung besteht auch die Möglichkeit, steuernd in das Laufzeitverhalten einzugreifen. So lassen sich typische Debugfunktionen wie das Anhalten des Gesamtsystems oder das bedingte Unterbrechen der Programmabarbeitung an bestimmten Positionen oder unter bestimmten Bedingungen (Breakpoints/Watchpoints) realisieren.

Jobangebote+ passend zum Thema

Embedded Trace Macrocell (ETM)

Die »Embedded Trace Macrocell« (ETM) bzw. deren Weiterentwicklung »CoreSight« von ARM ist für verschiedene ARM-Prozessoren als IP verfügbar, wobei unterschiedliche Versionen existieren, die den jeweiligen ARM-Prozessoren zugeordnet sind. Die ETM unterstützt sowohl Programm- als auch Datentrace, CoreSight erlaubt zusätzlich das Tracen der Context-ID und ist Multicore-fähig. Zur Übertragung der gewonnenen Trace-Daten zum Debug-Host kommt ein relativ breitbandiger Trace-Port zum Einsatz, der sich in mehreren Modi mit unterschiedlichen Datenraten betreiben lässt. Vorher serialisieren FIFOBuffer die zu übertragenen Tracedaten. Im Falle von Overrun-Situationen durch Überlaufen der FIFO-Buffer bzw. zu geringer Trace-Port-Bandbreite sieht die ETMSpezifikation zwei Alternativen vor:

- Anhalten (Stall) des gesamten Systems, bis alle Tracedaten aus den FIFOs übertragen sind. Dies beeinflusst jedoch das Laufzeitverhalten des Systems, Echtzeitanforderungen an das Gesamtsystem sind unter Umständen nicht mehr erfüllbar.

- Abschalten des Datentrace, der Programmtrace bleibt hiervon unberührt. Aufgrund der viel geringeren Datenraten, die der Programmtrace benötigt, ist es möglich, FIFO-Überläufe zu verhindern. Der Verlust von Datentrace-Informationen wird im Ausgabeprotokoll gekennzeichnet.

Als Erweiterung des ETM-Konzeptes sieht ARM den »Embedded-Trace-Buffer« (ETB) vor. Dieser On-Chip-Speicher dient dazu, die Tracedaten zu speichern, welche der Debug-Host dann später, wenn die eigentliche Trace-Aufzeichnung beendet ist, über die JTAG-Schnittstelle auslesen kann. Ein dedizierter Trace-Port ist nicht mehr notwendig. Vor allem bei hohen Taktfrequenzen der Cores ist der Einsatz des ETBs sinnvoll, da in diesem Fall eine vernünftige Übertragung der Daten in Echtzeit vom Chip herunter kaum noch möglich ist.

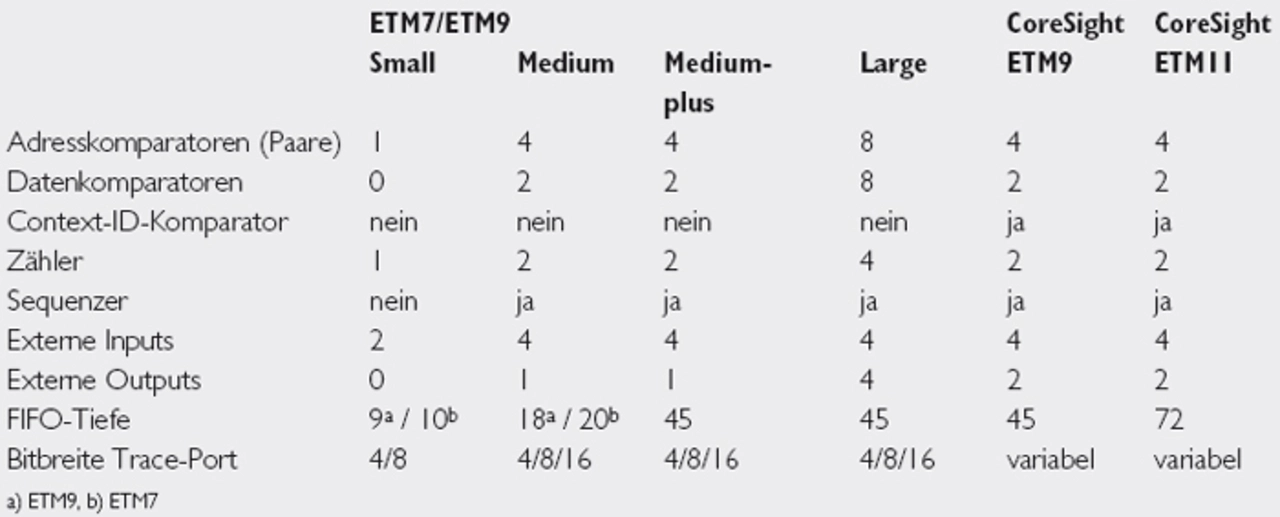

Die ETM ist in unterschiedlich komplexen Konfigurationen verfügbar (Tabelle 1). Dies spiegelt sich vor allem in der verfügbaren Filterund Triggerlogik wieder. Im Allgemeinen sieht das ETMKonzept Komparatoren für Adress-Bereiche, Daten sowie den Zugriffsmodus (Lesen oder Schreiben) vor. Speziell für den Programmtrace kann zudem definiert werden, zu welchem Zeitpunkt in der Pipelineverarbeitung (Fetch oder Execute) ein Adresskomparator auf eine passende Adresse reagiert. Durch Verknüpfung der einzelnen Komparatoren lassen sich außerdem komplexere Triggerbedingungen zur Steuerung der Trace-Aufzeichnung definieren. Mit Hilfe von Zählern und eines Sequenzers zur Realisierung einer State-Machine mit maximal drei Zuständen ist auch das sequenzielle Verhalten sehr gut rekonstruierbar. Leider ist der Sequenzer aber nicht in allen Konfigurationen verfügbar.

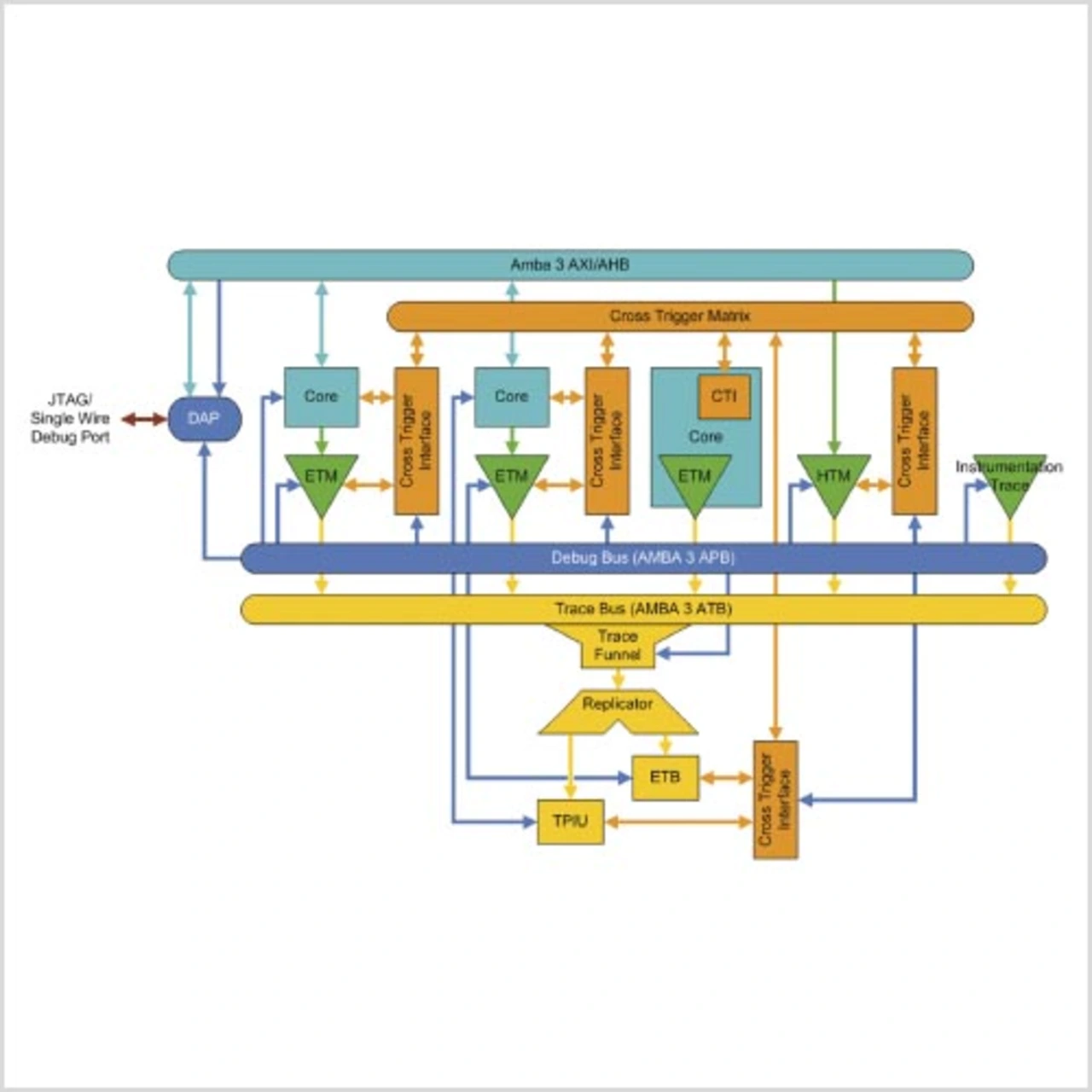

Um On-Chip-Trace zu ermöglichen, integriert der Halbleiterhersteller auf dem Die direkt neben dem eigentlichen Produktions-Chip weitere dedizierte Logik. Dabei haben die On-Chip-Trace-Einheiten der »CoreSight«-Technik direkten Zugang zu den Cores und den Systembussen des jeweiligen Mikrocontrollersystems (Bild 1). Mit dieser On-Chip-Trace-Logik ist neben dem »Programm-Trace«, also der Aufzeichnung des Programmablaufs, auch eine gleichzeitige Beobachtung der Kommunikation auf den Systembussen möglich. Damit lässt sich ein »Daten-Trace« realisieren, der neben den Hauptspeicheradressen auch die auf den Bussen übertragenen Daten selbst erfasst. Je nach Komplexität des jeweiligen On-Chip-Trace-Verfahrens können zudem auch weitere Informationen zum Laufzeitverhalten des Systems wie zum Beispiel die aktuelle Task-ID oder die jeweiligen Zugriffsmodi auf die Systembusse gesammelt werden.

- Klare Sicht auf den ARM-Core

- Klare Sicht auf den ARM-Core

- Klare Sicht auf den ARM-Core

- Klare Sicht auf den ARM-Core

- Klare Sicht auf den ARM-Core