IC-Gehäuse als Schnittstelle zwischen Leiterplatten und Halbleiterchip

Fortsetzung des Artikels von Teil 1

IC-Gehäuse als Schnittstelle zwischen Leiterplatten und Halbleiterchip

Zudem wird der Entwickler, wenn das „Die“ per Wirebond angeschlossen wird, die Netze aus Verilog den Flipchip- Bumps oder den Passivierungsöffnungen zuweisen. Die Software errechnet die Versorgungs- und Masse- Anforderungen und verbindet die ICNetze mit den definierten Versorgungs- und Masse-Pads. Mit dieser anfänglichen Zuweisung der IC-Netze werden Software-Routinen anschließend die physikalische Darstellung des „Dies“ vervollständigen und in der SiP-Layout-Umgebung aktualisieren. Die im Connectivity-Manager zugewiesenen Gehäusenetze sind in dieser Phase nun an die Verbindungspunkte der physikalischen Darstellung angehängt, und der SiP-Entwickler kann das übrige Layout des Gehäuses abschließen. Dies beinhaltet die Platzierung der übrigen „Die“-, Bypass-Kondensatoren und Terminierungen.

Vor der Initialisierung des Designs auf PCB-Ebene muss eine Gehäuse- Schnittstelle definiert werden. Dies kann auf unterschiedlichsten Wegen erfolgen: Am einfachsten geht es durch die Auswahl eines Standard-Gehäuses oder durch die Erstellung eines kundenspezifischen Gehäuses. Sobald die Platzierung im SiP erfolgt ist, können die Gehäuse-Signale des Designs automatisch den Balls zugeordnet werden. Ebenso kann der Flow den Connectivity- Manager aufrufen, der die anfänglichen IO-Zuordnungen für das PCB erstellt. Ungeachtet der Auswahl werden alle Änderungen mit Hilfe der Synchronisations-Engine in der Connectivity- Manager-Lösung aktualisiert.

Jobangebote+ passend zum Thema

Logische und physikalische SiPSymbole synchron geschaltet

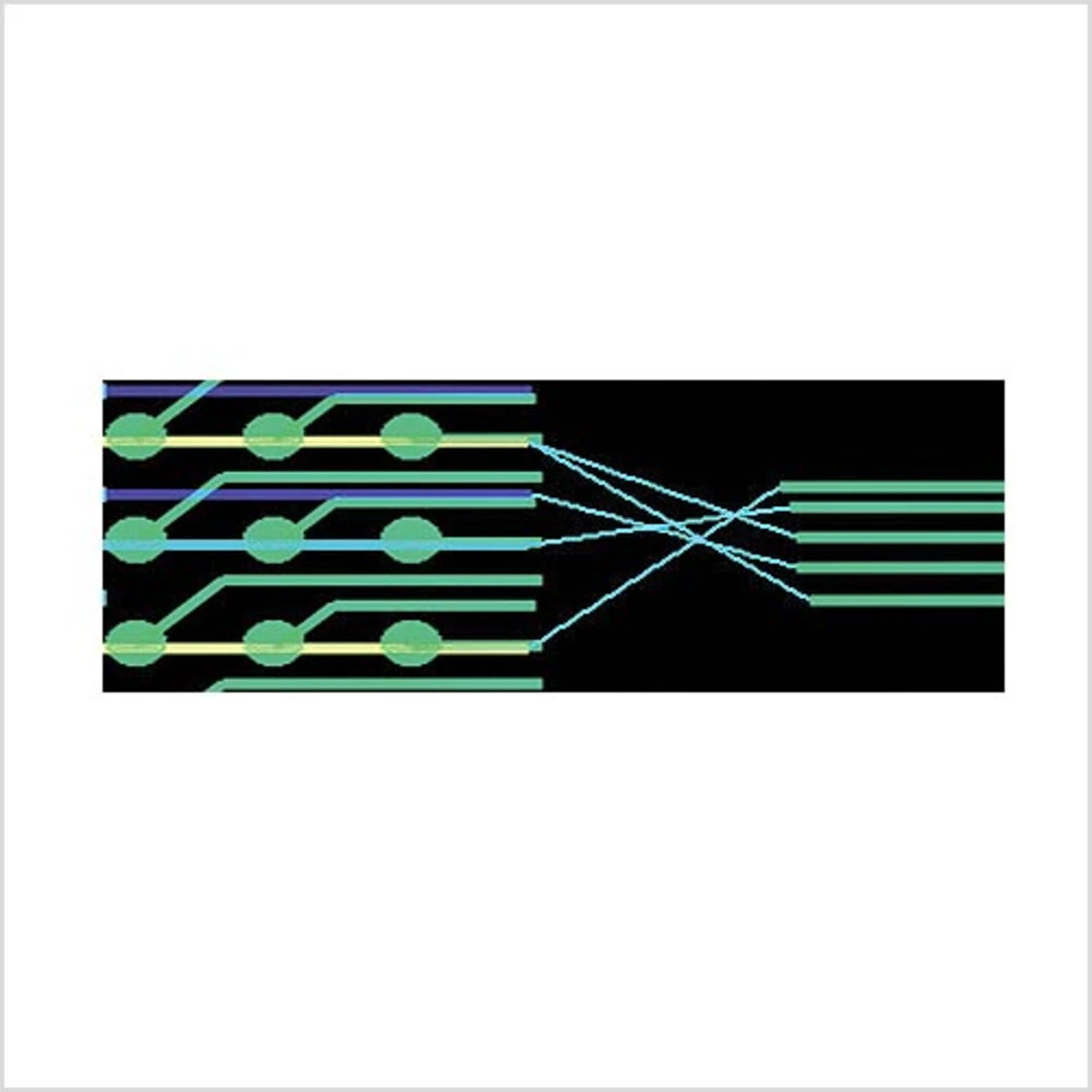

Mit Abschluss der Synchronisation sind die logischen und physikalischen SiP-Symbole jetzt synchron. Alle Zuweisungen zur neuen Gehäuse-Schnittstelle und den Pinzahlen des neu erstellten physikalischen „Die“-Objekts sind in der Kalkulationstabelle enthalten. Der PCB-Prozess wird gestartet, indem die Gehäuse-PCB-Schnittstelle an die PCB-Umgebung übergeben und automatisch ein Bauteilmodell erstellt wird. Dieses ist dann in der logischen PCB-Designphase verwendbar. Die PCB-Konnektivität wird durch die Verbindung der PCB-Signale mit dem neu geschaffenen Bauteilmodell hergestellt. Sobald ausreichende PCBKonnektivität verfügbar ist, wird der Entwickler die physikalische PCB-Design- Umgebung mittels einer logischen PCB-Netzliste initialisieren. Beim PCB-Layout wird er dann die kritischen Komponenten platzieren, einschließlich der anfänglichen physikalischen Gehäusemodelle. Sobald der Verlauf der Signale grob festgelegt ist, werden mögliche Ineffizienzen in der Ball-Zuweisung deutlich (Bild 3a).

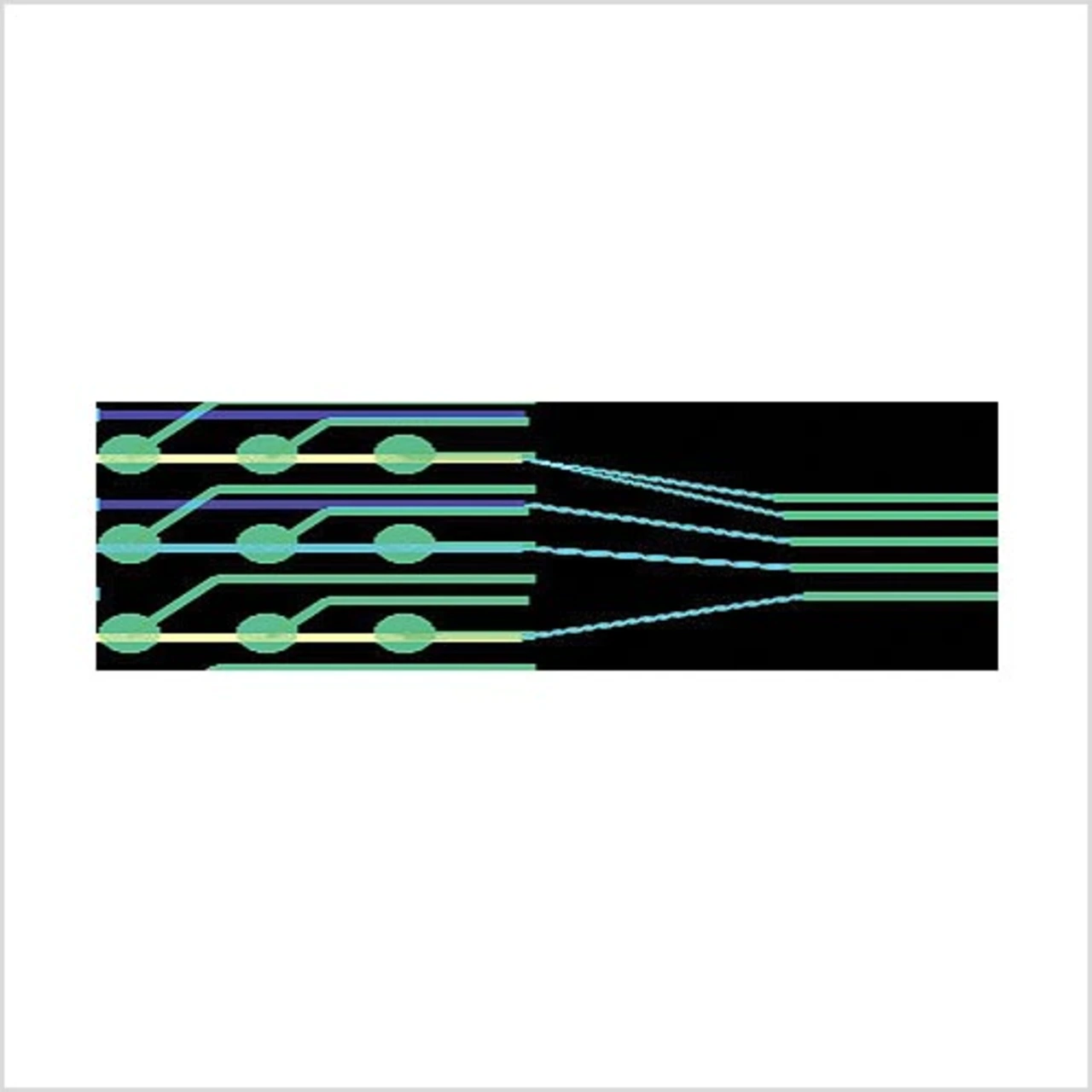

Für die Kopplung mit dem PCB nutzt der Layout-Entwickler jetzt Austauschbefehle, um die Zuweisung zu optimieren (Bild 3b). Sobald alle vom PCB-Layout-Ingenieur geforderten Zuweisungen erstellt wurden, wird mit Hilfe des physikalischen Designs und der Synchronisations-Engine das logische PCB-Design aktualisiert. Dieser Schritt ist entscheidend im Prozess, da die empfohlenen Änderungen zurück zum Gehäuse und möglicherweise zum IC-Design übergeben werden müssen. Alle Änderungen, die für die Optimierung des physikalischen Gehäuses im Zusammenhang mit der Baugruppe erforderlich waren, sind jetzt auch in der logischen PCB-Umgebung sichtbar. Die Signale im PCB sind jetzt mit den einzelnen Balls des Gehäusemodells verbunden. Die Aktualisierung des Gehäuse-Designs erfolgt, indem die optimierte Schnittstelle zum SiPConnectivity- Manager exportiert wird. Dieser importiert die Updates von der logischen PCB-Design-Umgebung und synchronisiert sie mit dem bestehenden SiP-Design. Dieser Schritt aktualisiert die bestehende Gehäuse-Schnittstelle, wobei alle internen Verbindungen erhalten bleiben. Der Entwickler wird nun eine physikalische Netzliste erstellen und zur Aktualisierung der physikalischen Gehäusedatenbank verwenden.

Der Layout-Entwickler muss in dieser Designphase nun entscheiden, ob die eine oder andere PCB-Anfrage zurückgewiesen, die eine oder andere Schnittstellen- Änderung im Gehäuse-Routing berücksichtigt oder die eine oder andere Änderung ins IC-Design verlagert werden soll. Je nach Umfang der erforderlichen Änderung kann der Designer den einen oder anderen Austausch ablehnen. Änderungen, die eine Verlagerung von Hard-Makros verursachen, sind in dieser Phase des Designs nicht akzeptabel. Von der IO-Planungsumgebung nicht akzeptierte Änderungen werden dann im SiP-Layout aktualisiert und gehen zurück zum SiP-Layout- Entwickler. Dieser entscheidet, ob dies im Gehäuse oder auf dem PCB implementiert werden soll.

Sobald diese Schritte abgeschlossen sind, befinden sich die IC-, Gehäuseund PCB-Umgebungen im gemeinsamen Co-Design-Modus. Die Synchronisation erfolgt durch das Einhalten der standardmäßigen Schnittstellen- Schritte. Dieser iterative Prozess lässt die Eingabe von Änderungen aus jeder der drei Design-Umgebungen zu. Design- Änderungen (ECOs) können damit an jedem Punkt im Prozess angestoßen werden.

Steve Durrill (sdurrill@cadence.com) / Keith Felton (keithfel@cadence) /go

- IC-Gehäuse als Schnittstelle zwischen Leiterplatten und Halbleiterchip

- IC-Gehäuse als Schnittstelle zwischen Leiterplatten und Halbleiterchip