Leiterplattenentwurf

Board-Designs auf Signal-Integrität überprüfen

Fortsetzung des Artikels von Teil 1

Signal-Integrität beginnt vor der Simulation

Immer mehr Standards verlagern die Verantwortung für das Funktionieren entsprechender Halbleiterbausteine auf den Entflechter. Den Vorgaben des entsprechenden Datenblattes sollte hier unbedingt Genüge getan werden, denn sonst nutzt das beste Simulations-Tool nichts. Wenn man z.B. einen DDR-Speicher verwendet, ist zwingend vorausgesetzt, dass die Leiterbahnlängen von Daten und Takt einen Längenabgleich erfahren. Demnach sollen hier einige mögliche Szenarien diskutiert werden:

- Längenabgleich für einfache Leiterbahnen in Busstrukturen (z.B. DDR3-Speicher)

- Längenabgleich für differentielle Leiterbahnen (z.B. Gbit-Ethernet)

- Impedanz-getriebene Leiterbahnen (z.B. 50 Ω)

- Zwei Speicherbänke an einem Treiberbaustein (Stubbed T-Nets)

- Widerstände zur Dämpfung in Leiterbahnen, die abgeglichen werden müssen

In die interaktive Entflechtung von Leiterbahnen mit Hilfe von Altium Designer ist die Möglichkeit integriert, einen Längenabgleich von einfachen und differentiellen Leiterbahnen durchzuführen. Nach dem Entflechten wird den betroffenen Netzen in der Regel eine Toleranz zugewiesen, die dann später von dem Längenabgleich benutzt wird. Der Längenabgleich fügt dann bis zur entsprechenden Ziellänge Schlangenlinien nach den Vorgaben hinzu.

Die Impedanz einer Leiterbahn bestimmt sich größtenteils aus der Leiterbahnbreite in Relation zum verwendeten Lagenaufbau. In Altium Designer wird einfach für die entsprechenden Leiterbahnen eine Regel definiert, welche die Leiterbahndicke aus den gegebenen Daten der vereinheitlichten Datenbank inklusive Lagenaufbau errechnet.

Bei so genannten Stubbed T-Nets ist der Längenabgleich zunächst nicht ganz so einfach: Hier müssen sowohl die Ableitungen der Treiber als auch die Zuleitungen der Empfänger in der Länge abgeglichen werden. Wenn man dieselben Bausteine als Empfänger verwendet, sind in der Regel die beiden Zuleitungen gleich lang. Bei unterschiedlichen Eingangskapazitäten wird ein Laufzeitunterschied über unterschiedliche Längen erfolgen, der zuvor simuliert werden sollte. Das generelle Problem dieses Ansatzes ist die Segmentierung des Netzes. Da man aus einem Netz drei Segmente machen will und jedem Segment jeweils einen Netznamen zuweist, wird das Tool einen Fehler melden. Man hat schließlich einen Kurzschluss produziert.

Abhilfe schafft hier das Konzept der „Net Ties“, das auch bei der physikalischen Verbindung von digitaler und analoger Masse sehr hilfreich ist. Der Entwickler definiert im Bibliotheks-Editor einen beliebig aussehenden Baustein und weist diesem in den entsprechenden Properties den Typ „Net Tie“ zu. Man kann hierbei definieren, ob dieser Baustein in der Stückliste erscheinen soll oder nicht. Mit dieser Methode tritt keine Regelverletzung auf, und die einzelnen Segmente können in der Länge abgeglichen werden.

Jobangebote+ passend zum Thema

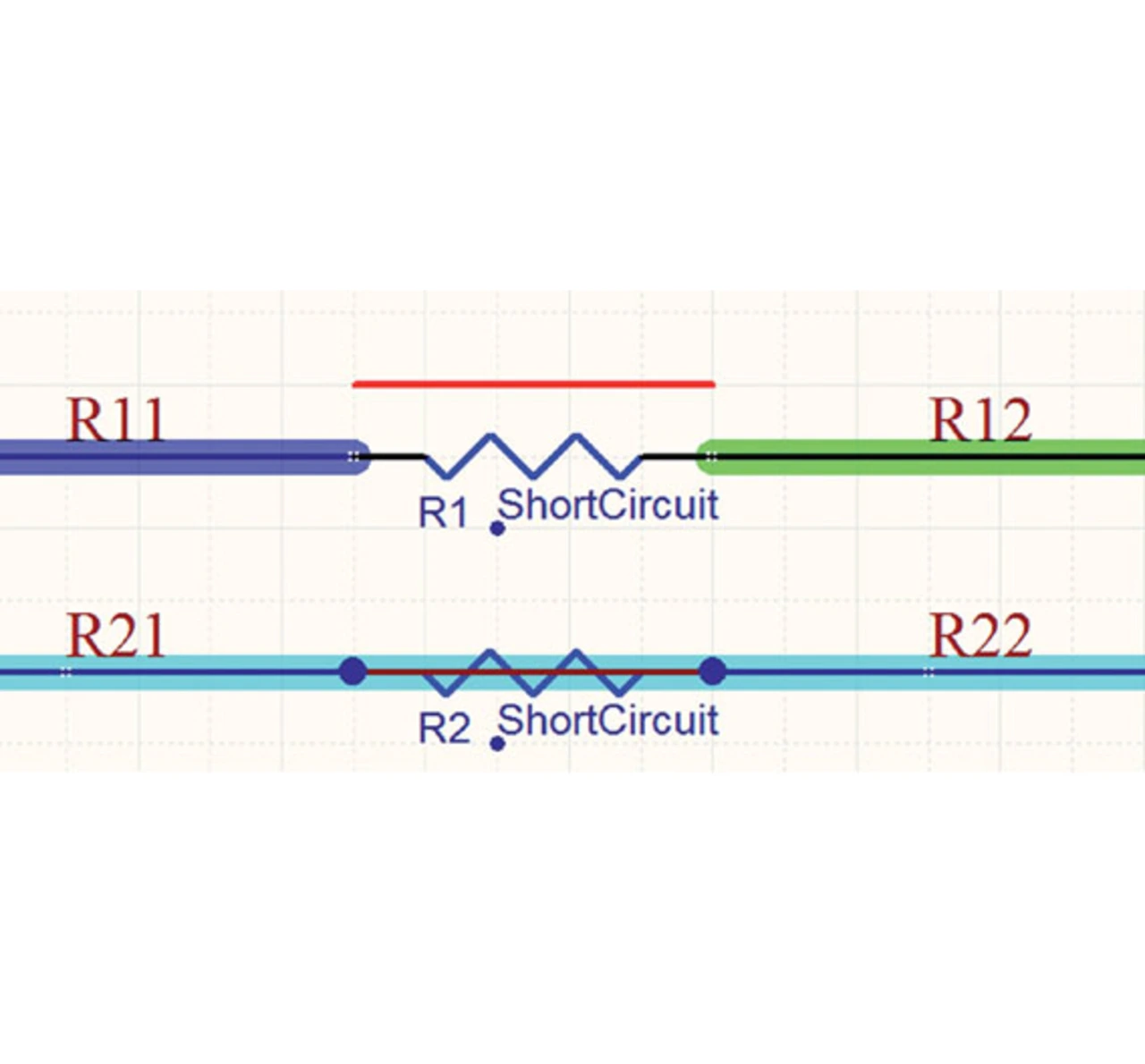

Der umgekehrte Fall tritt ein, wenn in den verwendeten Zuleitungen ein Widerstand entflochten worden ist. In diesem Fall hat man vor und nach dem Widerstand je ein Netz, was einen Längenabgleich deutlich erschwert. Abhilfe liefert ein kleiner Trick: Man überbrückt einfach kurzfristig im Schaltplan den verwendeten Widerstand, so wie in Bild 3 gezeigt.

Es ist empfehlenswert, diesen Track farblich zu markieren. So können diese über die Selektion nach Farben im „Find Similiar“-Menü später gelöscht werden. Wie Bild 3 bei farblicher Kennzeichnung der Netze zu entnehmen ist, hat der Kurzschluss zur Folge, dass physikalisch nur ein Netz vorhanden ist und demnach der Längenabgleich nur eine Formalität ist. Auf dem PCB platziert man nun seinen 0402-Widerstand - wie gewünscht - und legt die Leiterbahn über beide Anschlüsse. Nach dem anschließenden Längenabgleich ermittelt man mit dem Simulator einen geeigneten Widerstandswert. Die Segmente zwischen den Anschlüssen können selektiert und gelöscht werden. Im Schaltplan werden die Kurzschlüsse entfernt und der ermittelte Wert in den Widerstand eingetragen. Nach abschließendem Abgleich mit dem PCB-Design sind wieder zwei Netze vorhanden.

Weiterhin sollte erwähnt werden, dass es noch einige gute Möglichkeiten gibt, sein Board auf „High Speed“ zu trimmen. So können beispielsweise der Via-Lagenaufbau individuell bestimmt, die Leiterbahnen in Bögen entflochten (auch bei Bussen) sowie die Pads mit sogenannten Teardrops versehen werden.

Der Autor:

| Jörg Kaleita |

|---|

| studierte Fernsehtechnik an der Fachhochschule für Angewandte Wissenschaften in Wiesbaden und arbeitete anschließend als Hardware- und Software-Entwickler in der Industrie. Unter anderem war er als Field Application Engineer bei einem Hersteller für Programmierbare Logikbausteine tätig und wechselte 2008 zu seinem aktuellen Arbeitgeber, die Altium Europe GmbH, für die er als Technical Account Manager EMEA im Einsatz ist. |

joerg.kaleita@altium.com

- Board-Designs auf Signal-Integrität überprüfen

- Signal-Integrität beginnt vor der Simulation