Notbremse für das Auto

Fortsetzung des Artikels von Teil 1

Redundanz durch Verdopplung

Gegenwärtiger Stand der Technik zur Überwachung der CPU ist der „Dual-Core Lock-Step“-Ansatz, das heißt, die Überwachung durch doppelte CPU mit Hardware-Vergleicher. Dabei werden die Eingangssignale auf beide CPUs geführt, aber nur eine CPU ist ausgangsseitig aktiv. Die Ergebnisse der beiden CPUs werden auf Gleichheit getestet; im Falle einer Divergenz geht das System in den sicheren Zustand über. Diese Architektur wird oft durch Selbsttests (Built-In Self Test, BIST) ergänzt, welche die einzelnen Blöcke der CPU überprüfen.

Dieses hochwertige Überwachungsverfahren ist mit verhältnismäßig kleinen, wenig komplexen Produkten wie einem ARM7TDMI-Prozessor einfach zu realisieren. Wenn jedoch der Bedarf an Rechenleistung einen leistungsfähigen Prozessorkern wie zum Beispiel einen ARM1156T2-S verlangt, wächst der Mehraufwand sehr schnell über alle Schranken. Dies liegt nicht nur an der Siliziumfläche für den Prozessorkern, sondern auch am Speichersystem und der Busstruktur. Leistungsfähigere Prozessorkerne weisen in der Regel ein hierarchisches Speichersystem mit Cache-Speicher und mehrfachen Bussen auf. Jeder Eingriff in den optimierten Datenpfad wirkt sich negativ auf die Rechenleistung aus, die mehrfachen Busse erschweren das Platzieren der Verbindungsleitungen (Routing), und die Duplizierung des lokalen Cache-Speichers erhöht ebenfalls die benötige Chipfläche. Zusätzlich ist zu bedenken, dass ein klassischer „Dual-Core Lock-Step“ nur die Fehlererkennung ermöglicht, jedoch noch keine Redundanz aufweist, da die beiden Prozessorkerne nicht voneinander unabhängig sind und nur einen Ausführungskanal darstellen.

Dies ist für „Fail Silent“-Systeme, die entweder ganz oder gar nicht funktionieren – wie z.B. Systeme, bei denen die Elektronik die Mechanik ergänzt – vollkommen ausreichend. Erfordert das System eine „Fail Functional“-Architektur, d.h., das System muss auch nach x Fehlern funktionieren (in der Automobiltechnik ist normalerweise x = 1, ein Fehler darf also nicht zum Systemausfall führen), dann sind zwei Ausführungskanäle vorzusehen. Rekonfigurierbare Zweikanal-Chips sind bereits in der Literatur vorgeschlagen worden. Diese waren mit zwei „Dual-Core Lock-Step“-Einheiten aufgebaut und würden so die vierfache Fläche in Anspruch nehmen.

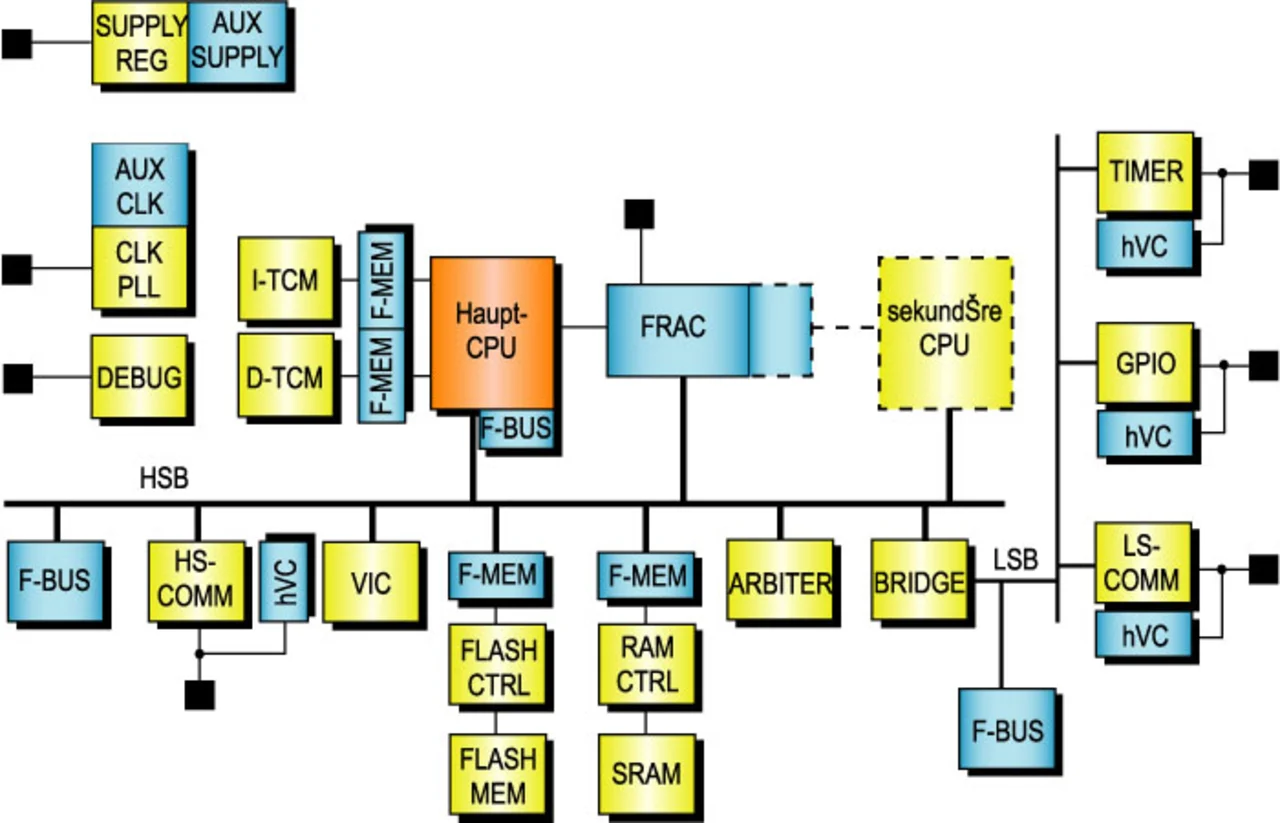

Da die zweite CPU aber ausschließlich zur Überwachung eingesetzt wird, kann sie durch einen spezifischen Diagnosekanal ersetzt werden. Die IEC-61508-Norm bietet hierzu Richtlinien zur Implementierung. Voraussetzung hierfür ist eine Fehlermöglichkeiten-Einflussanalyse (FMEA, Failure Mode and Effects Analysis), welche die Ausfallmechanismen von Halbleitern berücksichtigt und deren Auswirkung auf die verschiedenen Funktionsblöcke der CPU liefert. Die FMEA liefert also die Grundinformation für die Optimierung und Anpassung des Diagnosekanals in Form eines „Fault Recognition Acceleration Coprocessors“ an die CPU (Bild 2). Der „Fault Recognition Acceleration Coprocessor“ ist an die CPU und deren Busse gekoppelt und deckt mögliche Fehler in der CPU über deren Auswirkung an den Schnittstellen auf. Hierzu werden komplementäre Methoden eingesetzt, wie Register Shadowing, State Checker, ALU Checker, Kontrollflussgraph, Signaturüberprüfung etc.

Dieser Coprozessor wird unterstützt und ergänzt durch Selbsttests, die er selbst initiieren kann. „Memory Scrubbing“-Techniken – in regelmäßigen Abständen wird der gesamte Speicherinhalt ausgelesen und neu geschrieben, um zu vermeiden, dass sich korrigierbare Ein-Bit-Fehler zu nicht korrigierbaren Multi-Bit-Fehlern auswachsen –, redundante Busse sowie Protokoll- und Funktionschecker für Peripheriemodule, so genannte Hardware Verification Components, erweitern die Diagnose über die CPU hinaus auf den gesamten Chip.

Durch den Einsatz dieser komplementären Techniken wird der Diagnosedeckungsgrad von 99 % erreicht, welcher für SIL3-Systeme (Safety Integrity Level nach IEC 61508) erforderlich ist, und gleichzeitig die Fläche im Vergleich zu einer zweiten CPU minimiert. Eine solche einkanalige Struktur mit ständiger Überwachung ist der grundlegende Baustein zur Realisierung beliebiger MooND-Strukturen (M out of N channel architecture with Diagnostics) höherer Hardware-Fehlertoleranz – d.h., mehrkanalige Architekturen, bei denen M funktionsfähige von insgesamt N Kanälen in der Lage sind, die Sicherheit zu gewährleisten. Zwei solcher Strukturen würden z.B. eine 1oo2D-Architektur ergeben, mit der man die in der Automobilelektronik von TÜV und FAKRA (Normenaussschuss Kraftfahrzeuge des VDA) geforderte SIL3-Struktur mit Hardwarefehlertoleranz (HFT) von 1 implementieren kann. ARM untersucht zur Zeit die Machbarkeit solcher Architekturen zusammen mit dem Partner YogiTech [2] aus Pisa.

| Boris Vittorelli ist seit Januar 2001 als European Automotive Manager bei ARM für die Spezifikation neuer Produkte und Produkteigenschaften für Cores, Peripheriemodule und Entwicklungstools zuständig. Vorher arbeitete er drei Jahre lang als Systemarchitekt bei Infineon Technologies mit Schwerpunkt TriCore-Anwendungen in Powertrain und X-by-Wire. Nach dem Studium der Nachrichtentechnik an der Rheinisch-Westfälischen Technischen Hochschule in Aachen, Schwerpunkt digitale Signalverarbeitung, begann er 1994 seine Laufbahn bei Texas Instruments, Paris, und gründete dort die DSP Support Hotline für Europa. Nach drei Jahren wechselte er nach Freising, wo er mit Schwerpunkt Signalverarbeitung und X-by-Wire-Systeme arbeitete. E-Mail: boris.vittorelli@arm.com |

- Notbremse für das Auto

- Redundanz durch Verdopplung