Sicherer Halt inklusive

Fortsetzung des Artikels von Teil 2

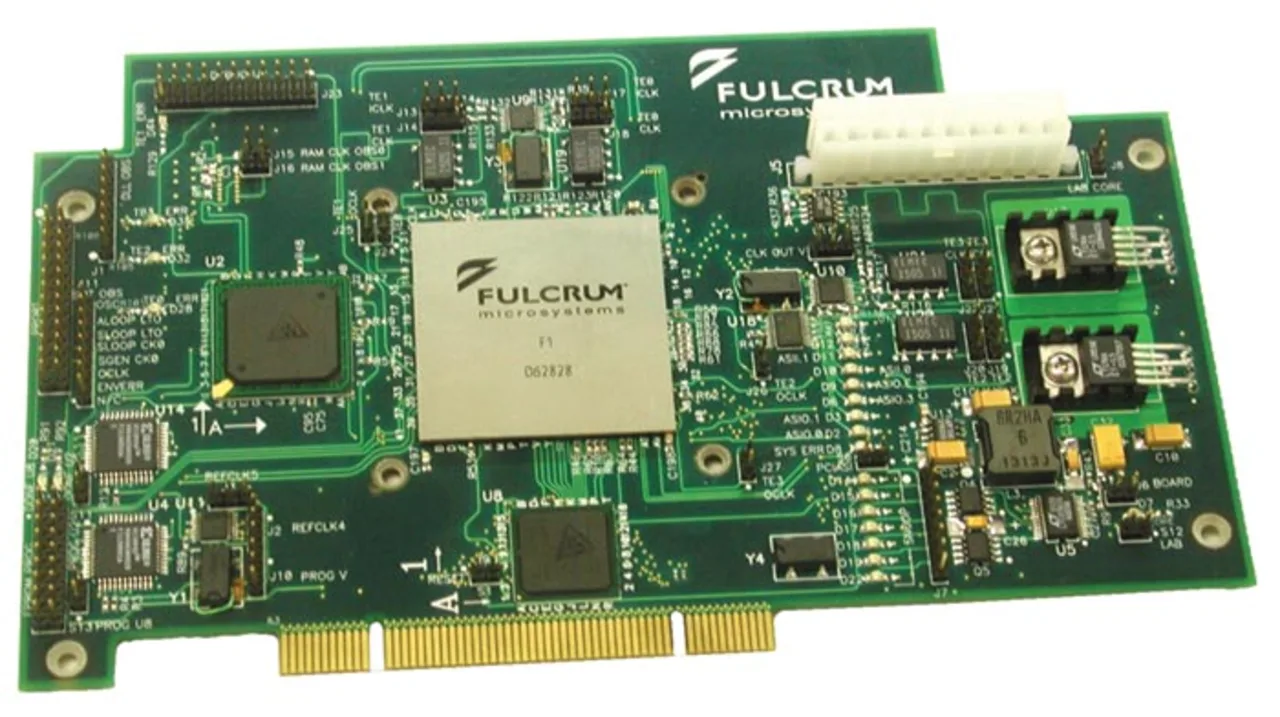

Das F1-Testboard

Bei den hohen Datenraten bei Taktfrequenzen von 450 MHz liefert das F1-Board (Bild 4) die einfache Möglichkeit, das Verhalten des F1-Chips oder auch die Interkommunikation mehrerer F1-ICs im System zu testen. Als PCI-Board ausgelegt, passt es in jeden PC.

Die Komponenten auf der Platine sind zum größten Teil programmierbar, um kundenspezifische Anpassungen zu ermöglichen:

- drei unabhängig programmierbare Taktchips,

- programmierbare Spannungsversorgung zum Test des Chips bei unterschiedlichen Kern-Betriebsspannungen zwischen 0,9 und 2 V,

- FPGA, vorprogrammiert als PCI-Interface und für Debug-Zwecke,

- FPGA, vorprogrammiert mit vier Test-Funktionen.

- Jede Testfunktion verwendet 24 Daten-Bits und 12 Parity-Bits.

- Jede der vier Test-Funktionen ist über 25 Kommandos programmierbar.

Auf diese Weise lassen sich schnell Teststrukturen aufbauen, um zum einen mit echten Daten und zusätzlich mit simulierten Testdaten schnelle und wiederholbare Datenflüsse bei hohen Datenraten zu erzeugen.

Datenflusstechnik im Kreuzschienenverteiler Nexus

Ein synchroner Datentransfer ist durch die Problematik der Synchronisation aller beteiligten Signalflüsse hier nicht einsetzbar. Fulcrum setzt bei Nexus eine patentierte, verzögerungsunabhängige Technik mit einem 4-Phasen-Übertragungsschema ein, die schnelle dynamische Logik verwendet, um eine quasi-parallele Verbindung der 16 Ports über einen extrem schnellen asynchronen Datenbus zu erreichen. On-Chip-Arbiter sorgen dafür, dass der Zugriff nicht blockierend ist.

Das Bild einer Reihe von Dominosteinen ist sehr anschaulich, denn es zeigt, wie sich die einzelnen Daten-Bits voranbewegen. Da es keinen übergeordneten Takt gibt, „fallen“ die einzelnen Bits wie Dominosteine in vielen Bitreihen unabhängig voneinander und mit maximaler Geschwindigkeit der eingesetzten Halbleitertechnologie, ohne dass durch eine übergeordnete Synchronisierung Zeit verloren geht.

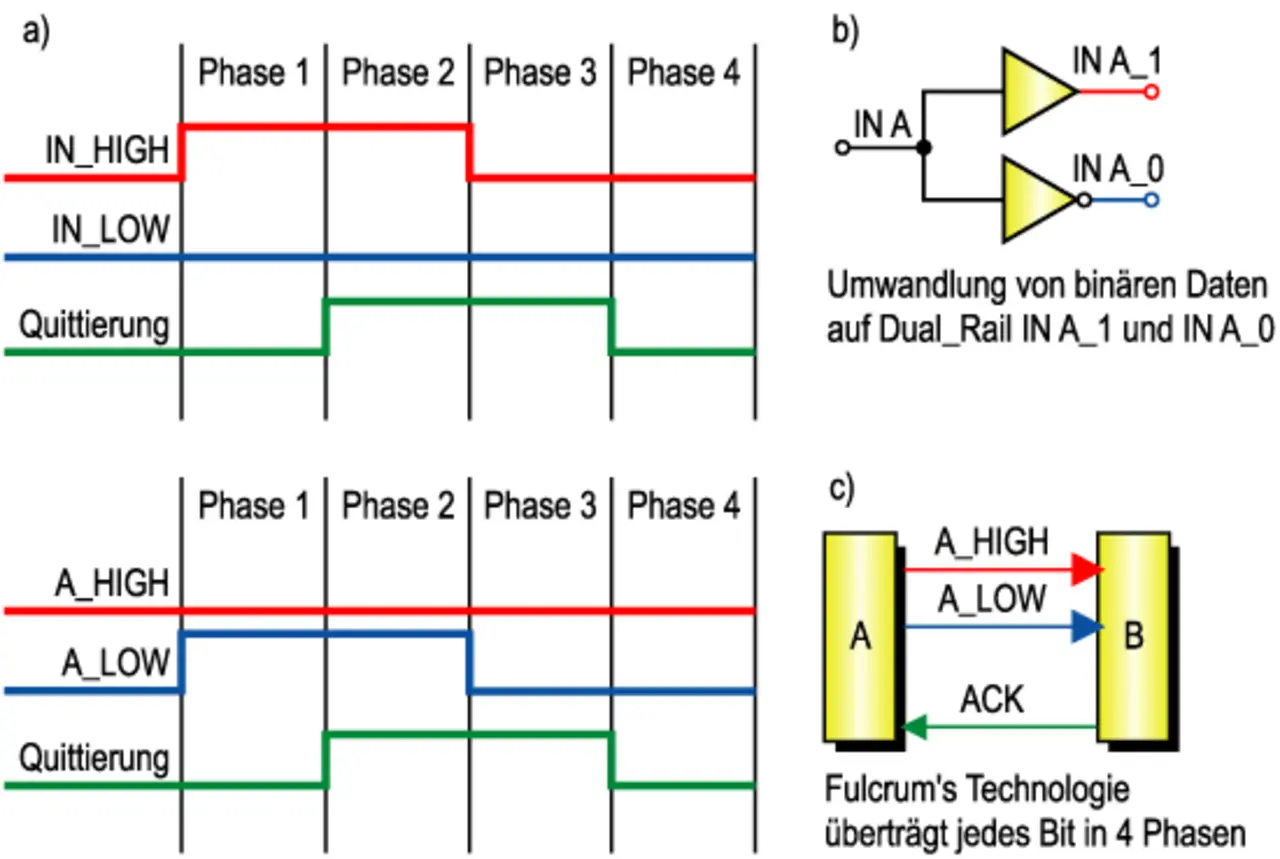

Da sich alle Domino-Bits per Definition unabhängig voneinander voranbewegen, kann hier nicht wie in der binären Logik mit HIGH und LOW zur Definition der Daten gearbeitet werden. Es muss sowohl für LOW wie für HIGH ein aktiver Level definiert werden. Da dies zusammen mit dem Wert „Null“ für inaktiv eine „dreiwertige“ Halbleitertechnologie erfordern würde, wird HIGH und LOW jeweils eine separate Leitung zugeteilt, indes ergibt sich die so genannte Dual-Rail-Implementierung (Bild 5).

Das Durchschalten eines jeden Bits wird in vier Phasen ausgeführt (Bild 5a):

- Der Sender schaltet entweder das Signal HIGH oder LOW von Null auf aktiv um. Es führt also immer nur eine von beiden Leitungen positives Potential, beide Signale positiv ist ein nicht erlaubter Zustand.

- Der empfangende Teil „erkennt“ das Signal und meldet dies über das Quittierungssignal an den Sender zurück, fängt aber sofort mit der Bearbeitung an.

- Der Sender schaltet bei Empfang des Quittierungssignales das jeweils aktive Signal wieder auf Null zurück.

- Der Empfänger nimmt das Quittierungssignal zurück. Damit ist der Ruhezustand erreicht.

Wichtig an dieser Kommunikationsart ist die Tatsache, dass der Empfänger sofort nach dem Empfang von Daten mit der Bearbeitung beginnen kann und auch eine Weitergabe an den nächsten Block möglich ist, unabhängig von der parallel stattfindenden Quittierung.

Man kann sich also gut vorstellen, wie sich die Datenbits vollkommen unabhängig von jeglichem Takt mit maximaler Geschwindigkeit der jeweiligen Halbleitertechnologie auf dem Chip vorwärtsbewegen. Die parallel stattfindende Quittierungsaktivität sorgt wie ein Abstandshalter dafür, dass nach einer Aktivität eine kurze Ruhepause folgt.

Durch die Implementierung des Nexus-Blocks in asynchroner Technologie ist eine quasi-gleichzeitige Übertragung für mehrere parallele Datenflüsse erreicht. Solange der Datenverkehr unterhalb des maximalen Durchsatzes bleibt, scheint Nexus 16 bidirektionale Datenkanäle gleichzeitig und voneinander unabhängig zu verbinden.

| Dipl.-Ing. Jürgen Pintaske studierte Nachrichtentechnik in Aachen und arbeitete dann als Entwicklungsingenieur bei Horstmann in Heiligenhaus im Bereich Analog- und Prozessorsysteme. Daran schlossen sich fünf Jahre Applikationsingenieur bei RCA/Harris an. Es folgten Marketingmanager-Funktionen bei Hitachi und Tekelec sowie Vertrieb bei Hughes Microelectronics und Mixed Mode in München. Seit 1998 in Exeter/England lebend, unterstützt er nach seiner Funktion als Director Germany bei Marketbroad jetzt bei ExMark amerikanische und europäische Kunden in PR, Marketing und Sales. E-Mail: exmarkjpi@aol.com |

- Sicherer Halt inklusive

- Der „Nexus“-Block

- Das F1-Testboard