Microcontroller

Ansteuerung von TFTs leichtgemacht

Fortsetzung des Artikels von Teil 2

ARMs Cortex-A9 – nicht nur schneller als Cortex-M

Bus-Master am South-Bus können auf keine Adressen, die dem North-Bus zugewiesen sind, zugreifen.

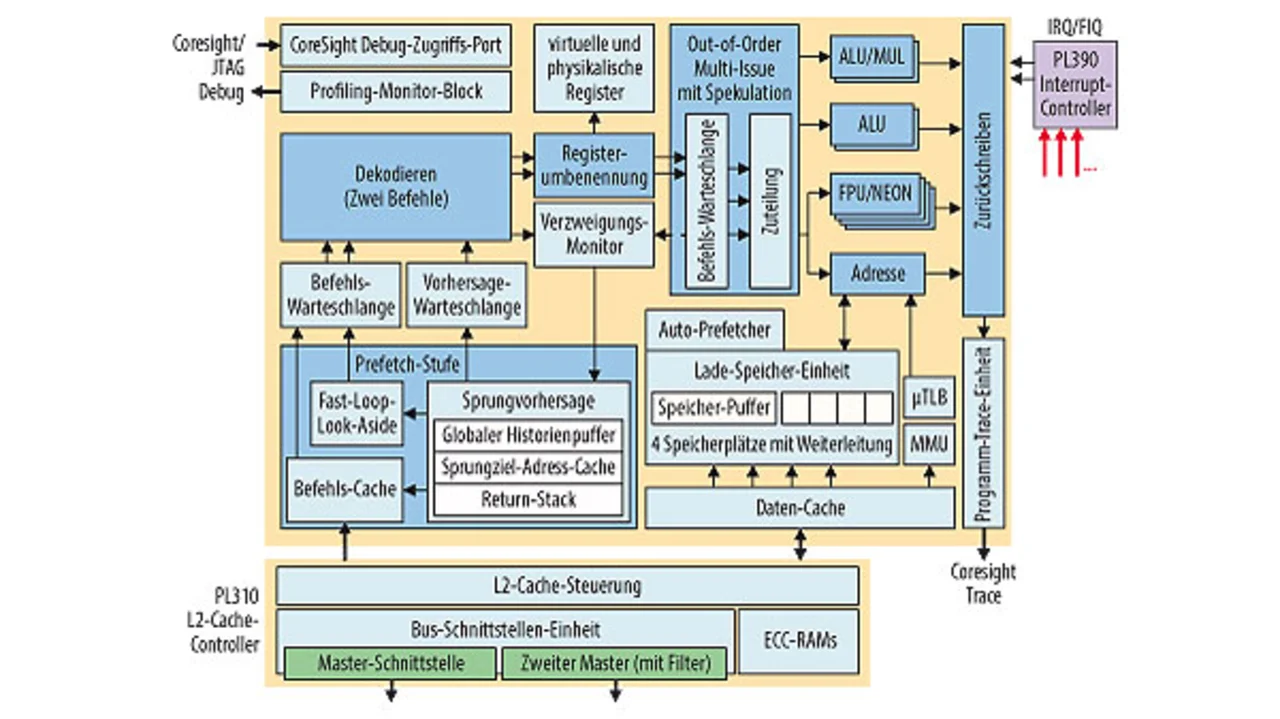

Zahlreiche Mikrocontroller setzen ARMs Core Cortex-M4 ein, die schnellsten heute verfügbaren Derivate werden mit rund 200 MHz getaktet, also halb so schnell wie der Cortex-A9 des RZ/A. Er weist allerdings auch eine erheblich leistungsfähigere Mikroarchitektur auf (Bild 5), welche eine Rechenleistung von 2,5 DMIPS/MHz ermöglicht – der Cortex-M4 kommt lediglich auf die Hälfte, nämlich 1,25 DMIPS/MHz

Beim Cortex-A9 handelt es sich um eine Dual-Issue-Out-of-Order-CPU mit einer 8- bis 11-stufigen Pipeline (8 Stufen für arithmetisch-logische Befehle, 11 für Laden/Speichern), die parallel zwei Instruktionen laden und dekodieren kann. Er hat drei Instruktionseinheiten (+ Sprung) und ein 24 Befehle großes Reorder-Fenster, innerhalb dessen Befehle außerhalb der ursprünglichen Reihenfolge ausgeführt werden können – z.B. wenn ein Befehl auf einen Wert warten muss, können folgende Instruktionen vorgezogen werden, damit die Pipeline nicht blockiert wird. Eine weitere Eigenschaft, welche die Rechenleistung erhöht, ist die dynamische Sprungvorhersage, die er u.a. mittels einer 512 Byte großen Sprunghistorientabelle realisiert.

Damit lässt sich in vielen Fällen verhindern, dass Befehle unnötig geladen und dekodiert sowie die Instruktions-Pipeline unnötig gefüllt wird und gelöscht werden muss, wenn ein Verzweigungsbefehl abgearbeitet werden muss und die Codeausführung an einer ganz anderen Adresse fortgesetzt wird.

Kurz gesagt – Anwendungen mit RZ/A sind einfach

Renesas entwickelte die neu vorgestellten RZ/A-Bausteine speziell für den HMI-Markt. Dieser stellt eine Reihe von Anforderungen, die an sich nicht einmalig sind; ihre Kombination allerdings macht es schwierig, diesen Markt mit herkömmlichen Systemen abzudecken. Es besteht Bedarf an großem RAM, allerdings wiederum nicht so groß, dass ein Mikroprozessor mit 128 MB an DDR3-RAM benötigt würde. Die Leistungsanforderungen sind gering, solange der Baustein von einem kompetent entwickelten Display Controller unterstützt wird. Allerdings sind sie nicht so niedrig, dass man sie mit einem Mikrocontroller mit zum Beispiel 100 MHz Taktfrequenz abdecken könnte.

Die RZ/A-Familie bietet gerade genug Konnektivität für alle HMI-Anwendungen, mehr als genug Rechenleistung und ein gutes Angebot an RAM für flexiblen Einsatz der Produktfamilie. Sie ist kostenoptimiert und bietet eine dedizierte Lösung, die nicht nur vom boomenden Markt für Display-Technik profitieren lässt, sondern diesen auch weiter vorantreiben wird.

Der Autor

| Robert Kalman, BEng, MBA |

|---|

| studierte Elektrotechnik an der University of Southampton. Nach 5-jähriger Tätigkeit bei Freescale wechselte er im Oktober 2007 zu Renesas, wo er zunächst als Marketing-Ingenieur tätig war. Heute arbeitet er als Marketing-Manager für Renesas‘ High-End-MCU- und MPU-Gruppe innerhalb des Geschäftsbereiches Industrie. |

Robert.Kalman@renesas.com

- Ansteuerung von TFTs leichtgemacht

- Was bedeutet das für die RZ/A-Bausteine?

- ARMs Cortex-A9 – nicht nur schneller als Cortex-M