Leiterplatten-Antennenarrays

Zuverlässige Bestückung von ICs in LGA-Gehäusen

Fortsetzung des Artikels von Teil 1

Richtlinien für das Leiterplattenlayout

Um die Auswirkungen von Leiterplatten- und IC-Gehäusetoleranzen zu minimieren, wird empfohlen, bei der Leiterplattenbestückung von LGA-IC-Gehäusen die im Folgenden aufgezählten Richtlinien anzuwenden. Die genannten Regeln eignen sich für LGAs mit 0,25 mm großen Anschlüssen (quadratisch oder rechteckig) in einem Raster von 0,5 mm sowie für vergleichbare Geometrien.

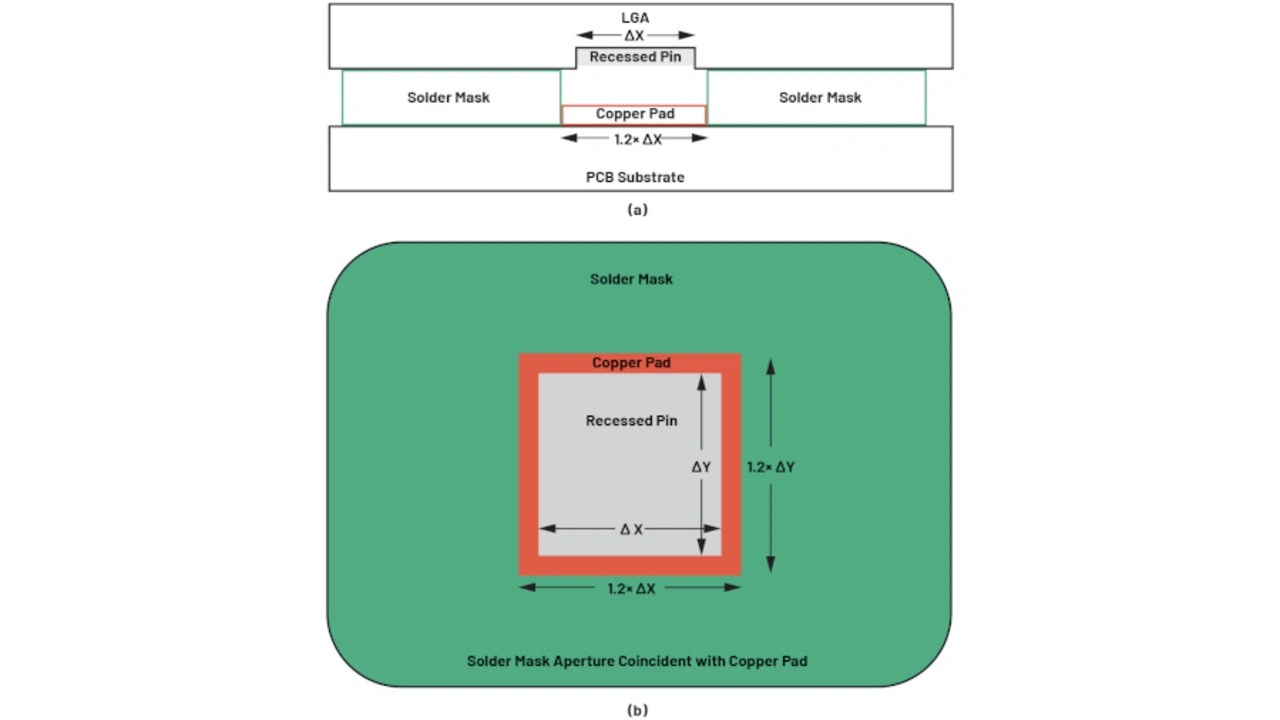

- Die Anschlussflächen auf der Leiterplatte sollten in jeder Richtung 20 % größer sein als die nominellen Abmessungen der LGA-Kontaktflächen (Bild 6). Dies entspricht bei quadratischen Anschlussflächen mit 0,25 mm Kantenlänge einem Plus von etwa 0,05 mm. Das Überdimensionieren der Leiterplattenanschlussflächen (Pads) hilft, die Auswirkungen von Registrierungsfehlern zu verringern.

- Leiterplatten-Pad und Lötstoppmasken-Öffnung sollten ein Verhältnis von 1:1 haben. Dies ist gewissermaßen eine Mischung aus einem lötstoppmaskendefinierten und einer nicht lötstoppmaskendefinierten Lotdepot. Das Verhältnis von 1:1 trägt dazu bei, dass einerseits genügend Lot für eine einwandfreie Verbindung zur Verfügung steht und andererseits ein ausreichender »Damm« zwischen den Pads entsteht, um Kurzschlüsse zu vermeiden.

- Für die Lotpastendruckschablone sollte die Massefläche in mehrere kleinere Öffnungen unterteilt werden, die ähnlich groß sind wie die Anschlussflächen des LGA-ICs. Diese Maßnahme sorgt für eine gleichmäßige Verteilung des Lots auf die großen exponierten Kupferflächen der Leiterplatte.

- Der Umriss des LGA-IC-Gehäuses sollte nicht im Bestückungsdruckprozess (Siebdruck) mit gedruckt werden. Hierdurch wird jedes Risiko vermieden, dass der Umriss die Planarität des LGA-IC-Gehäuses beeinträchtigt.

- Ebenso sollten alle Umrisse von Bauteilen, die in der Nähe des LGA-ICs platziert wurden, von der automatisch vom PCB-CAD-Programm erstellten Siebdruckvorlage für den Bestückungsaufdruck entfernt werden.

- Auch alle Beschriftungen, Pin-1-Markierungen usw. in der Nähe des LGA-ICs sollten aus der Siebdruckvorlage entfernt werden. Empfohlen wird, eine Sperrzone von 1,85 mm zur nächsten LGA-Anschlussfläche einzuhalten.

- Andere Bauteile sollten möglichst weit weg vom LGA angeordnet werden. Hier wird empfohlen, eine Sperrzone von 2,3 mm zur nächsten LGA-Anschlussfläche einzuhalten.

Jobangebote+ passend zum Thema

Die drei letztgenannten Richtlinien beeinflussen die Montage weniger als die ersten vier und sind daher eher als »Best Practices« einzustufen. Dennoch sollten diese Empfehlungen nach Möglichkeit so weit umgesetzt werden, wie es der Platz auf der Leiterplatte erlaubt.

Auch wenn sich dieser Beitrag nicht mit Gehäusen mit kleineren Anschlüssen in einem kleineren Raster befasst, dürften diese Richtlinien auch dort anwendbar sein – und sei es nur als Ausgangspunkt für die Konzeption von Anschlussflächen und Lötstoppmaskenöffnungen (Bild 6). Wenn die Pad-Abmessungen und das Raster jedoch deutlich kleiner sind, müssen möglicherweise aufwendigere Fertigungstechniken angewendet werden, um die Lötstoppmaskentoleranzen zu berücksichtigen.

Beispiel: Leiterplatte mit dem ADAR1000

Als Beispiel für ein Leiterplattenlayout wird der ADAR1000 verwendet, ein Beamforming-IC mit vier Kanälen für einen Frequenzbereich von 8 GHz bis 16 GHz (X-Band und Ku-Band), der für den Einsatz in planaren Antennenarrays konzipiert ist. Die oben beschriebenen Layoutvorgaben wurden beim Evaluation Board ADAR1000-EVALZ [2] befolgt.

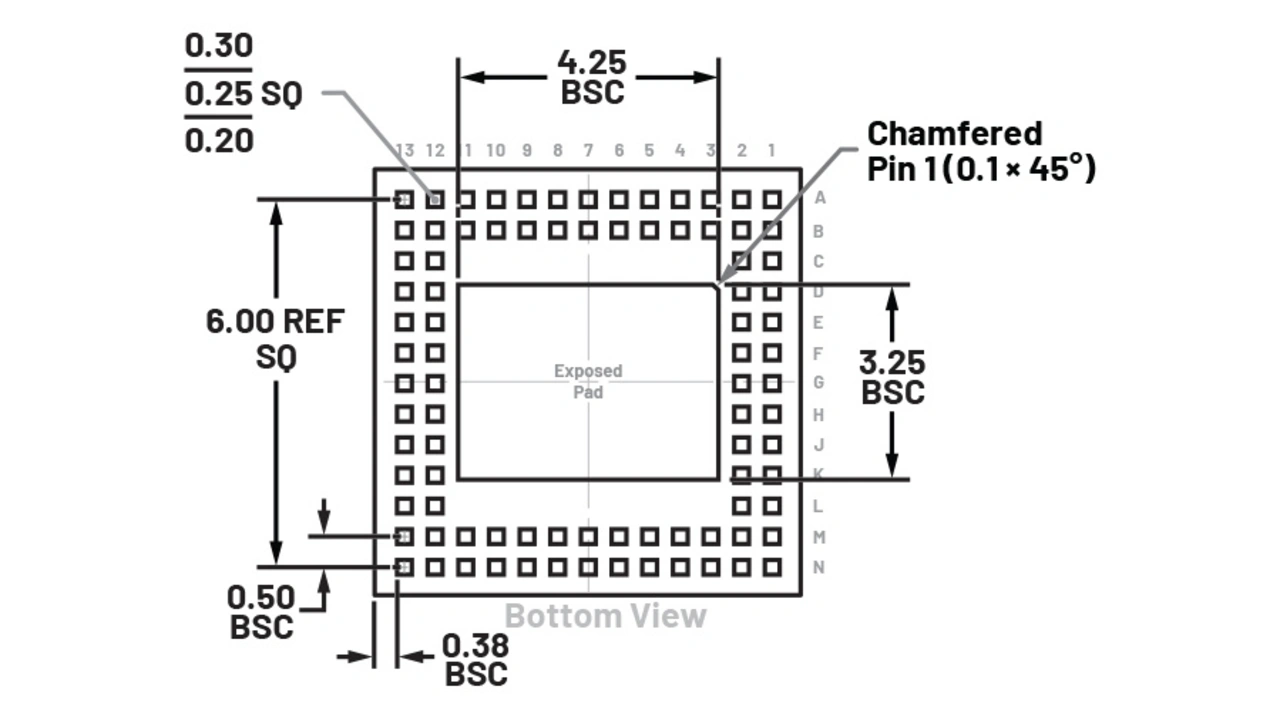

Der ADAR1000 ist in einem 7 mm × 7 mm großen LGA-Gehäuse untergebracht, seine Anschlüsse sind in Form zweier konzentrischer Quadrate angeordnet und in der Mitte befindet sich zusätzlich eine herausgeführte Massefläche (Bild 7). Die Abmessungen jeder Anschlussfläche betragen 0,25 mm × 0,25 mm bei einer Toleranz von ±0,05 mm. Die Massefläche hat eine nominelle Größe von 4,25 mm × 3,25 mm. Nicht dargestellt in Bild 7 ist die Vertiefung der Pads von 0,02 mm.

Gemäß den Richtlinien für eine zuverlässige Bestückung wurde beim Layout der Leiterplatte für den ADAR1000 folgendermaßen verfahren:

Bilder 8 bis 12

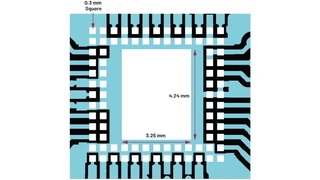

- Die Leiterplatten-Pads wurden um 20 % überdimensioniert, sind also um 0,05 mm größer als die nominellen Abmessungen der Anschlussflächen des ADAR1000. Die Pads der Leiterplatte haben folglich eine Kantenlänge von 0,3 mm (Bild 8).

- Die Öffnungen in der Lötstoppmaske wurden mit 0,3 mm × 0,3 mm gleich groß gewählt wie die Leiterplatten-Pads (Bild 9).

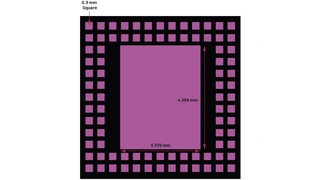

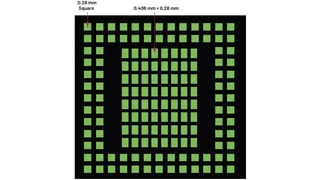

- Auf der Lotpasten-Schablone wurden für die Massefläche mehrere kleinere Öffnungen gewählt, die ähnlich groß sind wie die Pad-Öffnungen. Die quadratischen Pad-Aperturen haben eine Kantenlänge von 0,28 mm, für die Massefläche wurden Öffnungen mit den Maßen 0,406 mm × 0,28 mm gewählt (Bild 10).

- Aus der Siebdruckvorlage für den Bestückungsaufdruck wurde der Umriss um den ADAR1000 entfernt.

- Ebenfalls aus der Siebdruckvorlage entfernt wurden Umrisse von Bauteilen in einem Bereich von 2,3 mm um den ADAR1000.

- Auch jegliche Beschriftungen und weitere Elemente in der Nähe des ADAR1000, wie etwa die Pin-1-Markierung, wurden auf der Siebdruckvorlage für den Bestückungsdruck so verlagert, dass der empfohlene Mindestabstand von 1,85 mm eingehalten wird.

- Das nächste Bauelement wurde erst in einem Abstand von 2,3 mm vom ADAR1000 platziert.

Die letzten vier Richtlinien sind in Bild 11 und 12 illustriert. In Bild 12 ist folgendes erkennbar:

- In der Siebdruckvorlage fehlt der Umriss des ADAR1000.

- Das nächstgelegene Bauteil (C21) ist 2,3 mm entfernt.

- Das nächstgelegene Element auf der Siebdruckvorlage (Umriss von C21) befindet sich 1,85 mm entfernt. Als weiteres nächstgelegenes Element auf der Siebdruckvorlage folgt der Text »C35«.

In Bild 12 ist zu erkennen, dass der Text »DUT« und die Pin-1-Markierung auf der Siebdruckvorlage in einen Bereich weit außerhalb der 1,85 mm breiten Sperrzone verschoben wurden. Im Fall des ADR1000 ist die Sperrzone vom Rand des Gehäuses gerechnet mindestens 1,795 mm breit. Ist der Abstand zwischen Gehäuse- und Pad-Rand groß, wird empfohlen, die Sperrzone auf den Gehäuseumriss zu beziehen und nicht auf den Pad-Rand, wie hier.

Beim ADAR1000 Evaluation Board war es möglich, die nächstgelegenen Bauteile und Siebdruck-Elemente weit entfernt vom ADAR1000 zu platzieren. Auf realen Leiterplatten für planare phasengesteuerte Antennenarrays lässt sich diese Sperrzone nicht immer realisieren. Dennoch sollten Entwickler beim Leiterplattenlayout diese Richtlinie im Blick behalten und so gut wie möglich umsetzen.

Literatur

[1] ADAR1000 – 8 GHz to 16 GHz, 4-Channel, X Band and Ku Band Beamformer. Analog Devices, Datenblatt, 2019, www.analog.com/media/en/technical-documentation/data-sheets/ADAR1000.pdf.

[2] EVAL-ADAR1000 – ADAR1000 Evaluation Board. Analog Devices, Website, www.analog.com/en/design-center/evaluation-hardware-and-software/evaluation-boards-kits/EVAL-ADAR1000.html#eb-overview.

Die Autoren

Joel Dobler

ist als Staff Product Applications Engineer bei Analog Devices in der Aerospace and Defense Group mit dem Schwerpunkt Beamforming-Produkte tätig. Er befasst sich aber ebenso mit Vektor-Modulatoren und programmierbaren Tiefpassfiltern. Dobler arbeitet bereits seit 2006 bei Analog Devices und hatte in dieser Zeit mit einer breiten Palette von HF-Produkten wie etwa logarithmischen und RMS-Detektoren, digitalen und analogen VGAs, Mischern und I/Q-Demodulatoren zu tun.

Er hat sein Elektrotechnikstudium 2005 mit einem Bachelor an der Washington State University abgeschlossen, dem 2007 ein Master-Studium an der Portland State University folgte.

joel.dobler@analog.com

Eamon Nash

arbeitet bei Analog Devices als Applications Director für HF-Verstärker und Beamforming-ICs. Er ist seit 30 Jahren für das Unternehmen in verschiedenen Funktionen im Bereich der Mixed-Signal-, Präzisions- und HF-Produkte tätig. Den gegenwärtigen Schwerpunkt seiner Arbeit bilden HF-Verstärker und Beamforming-Produkte für Satcom- und Radaranwendungen.

Nash hat sein Elektronikstudium an der University of Limerick (Irland) mit dem Bachelor-of-Engineering abgeschlossen und ist Inhaber von fünf Patenten.

eamon.nash@analog.com

- Zuverlässige Bestückung von ICs in LGA-Gehäusen

- Richtlinien für das Leiterplattenlayout