Leiterplatten-Antennenarrays

Zuverlässige Bestückung von ICs in LGA-Gehäusen

Bei Leiterplatten-Antennenarrays begrenzt die Wellenlänge die zur Bestückung nutzbare Fläche zwischen zwei Antennenelementen. Für die knappe Fläche eignen sich ICs mit hoher Anschlussdichte. Um solche Antennenarrays in Serie zu produzieren, kommt es auf die Gestaltung der Kontaktflächen der ICs an.

Planare phasengesteuerte Antennenarrays für hohe Frequenzen erfordern oftmals komplexe Schaltungen mit Beamforming-ICs und Sende/Empfangsmodulen. Um sämtliche HF-Schaltungen im λ/2-Raster unterbringen zu können, bleibt Entwicklern nur die Chance ICs in Gehäusen mit hoher Anschlussdichte wie LGA (Land Grid Array) zu wählen. Die Anschlüsse von LGA-Gehäusen befinden sich als vertieft angeordnete Kontaktflächen an der Unterseite. Toleranzen bei den Leiterplatten-Lötstoppmasken und der Lotmenge machen die Bestückung deshalb schwierig, wenn die LGA-Kontaktflächen nicht optimal gestaltet sind.

Jobangebote+ passend zum Thema

Planare phasengesteuerte Antennenarrays

Die Technik der phasengesteuerten Antennenarrays (Phased Array Antenna) basiert auf einer besonderen Anordnung mehrerer Antennenelemente. Dabei werden die einzelnen Elemente jeweils mit einem definierten Phasenversatz angesteuert, um ein bestimmte Abstrahlungsmuster zu erzielen (Beamforming). Der Strahl kann damit auf rein elektronischem Weg in verschiedene Richtungen gelenkt werden, ohne die begrenzte Geschwindigkeit und die Zuverlässigkeitsprobleme mechanisch bewegter Richtantennen in Kauf nehmen zu müssen. Phasengesteuerte Antennenarrays zeichnen sich durch eine deutliche Verringerung der Abmessungen, des Gewichts und der Leistungsaufnahme aus, was sie insbesondere für die Wehrtechnik (Radar, Kommunikation, Weltraumeinsatz und elektronische Kriegsführung) attraktiv macht.

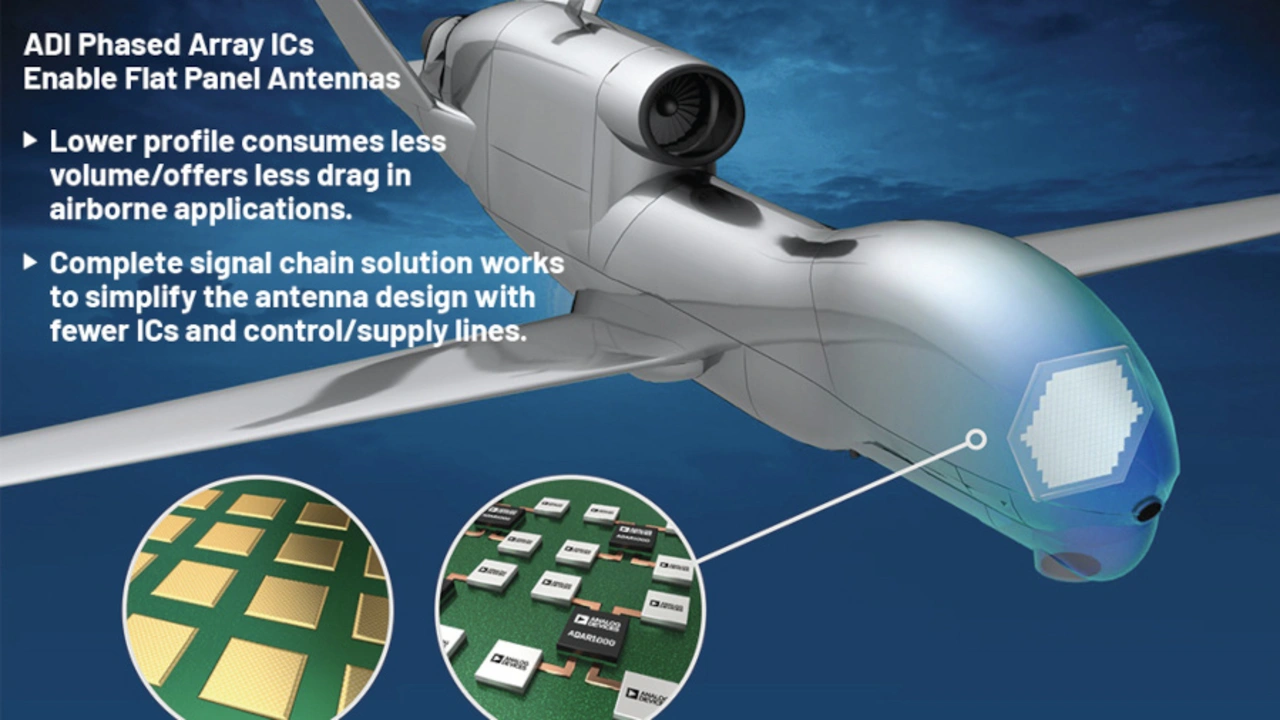

Eine als flache Baugruppe ausgeführte Radarstufe, bei der die Flächenantennen und die HF-Elektronik auf gegenüberliegenden Seiten derselben Leiterplatte angeordnet sind (Bild 1), kommt nicht nur ohne bewegliche mechanische Teile aus, sondern ist auch wegen ihres geringeren Platzbedarfs attraktiv. In analogen und hybriden, analog-digitalen Beamforming-Systemen hat sich der vierkanalige Beamforming-IC zur bevorzugten Variante entwickelt. Die Anordnung besteht aus eine Reihe von Zellen, wobei der in der Mitte platzierte vierkanalige Beamforming-IC von vier T/R-Modulen (Transmit/Receive) umgeben ist.

Die Mehrkanalfunktion dieser Beamforming-ICs sowie die zusätzlich vorhandenen Unterstützungs- und Steuerungs-Schaltungen – z.B. HF-Leiterbahnen für Sender und Empfänger, Bias-Ansteuerleitungen für die Verstärker sowie T/R-Steuerleitungen zwischen Beamforming-IC und T/R-Modul – machen die Verwendung von Gehäusen mit hoher Pin-Anzahl bei den Beamformer-ICs zwingend notwendig.

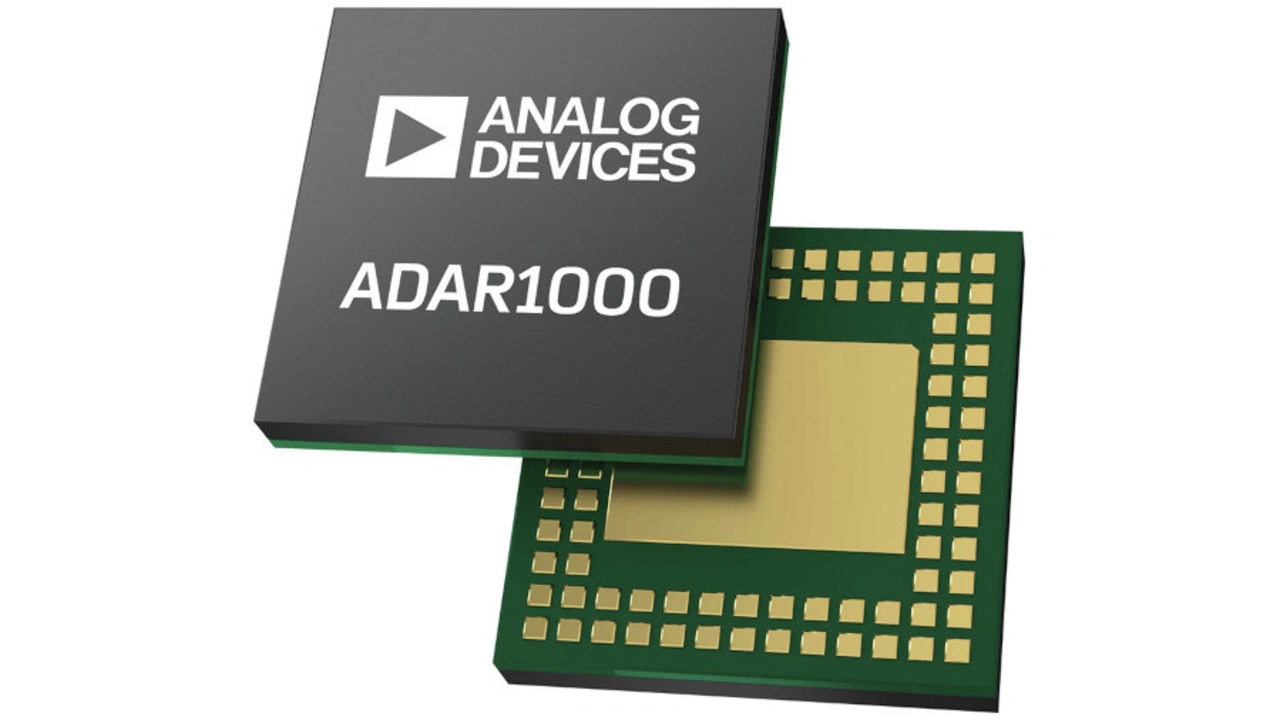

Getrieben wird dieser Trend zusätzlich durch die Notwendigkeit, ein λ/2-Raster – z.B. 15 mm bei 10 GHz – einzuhalten. Aus diesem Grund haben sich LGA-Gehäuse zu einer beliebten Option für mehrkanalige Beamforming-ICs entwickelt. Der ADAR1000 von Analog Devices ([1], Bild 2) ist ein erstklassiges Beispiel für einen typischen Beamforming-IC im LGA-Gehäuse.

Der Lötprozess

Die automatisierte Leiterplattenbestückung gliedert sich in mehrere Abschnitte. Den Anfang macht das Aufbringen der Lotpaste auf die vom Lötstopplack ausgesparten Kupferflächen der Leiterplatte. Hierfür wird eine Schablone für den Lotpastendruck auf der Leiterplatten-Oberfläche abgelegt und so ausgerichtet, dass die Löcher in der Schablone mit den zugehörigen Metallflächen auf der Platine zur Deckung kommen. Anschließend wird die Lotpaste mit einer Rakel über die Schablone gezogen, um die Aussparungen in der Schablone mit Lotpaste zu füllen. Daraufhin wird die Schablone entfernt.

Als nächstes werden die oberflächenmontierbaren Bauelemente auf die Lotpastendepots gesetzt, und die gesamte Anordnung aus Leiterplatte, Lotpaste und Bauelementen wird danach in einen Reflow-Ofen gegeben, in dem die Lotpaste schmilzt und eine feste Verbindung zwischen den Anschlussflächen der Bauelemente und den Kontaktflächen der Leiterplatte herstellt. In diesen Vorgang spielen gleich mehrere Variablen hinein, die zu Problemen führen können.

Lötmasken-Varianz und Schablonen-Invarianz

Neben der Lotpasten-Schablone legt auch die – meist in grüner Farbe gehaltene – Lötstoppmaske auf der Leiterplatte fest, an welchen Stellen Lotpaste auf die Platine aufzubringen ist. Häufig werden die Öffnungen (Aperturen) in der Lötstoppmaske geringfügig kleiner ausgeführt als die darunter befindlichen Anschlussflächen, sodass hier die Pads durch die Lötstoppmaske definiert werden.

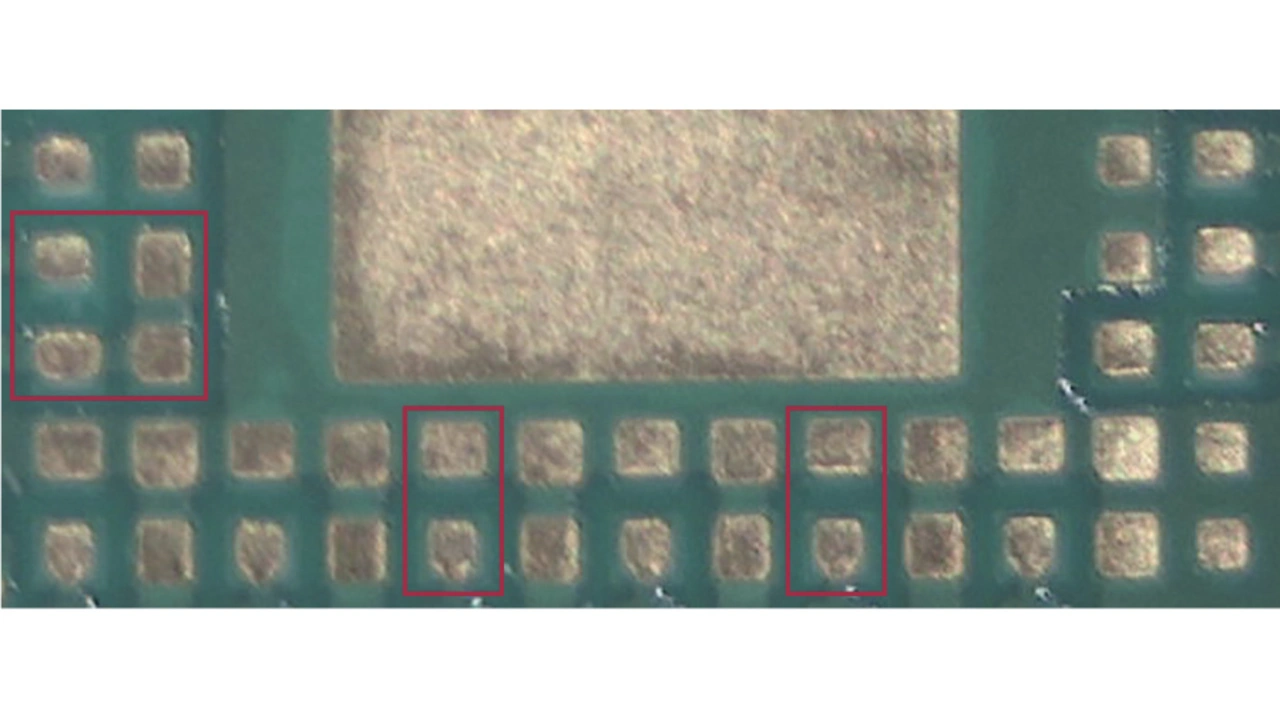

Bei vielen Leiterplatten kommen LPI-Lötstoppmasken (Liquid Photo-Imageable) zum Einsatz, die dem Standard IPC-SM-840 Class 3 entsprechen. Je nach Fertigungslos, Anbieter usw. kann es passieren, dass die Öffnungen in der Lötstoppmaske unterschiedlich groß und infolge von Registrierungsfehlern der Lötstoppmaske nicht korrekt ausgerichtet sind. Bild 3 zeigt ein Beispiel einer Lötstoppmaske mit unterschiedlich großen Aperturen (rot markiert).

Wenn die Pads durch die Lötstoppmaske definiert werden und die einzelnen Aperturen unterschiedlich groß sind, schwankt die effektive Größe der exponierten Kupferfläche, obwohl die Kupfer-Pads selbst alle einheitlich groß sind. Dies trifft insbesondere dann zu, wenn sich unter der Lötstoppmaske große, meist mit Masse verbundene Kupferflächen befinden.

Nun zur metallenen Schablone für den Lotpastendruck (Bild 4). Wenn die Öffnungen in dieser Schablone von unterschiedlicher Größe sind, wird unter Umständen unterschiedlich viel Lotpaste auf die einzelnen Pads aufgebracht. Allerdings werden Lotpastendruckschablonen in der Regel aus Edelstahlblechen hergestellt, in die mit Laserstrahlen die Öffnungen mit minimalen Schneidbreiten von 0,05 mm (oder besser) sowie Aperturtoleranzen von 0,013 mm (oder besser) geschnitten werden. In der Praxis unterliegt die Größe der Öffnungen deshalb nur sehr geringen Schwankungen. Diese engen Toleranzen gewährleisten also, dass stets einheitliche Mengen an Lotpaste auf die Anschlussflächen der Leiterplatte aufgebracht werden.

Die Größenschwankungen der Lötstoppmaske können in Verbindung mit den geringen oder gänzlich fehlenden Größenvariationen der Lotpastendruckschablonen zu der Situation führen, dass keine zuverlässige Leiterplattenbestückung erfolgt, weil es entweder zu Kurzschlüssen zwischen zwei IC-Anschlüssen kommt oder keine Verbindung zwischen IC-Anschlussfläche und Leiterplatten-Anschlussfläche hergestellt wird.

Offene Lötstellen können vorkommen, wenn eine Anschlussfläche auf der Leiterplatte eine größere Apertur hat und die Aperturabmessungen bei benachbarten Pads den Vorgaben entsprechen oder sogar kleiner sind.

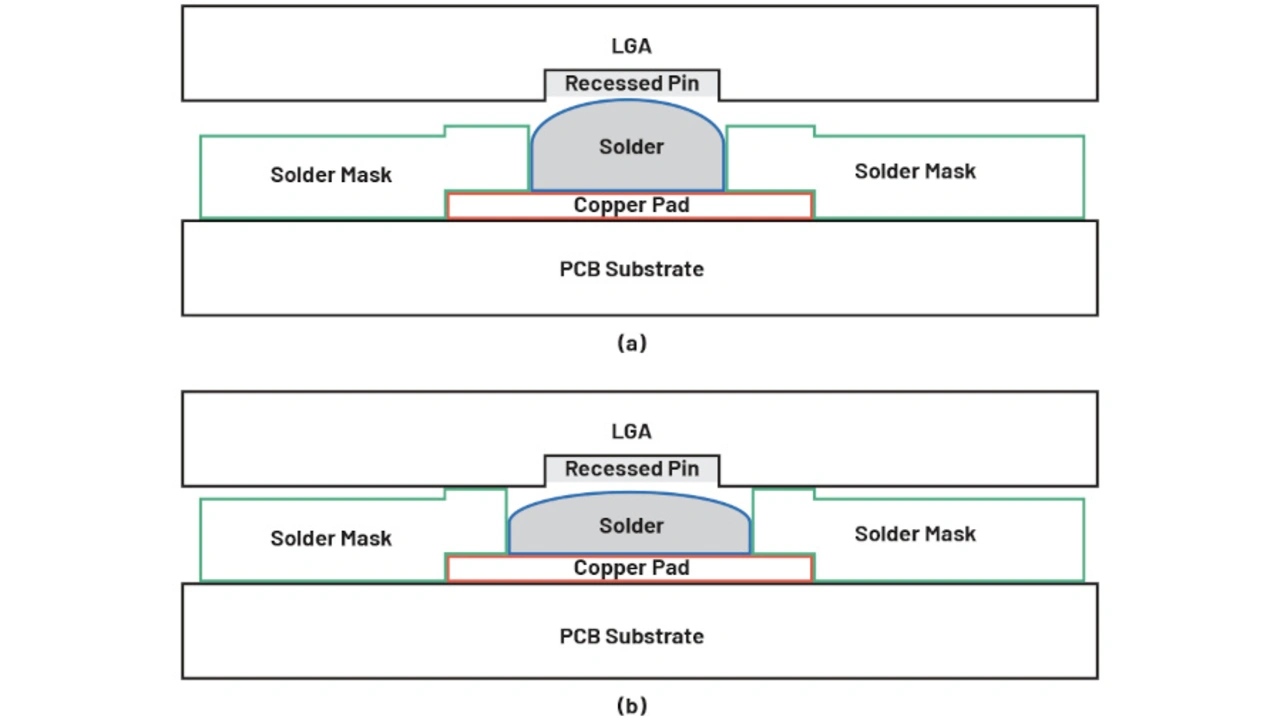

In Bild 5a ist (in vergrößerter Darstellung) die seitliche Ansicht eines LGA-IC-Gehäuses auf einer Leiterplatte nach dem Aufbringen der Lotpaste zu sehen. Nach dem Erhitzen der Lotpaste bildet sich in der Vertiefung, die durch den Ausschnitt in der Lötmaske gebildet wird, eine Lotperle, die so weit herausragt, dass sie sich mit der vertieft angeordneten Anschlussfläche des ICs verbindet.

Bild 5b zeigt dagegen einen Fall, in dem die Öffnung der Lötstoppmaske größer ist als normal, sodass die sich bildende Lotperle flacher ausfällt und sich deshalb nicht mit der vertieft angeordneten Anschlussfläche des IC-Gehäuses verbinden kann.

- Zuverlässige Bestückung von ICs in LGA-Gehäusen

- Richtlinien für das Leiterplattenlayout