Neue Produktionstechniken für HF-Serienprodukte ermöglichen neue Anwendungen

Höchstfrequenz-Elektronik wird kostengünstiger

Fortsetzung des Artikels von Teil 5

Plus für die Anwendung: Kosten der Serienfertigung deutlich reduziert

Ein Problem für die Anwendung von Höchstfrequenz-Elektronik war bislang die Herstellung von entsprechenden Komponenten und Systemen, denn kostenoptimale Fertigungsverfahren standen bisher nur für Produkte bis 40 GHz zur Verfügung. Für die kostengünstige, sichere Produktion von ICs und Höchstfrequenz-Modulen in größeren Stückzahlen waren die dort eingesetzten Fertigungsverfahren allerdings noch nicht geeignet; für eine wirtschaftliche Modulproduktion fehlten sichere Montage- und Testverfahren. Hier knüpfte z.B. das Forschungsprojekt EUREKA-PROKOSMOS an, welches in Zusammenarbeit mit irischen und österreichischen Partnern im Rahmen einer EU-Förderung durchgeführt wurde. Mit innovativen, standardisierbaren Modulkonzepten ließen sich die Kosten in der Serienfertigung von Höchstfrequenz-Modulen – nicht zuletzt auf Grund der Arbeiten des Forschungsprojekts – mittlerweile auf 50 % reduzieren und fertigungsgerechte Baugruppenarchitekturen entwerfen. Aufbau-, Verbindungs- und Prüftechnik für höhere Frequenzen bis 100 GHz werden letztlich bereits beherrscht. Diese Techniken sind auch für größere Stückzahlen wirtschaftlich.

Jobangebote+ passend zum Thema

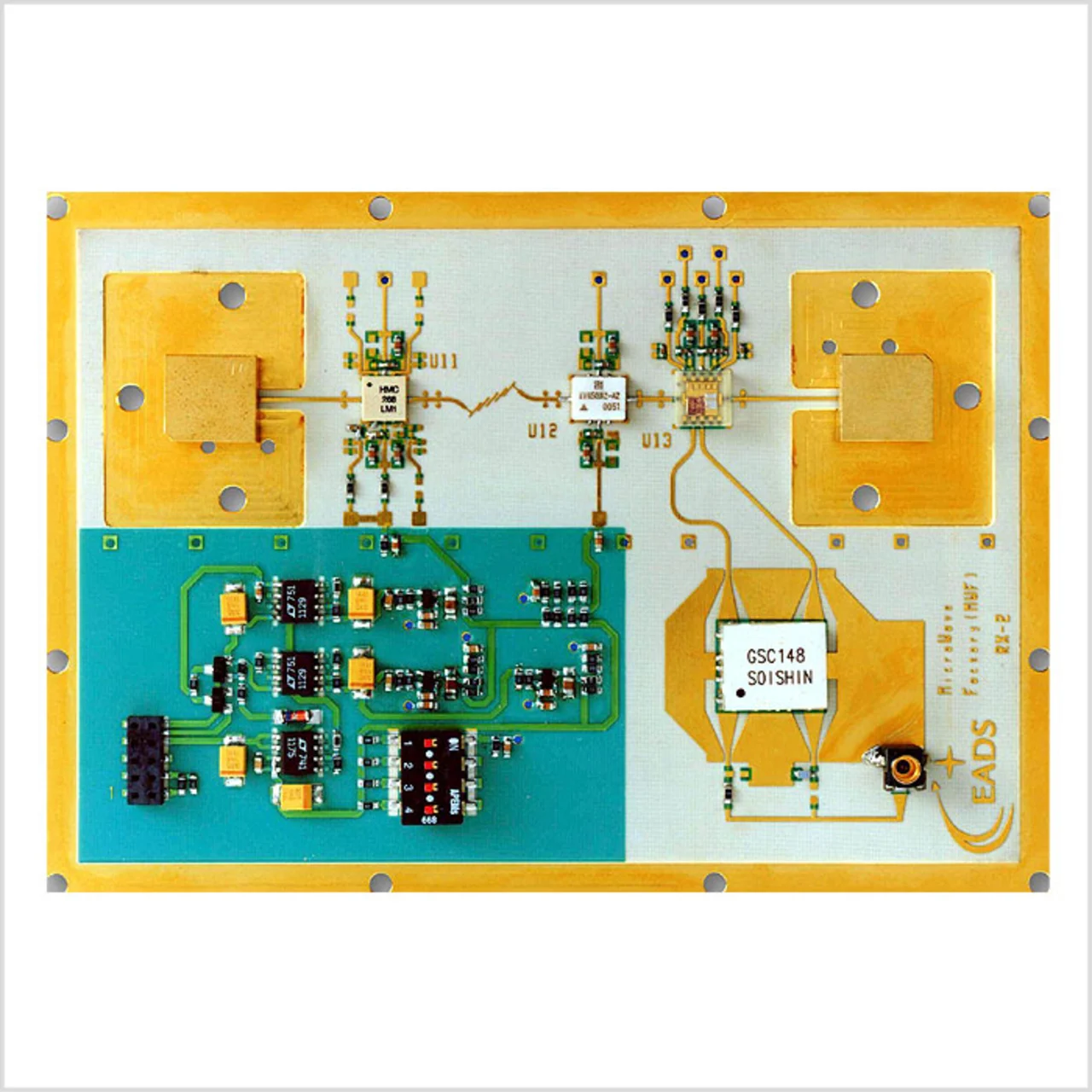

Für zukünftige Baugruppen wurden mittlerweile modulare Bauweisen und Packaging-Techniken bereitgestellt, die SMD-Submodule (Surface Mounted Devices – oberflächenmontierbare Bauteile) enthalten und für SMD-Linien geeignet sind (Bild 1).

Mit gehäusten Bauelementen können die Probleme der Bare-Chip-Verarbeitung und auch die Reinraum-Forderungen (die Partikel-Kontamination muss unter bestimmten Werten bleiben) umgangen und die Vorteile kostengünstiger SMD-Fertigungslinien ausgenutzt werden.

Höchstfrequenztaugliche multifunktionale Schaltungsträger für Frequenzen von 30 bis 100 GHz mit integrierten passiven und Höchstfrequenz-Strukturen bilden mittlerweile eine standardisierbare Basis zur fertigungsfreundlichen Oberflächenmontage. Im Folgenden deshalb ein Einblick in Verfahren und Ausrüstungen, die für eine wirtschaftliche Groß-Serienfertigung von Produkten mit Frequenzen über 40 GHz entwickelt wurden.

Flip-Chip-Technik mit abgesicherten Prozessen für ICs

- Höchstfrequenz-Elektronik wird kostengünstiger

- Marktfähige Preise gerade für das Automotive-Radar nötig

- Großstückzahl-Fertigungsverfahren für die Optoelektronik

- Industrielle Produktionsprozesse für multifunktionale Schaltungsträger

- Keramisches Trägermaterial für die HF-Modul-Serienproduktion

- Plus für die Anwendung: Kosten der Serienfertigung deutlich reduziert