Arm TechDays 2019

For Cloud and Infrastructure: This is Arms Neoverse Universe

Fortsetzung des Artikels von Teil 4

Neoverse Development Board

To help customers access the Neoverse universe, Arm offers the Neoverse System Development Platform (SDP), which will be available this quarter (Q1/2019) (Figure 12).

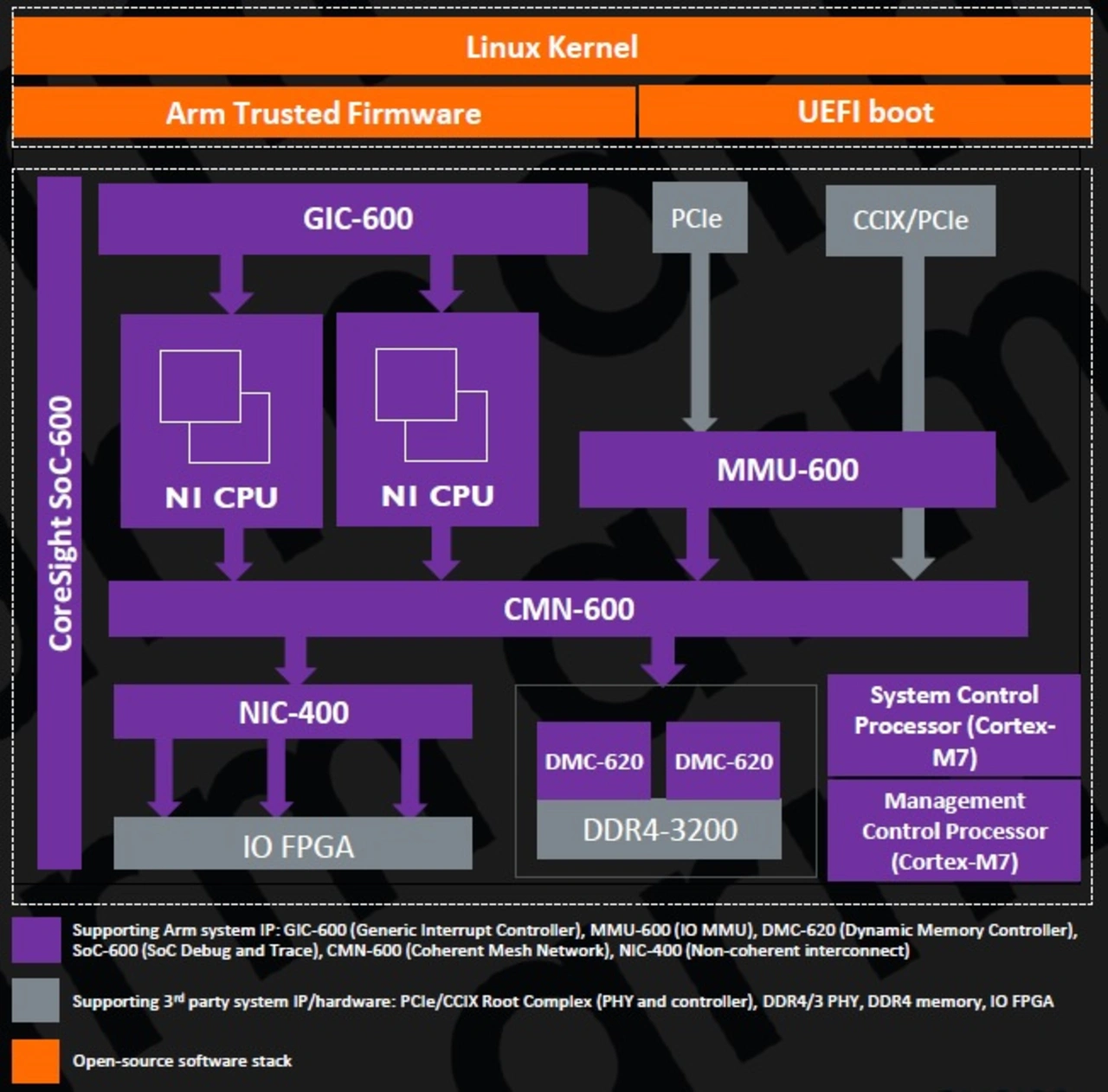

In addition to two dual-core neoverse N1 CPU clusters implemented in 7 nm, each with 1 MB L2 cache per core (clock frequency up to 3 GHz possible), it also includes two Cortex M7 microcontrollers for system control and management tasks. DDR4-3200 memory modules can be connected to the CMN-600 mesh network via two DMC-620 memory controllers. There are two 16 GB DDR4-RDIMMs on the board. The mesh network is also connected to 8 MB system level cache and the memory management unit MMU-600, to which external accelerator hardware such as a Xilinx FPGA can be connected via PCIe (a PCIe 3.0 switch with GbE, SATA and USB 3.0 are located on the board as well as 3 standard expansion slots with 16, 8 and 1 line) or CCXI. The Cache-Coherent-Interconnect-for-Accelerators (CCIX), pronounced "see six", is an open, cache-coherent connection architecture developed by the CCIX consortium. CCIX was designed to simplify communication between the central processor and the various accelerators in the system by cache-coherently extending the PCIe standard. On the board there is a CCIX/PCIe Gen4 slot with 16 lines.

Also attached to the CMN-600 is a non-coherent CoreLink NIC-400 Network Interconnect that enables the creation of an AMBA-compliant network infrastructure. Possible configurations for the CoreLink NIC-400 Network Interconnect can range from a single bridge component, such as an AHB to AXI protocol conversion bridge, to a complex infrastructure consisting of up to 128 masters and 64 slaves of AMBA protocols. An example of an application is an FPGA as an I/O device for boot memory, QSPI, eMMC, UART or HDMI video. The platform controller chip (PCC) manages the SoC and the board features and is connected to the two Cortex M7 controllers via I2C or UART.

The open source firmware software stack contains 64-bit drivers, file system, middleware, CCXI/PCIe drivers for Linux, the AArch64 kernel, hypervisor, arm trusted firmware, secure boot, UEFI/ACPI port for the N1 CPUs and others.

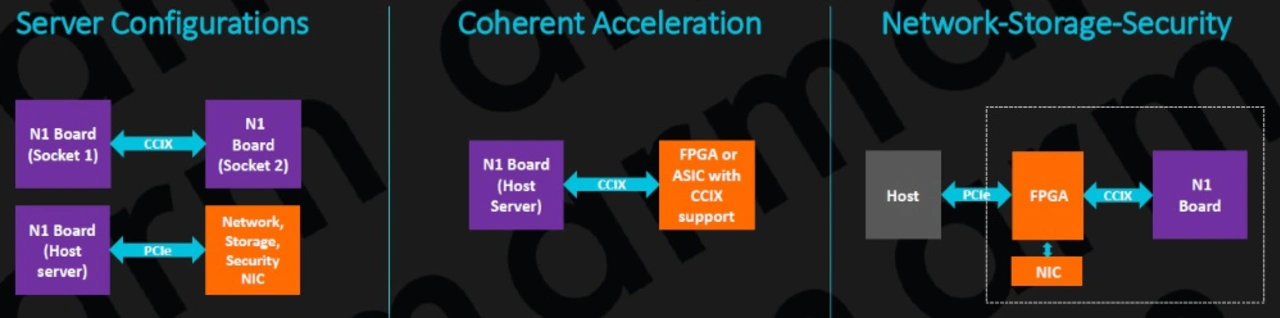

Figure 13 shows three possible use cases for prototyping, software development and performance evaluation.

In addition to the well-known Arm Development Studio, which now also enables a multi-core/multi-thread debugger and a cache utilization analysis via the Neoverse N1 statistical extensions, there are also development tools in the Arm Allinea Studio with C++ and Fortran compilers specially developed for high-performance computing applications. It also provides hand-optimized math libraries and scalable debugging functionality, performance analysis, and even supercomputer systems.

- For Cloud and Infrastructure: This is Arms Neoverse Universe

- The Neoverse-E1-CPU

- Neoverse Reference Designs

- Neoverse-N1 Hyperscale-Reference Design

- Neoverse Development Board

- Conclusion