Arm TechDays 2019

For Cloud and Infrastructure: This is Arms Neoverse Universe

Fortsetzung des Artikels von Teil 3

Neoverse-N1 Hyperscale-Reference Design

For applications that require the highest computing power, such as server and cloud applications, Arm has developed the Hyperscale reference design. Hyperscaling is the ability of an architecture to scale appropriately when increased demand is added to the system. This includes the ability to seamlessly add compute, storage, network and storage resources to a particular node or set of nodes. Hyperscale computing is necessary to build a robust and scalable cloud or big data infrastructure.

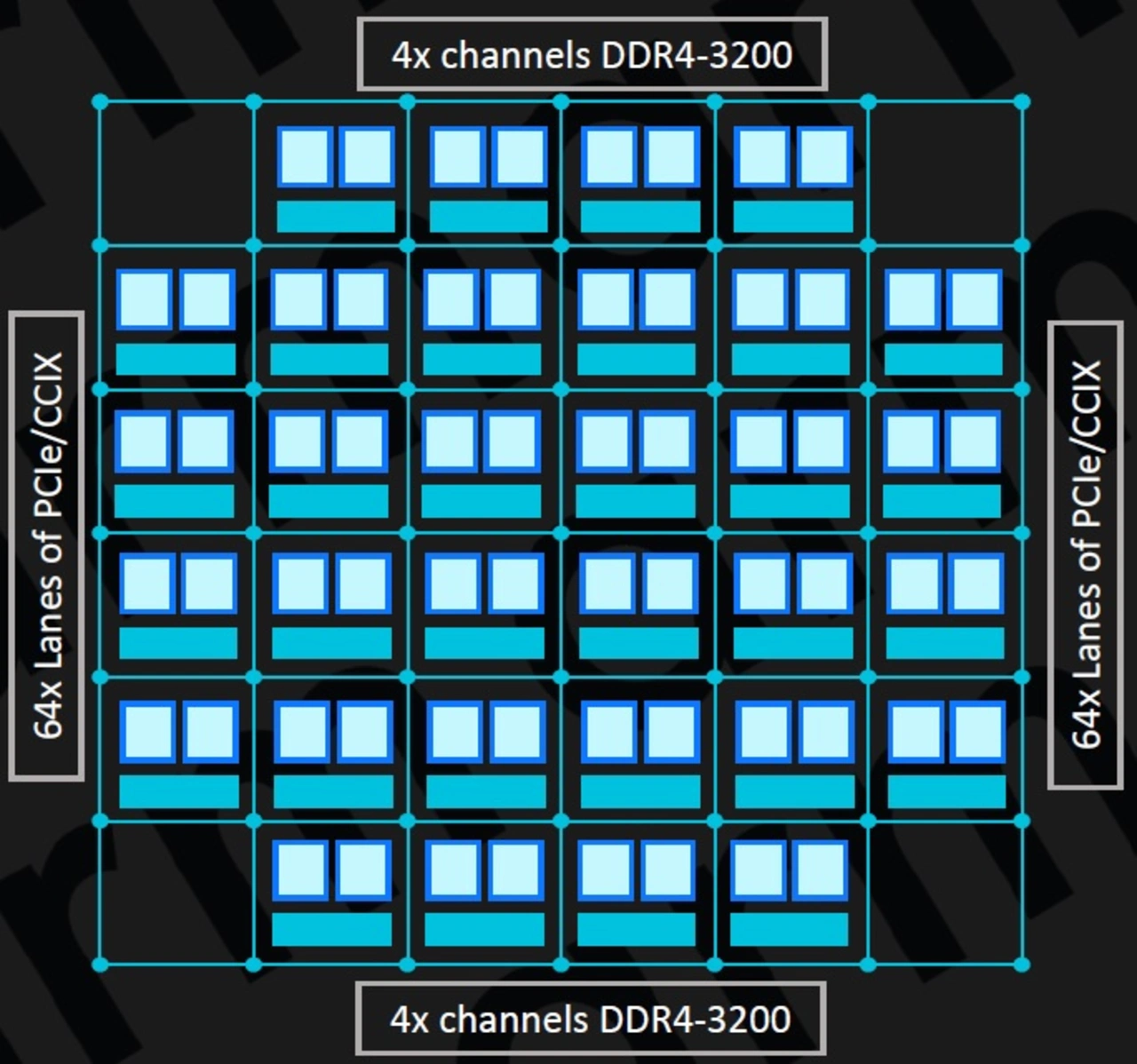

The arm design includes 64 to 128 N1 CPUs with a clock frequency between 2.6 and 3.1 GHz, a CMN-600-8x8 mesh network with 128 MB system level cache (SLC) shared by CPUs, hardware accelerators and I/Os and with a data throughput of more than 1 TB/s, 128 lines for PCIe/CCIX and 8 channels for DDR4-3200 memory (Figure 9). The 1.8 to 2.2 GHz clocked coherent mesh network can transmit two data packets per clock cycle because it operates bidirectionally.

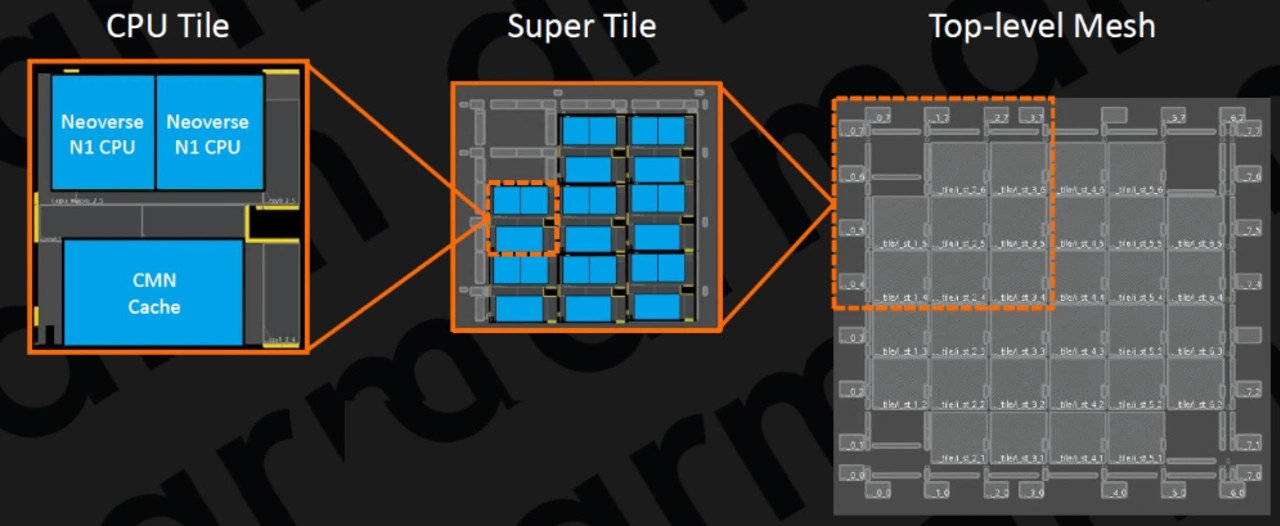

The scalability of the architecture is shown in Figure 10. From a CPU tile with 2 N1 CPUs and a part of the SLC (which can be divided into up to 64 parts with up to 128 MB each within the network to keep the transmission paths short), so-called super tiles of 8 tiles each are formed, from which in turn the entire network is formed. Figure 10 shows an example of an architecture with 64 CPUs formed from 4 super tiles.

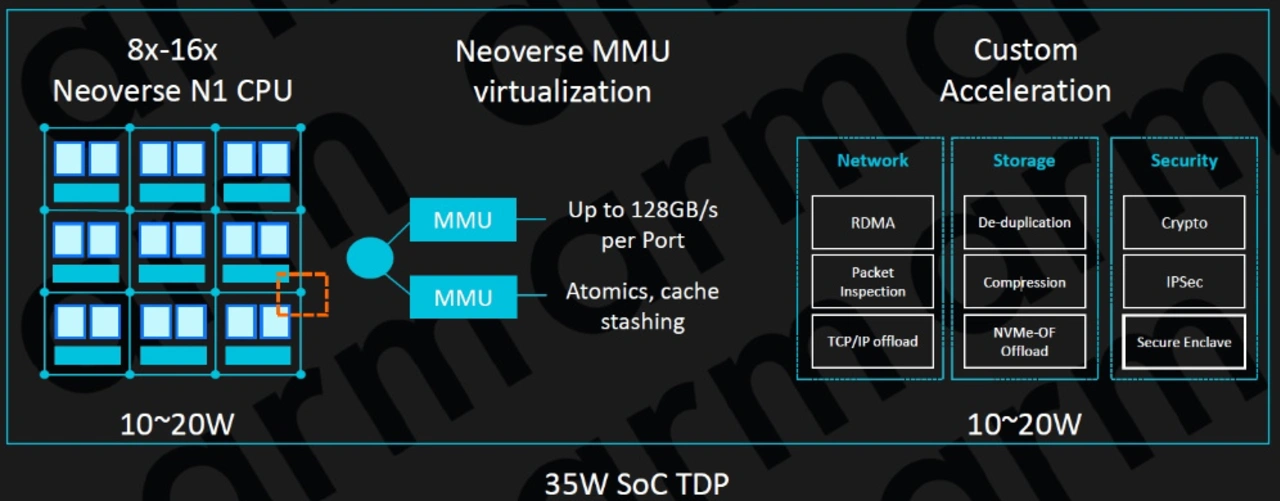

The neoverse N1 "edge reference design" is to be used for compute-intensive workloads in the edge cloud and for network, storage and security applications. An example of the latter is the shift from the traditional approach of attaching network and storage solutions to the computer cluster via devices with fixed functionality to an approach with software-defined solutions and virtualization. SmartNICs have so far often been mapped within an energy budget of 35 to a maximum of 65 W via 8 to 16 Cortex A72 CPUs plus hardware accelerators. Figure 11 shows an example of a SoC with only 35 W power consumption, consisting of 8-16 Neoverse N1 CPUs, virtualization and hardware acceleration for network, storage and security tasks.

- For Cloud and Infrastructure: This is Arms Neoverse Universe

- The Neoverse-E1-CPU

- Neoverse Reference Designs

- Neoverse-N1 Hyperscale-Reference Design

- Neoverse Development Board

- Conclusion