Verbessern die Audio-Signalqualität

Fortsetzung des Artikels von Teil 1

Systemintegration auf Wafer-Ebene

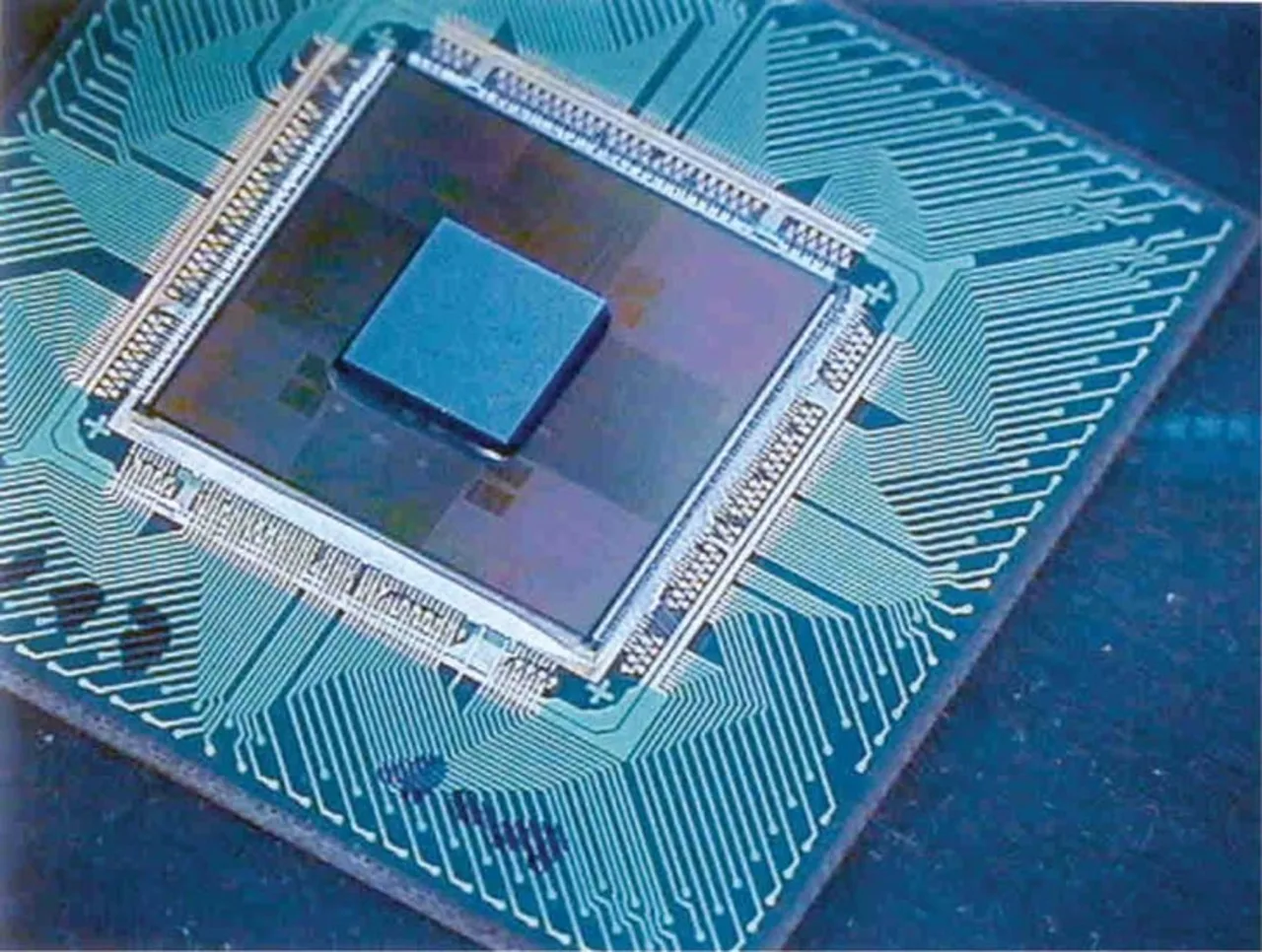

Wafer-Level-Packaging-Technologien werden gegenwärtig bereits sehr vielfältig in zahlreichen Produkten angewandt. Ein entscheidendes Kriterium für die Weiterentwicklung dieser Technologie ist der Vorteil, dass auf den großflächigen Wafern durch Kombination zusätzlicher technologischer Schritte gleichzeitig weitere Komponenten parallel realisiert werden können. So können beispielsweise durch die Nutzung der sog. Umverdrahtungstechnologie (Redistribution) passive Komponenten (Widerstände und Induktivitäten) sehr effektiv auf der Chip-Oberfläche integriert werden. Gleichzeitig wird eine Anpassung der Anschlussverbindungen hinsichtlich Pad-Größe, Abstand und Metallisierung (z.B. Lot-Bumps) für die Montage zum Board-Level (Leiterplatte) realisiert. Durch ein entsprechendes Design besteht ebenfalls die Möglichkeit, unter Berücksichtigung der Anschlusskonfigurationen, weitere aktive Bauelemente – z.B. einer anderen Halbleiterbasistechnologie – als „Chip-zu-Wafer Flip Chip“ oder „Face to Face“-Prozess zu integrieren (Bild 3). Mit optimal ausgelegten Chipumverdrahtungslagen kann hierdurch auch die Leistungsfähigkeit bei der Kopplung von zum Beispiel analog-digitalen Komponenten gesteigert werden.

Jobangebote+ passend zum Thema

Durch die anhaltend steigenden Anforderungen hinsichtlich Miniaturisierung ist die Anwendung der Flip-Chip- und der Chip-Size-Packaging-Technologie (CSP) in vielen Produkten bereits umgesetzt. Vor allem der HF- und der Mixed-Signal-Bereich werden aufgrund der steigenden Produktzahlen in der Mobil- und Breitband-Kommunikation besonders interessant sein. Die gestiegene Leistungsfähigkeit von Si-, SiGe- und GaAs-Bauelementen mit drastisch reduzierten Herstellungskosten erfordert ein Low-cost- und High-Performance-System-Packaging-Konzept. Für HF-Produkte (bis 5 GHz) ist neben präzisen elektrischen Simulationsmodellen auch die Berücksichtigung der dielektrischen Verluste und der durch Prozessvariationen verursachten parasitären Effekte erforderlich.

Um besonderen Bedingungen wie hohen Temperaturen und/oder Integration von Sensoren, z.B. im Automobilbau, gerecht zu werden, werden spezifische Verkappungstechnologien (Molding, Encapsulation) notwendig. Die Verkapselung dient dem mechanischen und optischen Schutz und der elektrischen Abschirmung der aktiven Bauelemente bzw. Komponenten, z.B. Sensoren. Zur Zeit werden bei der Wafer-Level-Verkapselung häufig nur Ein-Chip-Lösungen angewendet. Weitere Entwicklungen im Wafer-Molding erfordern nicht nur Ein-Chip-Lösungen, sondern auch Mehr-Chip-Lösungen, wie z.B. Chipstacks, und die Einbindung von MEMS und MOEMS (Micro Opto-Electro-Mechanical System). Damit entwickelt sich die Wafer-Verkapselung vom einfachen Schutz in ein integriertes, aktives Gehäuse mit zusätzlichen Funktionen, z.B. Mikrolinsen für optische Komponenten, HF-Abschirmung, integrierten Antennen etc. Ein wichtiger Gesichtspunkt der Wafer-Level-Integration sind die passiven Bauelemente mit hohen Güten (Widerstände, Kondensatoren, Induktivitäten etc.). Im Vergleich zur Integration dieser Komponenten in den CMOS-Prozess ist hier die Realisierung auf dem Chip bzw. in das Substrat eine gute Alternative zur nachträglichen Montage zusätzlicher Bauelemente (SMDs). Gleichzeitig spart dies kostbare Leiterplattenfläche und trägt so zur weiteren Miniaturisierung bei.

Ein wichtiger Gesichtspunkt, um die Vorteile des Wafer Level Packaging voll nutzen zu können, ist die Entwicklung geeigneter, kostengünstiger Test- und Burn-In-Verfahren. Zukünftig werden auch auf der Wafer-Ebene dreidimensionale Integrationskonzepte umgesetzt werden. Ein Ansatz ist hierbei der Einsatz von funktionellen flexiblen Polymerlagen, auf denen extrem gedünnte Chips Face-to-Face montiert oder aber auch in Polymerschichten eingebettet werden. Dies schließt auch die Entwicklung und Realisierung von waferprozesstauglichen Energieversorgungskonzepten ein. Das Übereinanderschichten derartiger funktionaler Lagen gestattet damit die Realisie-rung kompletter Mikrosysteme – sog. „e-Grains“ (www.e-grain.org) – auf Wafer-Ebene. Am Ende des Wafer-Prozesses steht ein komplettes funktionierendes Mikrosystem, welches extrem miniaturisiert ist, aber auch kostengünstig in hohen Stückzahlen gefertigt werden kann.

Netzwerk für Hetero-Integrationstechnologien

Sowohl auf dem Substrat-Level als auch auf dem Wafer-Level bestehen noch große Potentiale, anwendungsspezifische, integrierte Hetero-Systeme zu entwickeln, einzusetzen und damit die Grundlagen für innovative Produkte zu legen. Defizite in der Systemintegration bestehen heute darin, dass das Zusammenwirken der Schlüsseltechnologien in den Firmen oft schwach ausgeprägt ist. Die Weiterentwicklung der Einzeltechnologien erfolgt meist unabhängig vom Endanwender.

Insbesondere mittelständische Firmen können sich an der Entwicklung einer Hetero-Systemintegrations-Technologie auch in Zukunft aus Kostengründen nicht maßgeblich beteiligen und sind darauf angewiesen, dass Partner über produktgerechte Technolo-gien verfügen. Insgesamt führt dies dazu, dass Produktentwickler Barrieren bei der Einführung von neuen Systemintegrationstechnologien vorfinden.

Das Vorhandensein neuer Integrationstechnologien kann als ein Träger der Innovation betrachtet werden, der die Attraktivität eines Entwicklungs- und Produktionsstandortes steigert. Aus diesen Gründen ist es notwendig, dass Anwenderindustrie und Technologie-Dienstleister sowie Forschungseinrichtungen auf der Basis einer „Hetero-Integrations-Technologie-Plattform“ als Netzwerk zusammenarbeiten. Dieses Netzwerk aus Industrie, Forschungseinrichtungen und Anwendern sollte eine gemeinsame Technologie-Roadmap für Hetero-Integrations-Technologien definieren und Ziele für zukünftige Forschungsaktivitäten festlegen. Damit wäre auch kleineren Firmen der Zugang zu modernen Hetero-Integrations-Technologien offen.

Diese zunächst auf nationaler Ebene ausgerichtete Plattform sollte eine Strategie auf dem wichtigen Gebiet der Hetero-Integration erarbeiten. Damit könnten Standort- und Wettbewerbsvorteile erzielt und gleichzeitig eine führende Rolle bei dieser wichtigen innovationsentscheidenden Technologie im europäischen Umfeld eingenommen werden.

| Prof. Dr.-Ing. Herbert Reichl studierte Elektrotechnik an der Technischen Universität München. Er ist ordentlicher Professor der Technischen Universität Berlin und leitet den Forschungsschwerpunkt Technologien der Mikroperipherik. 1993 übernahm er die Leitung des Fraunhofer-Instituts für Zuverlässigkeit und Mikrointegration (IZM), Berlin. Er gehört weltweit zu den renommier-testen Wissenschaftlern auf dem Gebiet des Packaging. Für seine herausragenden Leistungen wurde er als IEEE-Fellow ausgezeichnet und im Jahre 2000 mit dem Bundes-verdienstkreuz geehrt. E-Mail: reichl@izm.fraunhofer.de |

| Dipl.-Ing. M. Jürgen Wolf studierte Elektrotechnik an der TU Chemnitz. Nach seinem Abschluss war er mehrere Jahre als Entwicklungsingenieur im Bereich Aufbau- und Verbindungstechnik in einem Industrieunternehmen tätig. Seit 1994 arbeitet er als Projekt- und Gruppenleiter am Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration (IZM), Berlin. Der Schwerpunkt seines gegenwärtigen Arbeitsgebietes liegt im Bereich Flip-Chip-Applikationen und Wafer Level Packaging. E-Mail: wolf@izm.fraunhofer.de |

- Verbessern die Audio-Signalqualität

- Systemintegration auf Wafer-Ebene