Mikroprozessor im FPGA

Symbiose im Chip

Fortsetzung des Artikels von Teil 1

Tools im Überblick

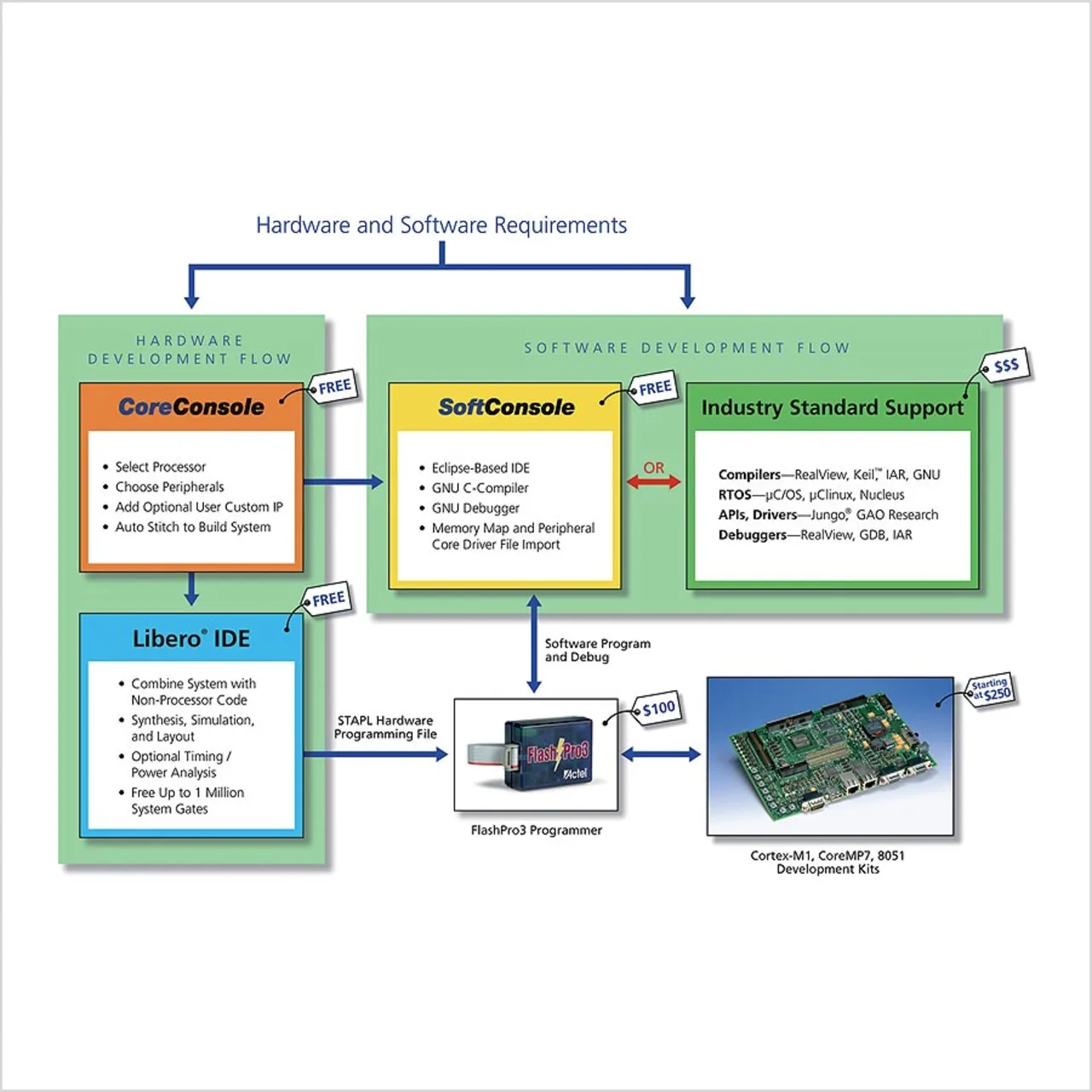

Beim Einsatz eines Prozessors in einer Embedded-Applikation spielt die Verfügbarkeit von Entwicklungswerkzeugen eine wichtige Rolle (Bild 2). Actel steuert die IDP (IP Deployment Platform) »CoreConsole« bei, außerdem die integrierte Entwicklungsumgebung »Libero «, die Programmentwicklungsumgebung »SoftConsole« sowie eine komplette Board-Level-Entwicklungs- und Debugging- Umgebung. ARM unterstützt Cortex-M1 mit der Entwicklungssuite »RealView« und mit dem zugehörigen Mikrocontroller-Entwicklungskit (MDK). Auch Drittanbieter wie Aldec, CriticalBlue, CodeSourcery, IAR, ImpulseC, Mentor Graphics und andere unterstützen den neuen Prozessor mit zahlreichen Tools. Mentor etwa liefert mehrere Plug-&-Play-Designlösungen einschließlich »Design Assembly «, »Embedded Software-Toolsets« und »Precision Synthesis«, ein RTL- und Physical-Synthesis-Tool.

Jobangebote+ passend zum Thema

FPGAs und PSCs für M1

Die für den M1 vorbereiteten Bausteine »M1A3P1000« (ProASIC3) und »M1AFS600« (Fusion) bieten alle Eigenschaften von Actels nichtflüchtigen, Flashbasierten Produktfamilien: Single-Chip-Lösung, Wiederprogrammierbarkeit, Liveat-Power-up, Sicherheit, Resistenz gegen Firm-Errors und geringer Stromverbrauch. Der Fusion-PSC »M1AFS600« mit 600 000 Systemgattern enthält in einem einzigen Baustein einen 12-Bit-A/D-Wandler, 40 Analog-I/Os, bis zu 8 MBit Flash und die FPGA-Architektur. Der Core lässt sich in 4300 »Tiles« implementieren, er nimmt also weniger als 30% des Bausteins ein. Der Baustein »M1A3P1000«, ein Mitglied der Flash-basierten ProASIC3-Familie mit 1 Million Systemgattern, verfügt über 144 KBit SRAM und 300 Digital-I/Os. Der Cortex-M1-Prozessor entspricht ungefähr 20% der FPGA-Logik eines solchen Chips.

Verwandte Artikel:

Wenn mehrere Herzen schlagen

Sind FPGA-Designs sicher?

Autor:

Mike Thompson ist Senior Manager IP and Application Solutions bei Actel. Telefon 0 81 65/95 84 67 www.actel.com

Der Cortex-M1 enthält eine Untermenge der Thumb-2-Architektur mit zwei Betriebsarten: Bei normaler Verarbeitung gelangt man in den »Thread-Modus« über Reset- oder Exception-Return. Während einer Exception befindet sich der Prozessor im »Handler-Modus «. Durch die Begrenzung des Programmiermodells auf zwei Betriebsarten wurde die Komplexität des Prozessors wesentlich reduziert, was die Implementierungskosten senkt.

Der Prozessor ist so aufgebaut, dass Entwickler den Datenfluss und die Verarbeitung im Core steuern können. Dabei müssen sie lediglich dort Kompromisse eingehen, wo es unbedingt erforderlich ist, um die Größe des Prozessors so klein wie möglich zu halten. Dies vereinfacht die Programmierung speziell dann, wenn Teams gleichzeitig Soft- und Hardware entwickeln. Um die Programmierung weiter zu vereinfachen und den Übergang zwischen Thread-Modus und Handler-Modus so reibungslos wie möglich zu gestalten, verfügt der Prozessor über zwei Stacks. Außer dem Reset nutzt der gesamte Programmcode den Haupt-Stack. Ein Exception-Handler kann den vom Thread-Modus benutzten Stack ändern und zwar vom Haupt-Stack zum Process-Stack. Dazu wird der beim Exit verwendete Wert »EXC_RETURN « verändert. Alle Exceptions nutzen dann weiterhin den Haupt-Stack. Der Stack-Pointer (R13) ist ein Banked-Register, das zwischen Haupt-Stack und Prozess-Stack umschaltet.

Entwickler, die mit ARM7 und ARM9 vertraut sind, werden feststellen, dass die Registerdatei ähnlich aufgebaut ist, was der Kompatibilität zum Thumb-Befehlssatz dient. Allerdings ist die Registerdatei weniger komplex und lässt sich in weniger FPGA-Gates implementieren. Zur weiteren Vereinfachung der Programmierung verfügt der Prozessor über eine definierte Memory-Map, auf welche der Core vollständig, also einschließlich Datenbereichen mit allen Datentypen, zugreifen kann. Neben einem externen Interface für den AMBA-Peripheriebus verfügt der Prozessor über eine separate Speicherschnittstelle. Diese Struktur ähnelt jener der ARM9-Architektur, unterscheidet sich aber von der ARM7- Architektur mit kombiniertem Speicher- und Peripheriebus. Die separate Speicherschnittstelle besteht aus zwei Teilschnittstellen, ITCM (Instruction Tightly Coupled Memory) und DTCM (Data Tightly Coupled Memory) (Bild 1). Da der Prozessor bei jedem Taktzyklus einen Befehl über ITCM holen kann und durch Zugriffe auf den Datenspeicher oder durch Lese- und Schreibvorgänge der Peripherie am AMBA-Bus nicht beeinträchtigt wird, ergibt sich ein höherer Durchsatz. In vielen Embedded-Anwendungen, speziell aber in solchen, die in Echtzeit arbeiten, ist eine geringe Interrupt-Latenz entscheidend. Um die Latenz zu verringern, nutzt der Baustein den konfigurierbaren NVIC (Nested Vectored Interrupt Controller), der auch die Behandlung von Exceptions ermöglicht und die Programmierung vereinfacht (Bild 1). Der NVIC unterstützt repriorisierbare Interrupts (die Prioritäten lassen sich individuell bestimmen) auf vier Interrupt-Leveln und ist eng an den Prozessorcore gekoppelt.

- Symbiose im Chip

- Tools im Überblick