Schnittstellen-ICs: Analoge Technik bewegt digitale Inhalte

Fortsetzung des Artikels von Teil 2

BiCMOS contra CMOS

Schnelle Schnittstellen-Bausteine stellen an die Prozesstechnik sehr hohe Anforderungen. Wie zuvor dargestellt, müssen diese Bausteine zuallererst das Rauschen vermindern – und zwar bei Signalen mit Frequenzen weit im Gigahertz-Bereich. CMOS-Transistoren bieten eine hohe Eingangsimpedanz und sind für kurze Schaltzeiten, geringe Leistungsaufnahme und eine kleine Fläche optimiert. Dies ist der Grund für ihre dominierende Rolle in digitalen Schaltungen, in denen die Kosten (d.h. im Wesentlichen die Chipfläche) und die Verlustleistung höchste Priorität haben. Nachteilig an CMOS-Schaltungen ist dagegen das Rauschen. Um die gewünschten hohen Taktfrequenzen zu erreichen, werden die Bauelemente so weit wie möglich miniaturisiert, womit sie jedoch bei gleicher Verlustleistung mehr Rauschen erzeugen als entsprechende bipolare Elemente. Für digitale Logik mag dies hinnehmbar sein, doch beim Ansteuern sauberer Signale oder beim Aufbereiten von Signalen nach beträchtlichen Distanzen ergeben sich Probleme.

Bipolare Schaltungen verhalten sich in vielerlei Hinsicht genau umgekehrt wie CMOS-Schaltungen. Sie nehmen beispielsweise deutlich mehr Leistung auf als CMOS, bringen aber als Hauptvorteile eine größere Verstärkung und einen größeren Signal-Rausch-Abstand mit, was auf die höhere Betriebsspannung und das geringere Rauschen zurückzuführen ist. Angesichts der klaren Forderungen schneller Schnittstellen-Bausteine nach geringer Leistungsaufnahme und niedrigem Rauschen ist BiCMOS die ideale Wahl bei Frequenzen von mehr als 1 GHz. BiCMOS ermöglicht den Einsatz von Bipolar- und CMOS-Transistoren in ein und derselben Schaltung. Wo es auf die Signalintegrität ankommt, kann der Schaltungsentwickler somit rauscharme und schnelle Bipolartransistoren einsetzen, während in allen übrigen Fällen die kleineren, weniger energiehungrigen CMOS-Transistoren bevorzugt werden.

Jobangebote+ passend zum Thema

| A/D-Umsetzer | Takt-Schnittstelle – Jitter-Spezifikation | ||||

| Auflösung | Abtastrate | 1 ps | 0,35 ps | 0,1 ps | 0,05 ps |

8 bit | 1 GSPS | 8 | 8 | 8 | 8 |

| 2 GSPS | 7 | 8 | 8 | 8 | |

| 3 GSPS | 5 | 6,5 | 8 | 8 | |

| 10 bit | 500 MSPS | 8,5 | 10 | 10 | 10 |

| 14 bit | 250 MSPS | 10 | 11 | 13 | 14 |

| 16 bit | 200 MSPS | 10 | 12 | 13,5 | 16 |

| Tabelle 2. Einfluss des Taktsignalrauschens auf den A/D-Umsetzer und die effektive Zahl von Bits (ENOB) | |||||

Der Markt diktiert die Anforderungen an die Prozesse

Im Vergleich zu reinen CMOS- oder Bipolar-Prozessen machen BiCMOSProzesse bestimmte Kompromisse erforderlich. Optimiert man die eine Seite, geht dies zwangsläufig zu Lasten der anderen. Welcher Kompromiss im Einzelfall der beste ist, kann in hohem Maße vom jeweiligen Baustein abhängen. Für die Entwickler schneller Schnittstelllenschaltungen kann es aus diesem Grund sehr sinnvoll sein, wenn ihr Unternehmen über eigene proprietäre Prozesse verfügt. Welchen Nutzen dies in der Tat bringt, lässt sich am BiCMOS8-Prozess von National Semiconductor illustrieren.

Als einer der Pioniere auf dem Analogsektor verfügt National Semiconductor seit den 60er Jahren über analoge Prozesstechnologien. In den 80er Jahren kamen CMOS-Prozesse, in den 90ern dann auch BiCMOS-Prozesse hinzu. Ebenfalls seit sehr langer Zeit betätigt sich National als Entwickler von Schaltungen für sehr hohe Frequenzen – zunächst in den 90er Jahren mit PLLs für Mobiltelefone, in neuerer Zeit dann mit noch höher ausgereizten, rauscharmen Hochgeschwindigkeits-Schnittstellen-ICs. Um den passenden Prozess für einen schnellen Schnittstellen-Baustein zu finden, gilt es zunächst die Anforderungen des Markts zu analysieren. Tabelle 1 fasst die wichtigsten Leistungsvorgaben einiger Anwendungen zusammen. Generell wünschenswert ist stets eine geringe Leistungsaufnahme. Zwar sieht keine der aufgeführten Anwendungen den Batteriebetrieb vor, doch weniger Strombedarf bedeutet geringere Wärmeentwicklung, was wiederum zu kleineren Abmessungen und günstigeren Preisen führt.

Bildgebende medizinische Systeme zum Beispiel verlangen nach Analog/Digital-Wandlern mit Abtastraten von mehreren GSPS (GigaSamples/s), damit die erzeugten Bilder die angestrebte Auflösung erreichen. Damit die Wandler mit maximaler Auflösung arbeiten können, sind sie auf ultrapräzise Taktsignale angewiesen. Hierzu werden hochpräzise Timing-Bausteine verwendet, die das Rauschen aus Quarz-Oszillatoren und Systemtaktquellen ausfiltern. Ein 8-bit-Wandler mit 1 GSPS verlangt beispielsweise ein Taktsignal von 1 GHz mit 1 ps Jitter, damit er seine volle Auflösung von 8 bit erreichen kann (Tabelle 2). Schaltungsdesigner entwickeln aus diesen Applikations-Anforderungen Zielvorgaben für ihre Bauelemente. Sie müssen dabei eng mit den Prozess- Spezialisten zusammenarbeiten, um verstehen zu können, welche Kompromisse möglich sind. Kleinere Prozessgeometrien resultieren in der Regel in weniger Verlustleistung, kleineren Chipflächen und meist niedrigeren Kosten. CMOS-Transistoren mit der Eignung für höhere Frequenzen sind damit ebenfalls möglich. Deshalb gilt bei digitalen Schaltungen meist die Regel: Je kleiner die Prozessgeometrie, desto besser, d.h. desto kleiner, sparsamer und preisgünstiger. Auch aus analoger Sicht bedeutet eine kleinere Prozessgeometrie schnellere Transistoren, aber auch mehr Rauschen, denn die mit stärker miniaturisierten Prozessen einhergehenden niedrigeren Versorgungsspannungen verringern zwangsläufig den Signal-Rausch-Abstand. Für Funktionen wie die spannungsgesteuerten Oszillatoren in Timing-Bausteinen kann dies erhebliche Konsequenzen für das Phasenrauschverhalten haben. Bezüglich der Architektur resultiert hieraus auch eine vermehrte Empfindlichkeit gegen elektrostatische Entladungen.

Sehr anschaulich werden diese Aussagen an „Field Programmable Gate Arrays“ (FPGAs). Wegen ihrer digital dominierten Struktur und ihrer großen Abmessungen werden sie meist mit den höchstentwickelten „Deep-Submicron“- Prozessen produziert. Viele dieser Bausteine unterstützen schnelle Schnittstellen-Standards wie LVDS (Low Voltage Differential Signalling) oder CML (Current Mode Logic), doch sind sie mit dem Nachteil eines mäßigen Rauschverhaltens behaftet, das zum Teil aus den durch benachbarte Kanäle einstreuenden erheblichen Schaltstörungen resultiert. Diese Bausteine kommen deshalb auf niedrigere Übertragungsraten und kürzere Kabeloder Backplane-Distanzen als diskrete analoge Lösungen. Ein weiterer Mangel ist die extrem geringe Immunität gegen elektrostatische Entladungen. Diskrete Schnittstellen-Produkte verkraften hier bis zu 15 kV, doch FPGAs schneiden bis zu einer Größenordnung schlechter ab.

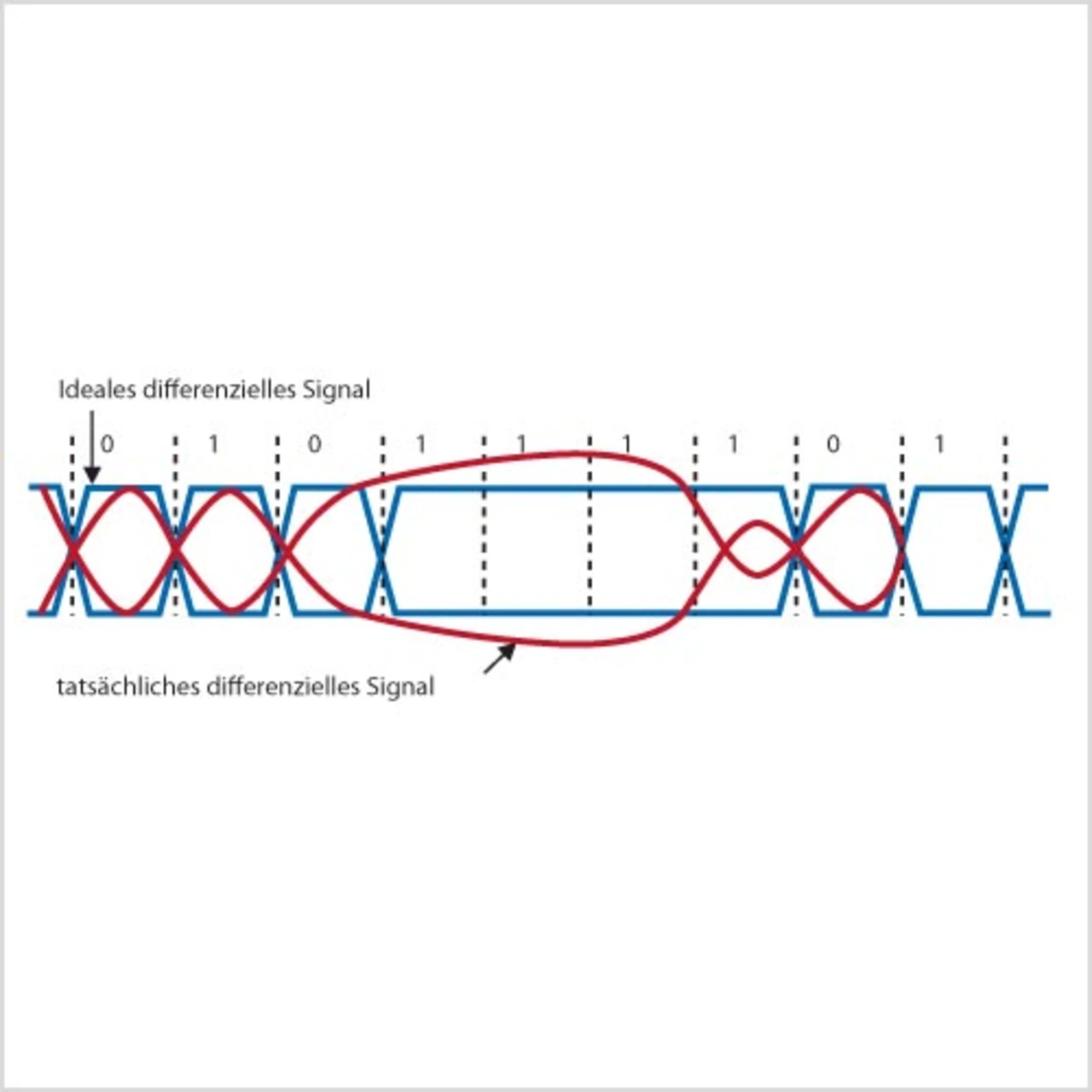

Während die Bits über Kabel, durch Steckverbinder und sogar über Leiterplatten übertragen werden, sind sie störenden Einflüssen ausgesetzt, die gelegentlich so stark sein können, dass kaum noch zwischen digitalen Einsen und Nullen unterschieden werden kann (Bild 2).

Ursachen dieser Störungen können Übersprechen von benachbarten Datenkanälen, Impedanz-Unstetigkeiten durch Steckverbinder oder Dämpfungen infolge nicht idealer Sende- und Empfangs-Schnittstellen sein. Werden diese Störungen nicht bekämpft, führen sie zu einer Zunahme der Bitfehlerraten und damit schließlich zu einer Qualitätsbeeinträchtigung der Video-, Audio- oder Datensignale.

Grundlage für die Verbreitung von Inhalten, mit denen sich die digitale Revolution und die vernetzte Welt für den Endverbraucher materialisieren, ist somit jene Technik, die die Bits auf ihrem Weg an ihr Ziel von störenden Einflüssen befreit. Es mag Techniken – genauer gesagt: schnelle Schnittstellen-ICs – sind, die den schnellen Digitalsignalen den Weg durch dieses rauhe Terrain bahnen. Letztendlich stützt sich diese Schlüsseltechnologie damit auf die vor beinahe 60 Jahren erfundenen bipolaren Transistoren.

Im Wesentlichen wird analoge Technik eingesetzt, um Beeinträchtigungen zu beseitigen, denen die differenziellen Digitalsignale bei der Übertragung mit Datenraten von mehreren Gigabit pro Sekunde und mehr ausgesetzt sind. Senderseitig kommen so genannte Puffer (Buffer) zur Anwendung, die beispielsweise mit einem als „Pre-Emphasis“ (Vorverzerrung) bezeichneten Verfahren die hochfrequenten Anteile der Information verstärken. Dies geschieht in Erwartung der erhöhten Abschwächung, der eben die hochfrequenten Signalanteile auf dem Übertragungsweg unterliegen. Im Empfänger werden so genannte Entzerrer (Equalizer) eingesetzt, die mit ihrer Hochpass-Charakteristik die Tiefpass- Eigenschaften des Kabels ausgleichen und die entsprechende Dämpfung kompensieren. Entzerrer und Puffer schaffen es, die Pegelschwankungen der Bit-Informationen zu reduzieren, doch gegen den Jitter (zeitliche Schwankungen der Signalflanken) sind sie machtlos. Hier sind stattdessen Bausteine zur Rückgewinnung der Takt- und Dateninformationen (Clock/Data Recovery) gefragt, die die ursprüngliche, korrekte zeitliche Beziehung der Bits mit den entsprechenden Taktflanken wiederherstellen (Bild 3).

Man kann sich diese Bausteine wie die Bestandteile eines Signalaufbereitungs-Baukastens vorstellen, welcher mit die höchsten Anforderungen an Hochfrequenz-Analogtechnik stellt. Weitere schnelle Schnittstellen-Produkte wie etwa „Serializer“ (Parallel-Seriell-Datenumsetzung) und „Deserializer“ (Seriell-Parallel-Datenumsetzung) bedienen sich derselben Bausteine. Wieder andere Produkte wie zum Beispiel Taktschnittstellen-Bauelemente stützen sich auf hochfrequente PLL-Schaltungen mit äußerst schmalbandigen Regelkreisen, die den Jitter aus verrauschten Taktsignalen entfernen. Allen diesen Lösungen gemeinsam ist die Forderung, bei möglichst geringem Energiebedarf möglichst viel Rauschen aus hochfrequenten Signalen herauszufiltern.

- Schnittstellen-ICs: Analoge Technik bewegt digitale Inhalte

- Internet-Links:

- BiCMOS contra CMOS

- Schnittstellen-ICs: Analoge Technik bewegt digitale Inhalte