Hardware-Strukturen für eine schnelle, kosteneffektive Verarbeitung von DSP-Algorithmen mit geringer Verlustleistung

Reconfigurable Algorithm Processing

Fortsetzung des Artikels von Teil 1

Die Verbesserungen im Einzelnen

Die Version 2.0 enthält Verbesserungen auf der ALU- und der Tile-Ebene, durch neue Block-RAM-Optionen und durch die Einführung spezieller Multiplizierer und Schieberegister.

ALU-Ebene

Auf der ALU-Ebene zeichnet sich die Version 2.0 durch zusätzliche Befehle und erweiterte I/O-Funktionen aus. Hier einige Änderungen an der ALU:

- Der Subtraktions-Befehl ist jetzt symmetrisch: Da die ALU nunmehr sowohl A – B als auch B – A berechnen kann, verbessert sich die Fähigkeit zum Routen dicht gepackter Multiplizierer und anderer Datenpfad-intensiver Strukturen. Außerdem existiert jetzt für jeden Befehl ein Gegenbefehl, bei dem die Eingänge A und B vertauscht sind, dadurch sind beim Routen zusätzliche Optimierungen möglich.

- Bit-orientierte Logik-Befehle sind durch Befehle mit komplementärem Ausgang ergänzt worden: Die ALU unterstützt jetzt Bit-orientierte NAND-, NOR- und XNOR-Befehle, sodass weniger zusätzliche NOT-Operatoren benötigt werden.

- Neuer „Merge“-Befehl: Damit kann ein Ausgangswert aus einer Kombination von Bits am A- und B-Eingang hergestellt werden, wie z.B. F[i] = L[i] ? A[i] : B[i]. So wird der Bedarf an ALU-Rechenleistung bei der Ausführung von Bit-Manipulationen reduziert.

- Invertierung des „Carry“-Eingangs: Die neu hinzugefügten Befehle „not(cinV)“ and „not(v1w[0])“ erhöhen die Flexibilität des „Carry“-Eingangs. Durch diese zusätzlichen Funktionen verringert sich auch die Zahl der zusätzlich benötigten NOT-Operatoren.

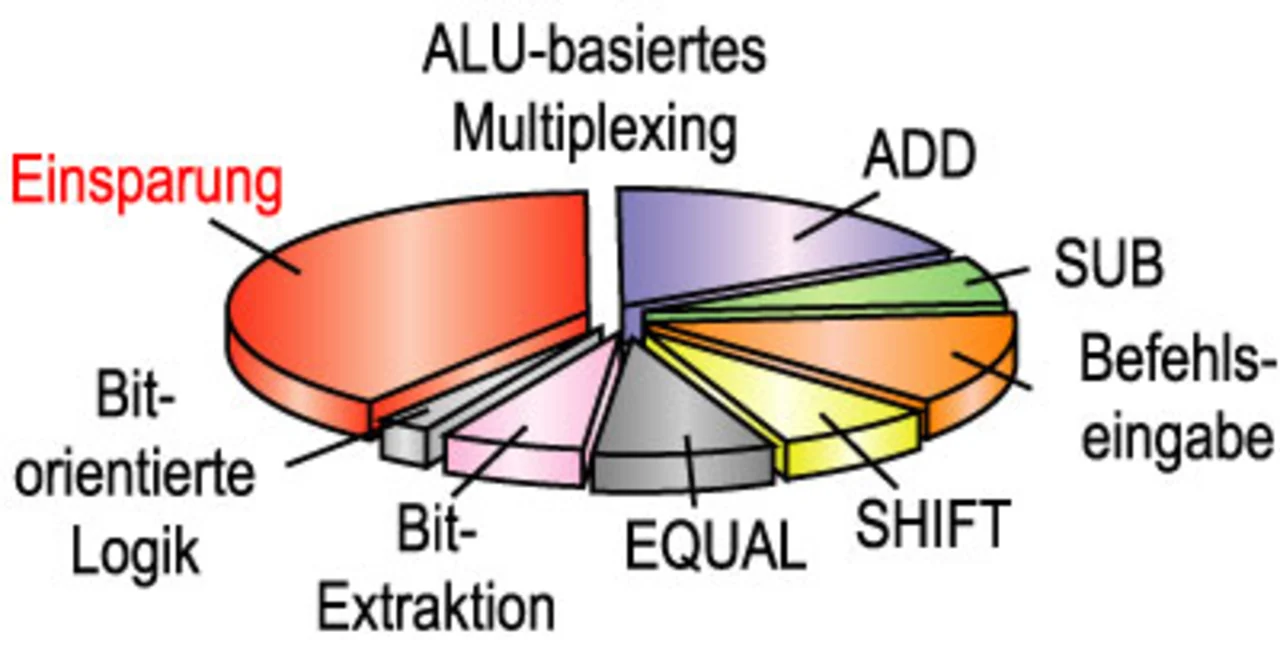

Auch wenn diese Änderungen die Fläche eines „Tile“ geringfügig erhöhen, bewirken sie eine deutlich verbesserte Auslastung der ALU und insgesamt eine Verringerung der Gesamtfläche. Auch ist die Leistungsaufnahme kleiner und die Systemleistung ist größer, da sich bei weniger ALUs der Routing-Aufwand auf dem Array reduziert.

Jobangebote+ passend zum Thema

Verbesserungen auf der Tile-Ebene

Auf der Tile-Ebene ist die Version 2.0 durch Verbesserungen beim „Routing“ und der „Connectivity“ gekennzeichnet. Zusätzlich wurde die Multiplexer-Funktion aufgewertet, um die ALU-Auslastung zu verringern. Die Änderungen auf der Tile-Ebene im Einzelnen:

- Ein schneller „Select“-Pfad wurde hinzugefügt, um die Steuersignale für Multiplexer mit hohem „Fan Out“ aus dem allgemeinen Routing herauszunehmen.

- Die Funktion des „Pattern Matching“ in den Multiplexern wurde modifiziert, indem ein ALU-Befehl OR/AND zur Auswahl-Eingangslogik (Select) der Multiplexer hinzugefügt wurde. Die Verwendung der Multiplexer ermöglicht es, das „Pattern Matching“ aus dem Haupt-Datenpfad der ALU herauszunehmen.

- Neu zugeordnete Switches an den Multiplexer-Ausgängen ergeben bessere Verbindungen zwischen Multiplexer und ALU sowie von einem Multiplexer zum anderen.

Insgesamt bewirken diese Änderungen eine Verbesserung der Packungsdichte der Tiles und eine verringerte Auslastung der ALU. Außerdem reduziert sich die Routing-Laufzeit gegenüber der Version 1.2. Auf Array-Ebene lassen sich mit der Version 2.0 neue und verbesserte Hardware-Funktionsblöcke einsetzen, die entweder am Rand hinzugefügt oder in das Array eingebettet werden können.

Neue Block-RAM-Optionen

In der Version 1.x ist das eingebette-te Block-RAM mit herkömmlichen SRAMs realisiert. In der Version 2.0 kommen mehrere RAM-Optionen hinzu, mit denen das Array auf eine Maximierung der Leistung und der Dichte für potentielle Anwendungen abgestimmt werden kann. Zu den Optionen gehören:

- „Dual Port RAM“: Um höhere Geschwindigkeiten beim „Pipelining“ und anderen Daten-Flows zu ermöglichen, unterstützt die Version 2.0 in das Array eingebettetes Dual Port RAM. Damit ist in jedem Zyklus ein Lese- und ein Schreibzyklus (von/nach verschiedenen Adressen) möglich.

- „Split ROM“: Im Interesse einer besseren Auslastung der 4-bit-ALU-Architektur bietet die Version 2.0 Unterstützung für ein in das Array eingebettetes „Split ROM“. Damit ist das Lesen von 4-bit-Daten pro Zyklus (von verschiedenen Adressen) möglich.

- Eingebettete Schieberegister (Shifter): Als Hilfestellung für Arithmetik-intensive Operationen unterstützt die Version2.0 eingebettete Schieberegister. Über die RAM-Schnittstellen wird ein Schieberegister mit variabler Schiebeweite an das Array angeschlossen.

Spezielle Multiplizierer und Schieberegister

D-Fabrix kann in das Array eingebettete Multiplizierer und Schieberegister unterstützen. Um ein Maximum an Leistung und Dichte zu erzielen, können jedoch auch spezielle Hardware-Multiplizierer und -Schieberegister verwendet werden. Die Version 2.0 unterstützt beide Arten von Hardware-Ressourcen, entweder eingebettet oder an den Rand des Arrays angeschlossen. Im Falle des Schieberegisters ist die Verzögerungszeit unabhängig von der Schiebeweite. Durch das Hinzufügen eines Schieberegisters als Ressource verbessert sich auch die Leistung der ALU-basierten Multiplizierer.

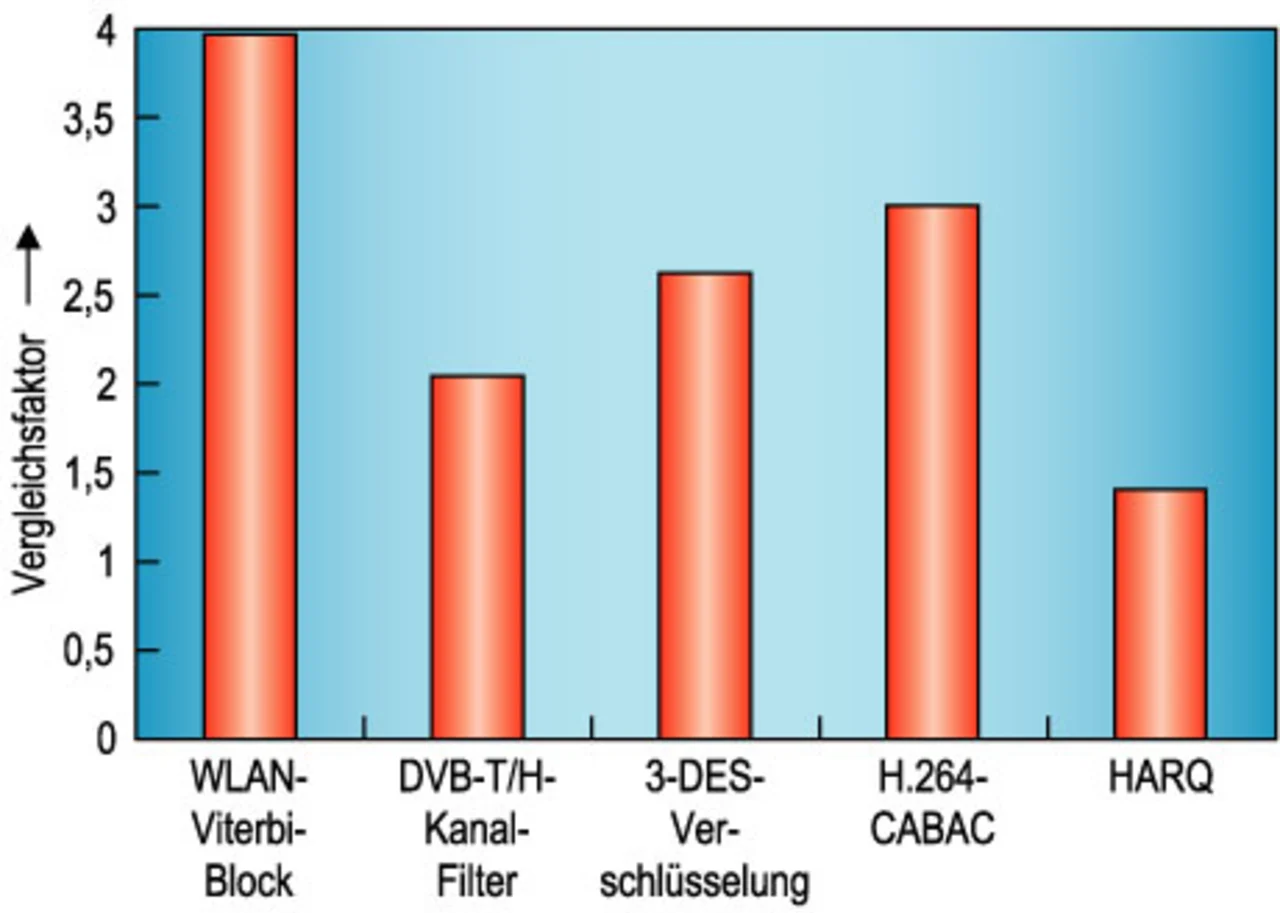

Vorteile der neuen Architektur

| Ralph Weir studierte an der schottischen Strathclyde University und war danach in Entwicklung und Marketing und Business Development bei Texas Instruments und Motorola Semiconductors im Bereich der digitalen Signalprozessoren (DSP) tätig. Nach einer Tätigkeit als Director of Marketing bei der Firma Blue Wave Systems bekleidete er die Position eines Directors Sales & Marketing für die Firma Hunt Engineering, ein auf DSP-Systeme spezialisiertes Unternehmen. 2001 trat er in das Unternehmen Elixent ein, wo er als Director of Technical Marketing wesentlich zur Markteinführung der „rekonfigurierbaren Logik“ beitrug. E-Mail: ralph.weir@elixent.com |

Verwandte Artikel:

- Reconfigurable Algorithm Processing

- Die Verbesserungen im Einzelnen