Programmierbare Chips sollen ASICs, FPGAs und ASSPs ablösen

Fortsetzung des Artikels von Teil 1

Hardware-Multithreading ohne Reibungsverluste

Um unter Echtzeit-Bedingungen funktionieren zu können, wird, anders als man es z.B. von PC-Betriebssystemen kennt, das Multithreading auf Hardware- Ebene realisiert. Jeder Core kann bis zu acht Threads ausführen und den Kontext bei jedem Taktzyklus wechseln. Obwohl XMOS hierzu noch keine Details veröffentlicht hat, ist davon auszugehen, dass für jeden Thread ein eigener Registersatz vorgehalten wird, zwischen denen über einen Zeiger gewechselt wird. Nur so kann ein Thread- Wechsel ohne Zeitverlust für das Speichern und Laden der Register funktionieren. Die Threads werden nach einem Round-Robin-Verfahren gewechselt, wobei die Rechenzeit – anders als z.B. beim Mips 74K, wo Thread-Prioritäten programmtechnisch festgelegt werden können – symmetrisch verteilt wird. Bei acht Threads pro Core bekommt somit jeder Thread 12,5 Prozent, bei vier entsprechend 25 Prozent. Durch die Software-Steuerung ist es möglich, Rechenlasten und Thread- Zuweisungen dynamisch zur Laufzeit zu verändern. Wenn beispielsweise eine Anwendung eine I/O-Schnittstelle für eine bestimmte Zeitspanne nicht benötigt, kann der Thread einer anderen Aufgabe zugewiesen werden. Eine I2C-Schnittstelle könnte etwa temporär durch den Wechsel eines Gerätetreibers in einen UART verwandelt werden.

Jobangebote+ passend zum Thema

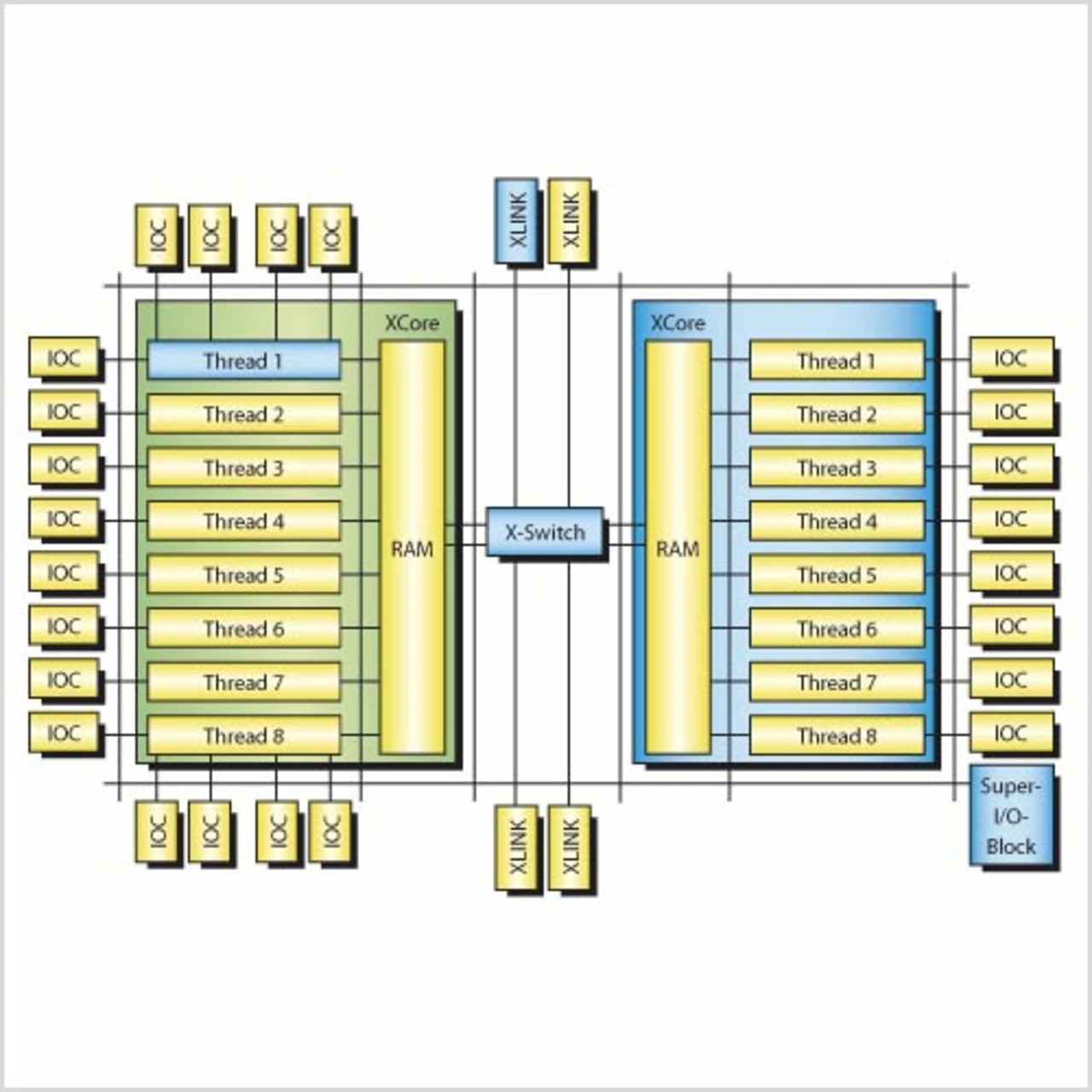

Die ersten Cores sollen eine Rechenleistung von 500 MIPS aufweisen, was pro Thread 62,5 MIPS entspricht. Das sollte für die Implementierung einer 100 -Mbit/s-Ethernet-Schnittstelle oder sogar einer 480-Mbit/s-USB-2.0- Schnittstelle ausreichen. Bei DSP-Anwendungen würde ein FIR-Filter 16. Ordnung über 7 Mio. Samples pro Sekunde verarbeiten können. Einige Anwendungen werden trotzdem mehr Rechenleistung benötigen, als sie von einem einzigen Core bereitgestellt werden kann. In diesen Fällen können mehrere Cores über eine proprietäre, XLink genannte Verbindungstechnologie zusammengeschaltet werden. XLink-Netzwerke können mehrere Threads auf einem Core, mehrere Threads auf mehreren Cores oder sogar mehrere Threads auf unterschiedlichen Chips koordinieren (Bild 2). Der compilierte Code ist positionsunabhängig, so dass Entwickler nicht wissen müssen, auf welchem Core welcher Thread läuft – die Verteilung der Threads erfolgt zur Laufzeit. Allerdings können Programmierer auch manuelle Zuweisungen vornehmen, um zum Beispiel Überlastungen eines Cores zu verhindern. XLink umfasst ein logisches Protokoll, das auf unterschiedlichen physikalischen Schichten aufbaut. Die XMOS-Entwicklungswerkzeuge müssen daher Netzwerk- Latenzzeiten einkalkulieren, wenn sie die Threads intelligent verteilen wollen.

Systemblibilotheken unterstützen I/O-Schnittstellen

Ob sich XMOS mit dieser Technologie am Markt durchsetzen kann, wird von mehreren Faktoren abhängen. Die erste Frage stellt sich nach der Unterstützung durch Entwicklungswerkzeuge. Eine Hürde ist sicherlich XC. Entwickler verweigern sich in der Regel herstellerspezifischen Spracherweiterungen, speziell wenn sie diese Erweiterungen an eine proprietäre CPU-Architektur eines Startup-Unternehmens bindet. XMOS hat dies erkannt und entwickelt deswegen Systembibliotheken mit Gerätetreibern und I/OSchnittstellen in XC, so dass die Entwickler den größten Teil ihres Codes in C oder C++ schreiben können. Zudem hofft XMOS, einige bei SoC-Entwicklern besonders beliebte Software- Bibliotheken in XC portieren zu können. Eine weitere Frage stellt sich nach der Qualität der Entwicklungswerkzeuge, die für viele Kunden wichtiger ist als die Leistungsmerkmale der Hardware.

Für XMOS spricht der Trend, immer mehr Funktionen von der Hard- in die Software zu verschieben. Je leistungsfähiger Prozessoren werden, desto einfacher wird es, I/O-Funktionen, die vor noch nicht allzu langer Zeit in Hardware abgebildet werden mussten, in Software zu emulieren. Des weiteren werden die Lebenszyklen vieler Produkte immer kürzer und lassen sich statt in Jahren nur noch in Monaten messen. Die Folge ist, dass sich zunehmend die Frage stellt, ob die Produkte die notwendigen Verkaufszahlen erreichen, um die hohen Hardware- Entwicklungskosten wieder einzubringen. Weiterhin kann ein Produkt durch die enorme Geschwindigkeit der Weiterentwicklung sehr schnell veraltern. Der Zeitpunkt, zu dem es am Markt nicht mehr verkäuflich ist, lässt sich hinausschieben, wenn man I/OSchnittstellen sogar noch zur Laufzeit verändern kann.

Die Prognose für XMOS hängt im Wesentlichen davon ab, wie gut die Firma ihre Strategie in die Tat umsetzen kann. Hierfür sind die Qualität der Multicore- Integration, die Unterstützung durch die Entwicklungswerkzeuge, die Akzeptanz der erweiterten C-Sprache und der Umfang und die Qualität der mitgelieferten Systembibilotheken entscheidend.

Frank Riemenschenider, Elektronik

- Programmierbare Chips sollen ASICs, FPGAs und ASSPs ablösen

- Hardware-Multithreading ohne Reibungsverluste