Basisband-Downlink-Lösungen mit einem kleinen FPGA auf den neuesten Stand bringen

Plattform-FPGAs für drahtlose Basisstationen #####

Fortsetzung des Artikels von Teil 1

Lebensverlängerung der gegenwärtigen Basisstationen

In dem Maße, in dem die Industrie bei drahtloser Kommunikation die Kosten senken und gleichzeitig Leistungsmerkmale verbessern will, ist sie vor schwierige Entscheidungen gestellt. Sie muss die für neue Eigenschaften erforderlichen Funktionen auf verfügbare Technologien abbilden, vorhandene IPs aufarbeiten, das Risiko neuer Lösungen abschätzen und versuchen, Risiko und Ungewissheit durch Flexibilität zu mindern. Allerdings ist das ideale Szenario eines geschlossenen Sprungs hin zur voll flexiblen Lösung einer Verteilung auf DSPs und FPGAs nicht immer möglich.

Ein gangbarer Zwischenschritt könnte darin bestehen, diskrete Bauteile in der Umgebung existierender ASICs anzusiedeln, die ihrerseits neue Funktionen unterstützen, die sich auf andere Weise weder zeitgerecht noch kosteneffektiv ergänzen lassen.

So hat z.B. das 3GPP-Konsortium, das für die technische Spezifikation von W-CDMA verantwortlich ist, Mitte 2002 das Release 5 herausgegeben. Dieses umfasst mit HSDPA (High Speed Downlink Packet Access) eine neue obligatorische Funktion, die einen breitbandigen Kanal für gemeinsam genutzte Daten in die physikalische Schicht einführt. ASICs für Release 4, die gegenwärtig in W-CDMA-Basisstationen Verwendung finden, stellen indes nur eine begrenzte Verarbeitungsleistung zur Unterstützung von HSDPA zur Verfügung. Damit steht die Herausforderung im Raum, wie diese Muss-Funktion von Release 5 bei gleichzeitig steigendem Kostendruck implementiert werden kann.

Bestehende Basisband-Downlink-Lösungen kann man mit einem kleinen und billigen FPGA „hochrüsten“. Die dafür notwendige HSDPA-IP ist aus diversen Referenzdesigns erhältlich, die von einem kleinen, eigenständigen Symbolrate-Prozessor für HS-DSCH bis hin zur kompletten Downlink-Lösung reichen, die Symbolraten- und Chipraten-Verarbeitung für HS-DSCH und HS-SCCH bieten. Dabei lässt sich die HSDPA-Downlink-Lösung leicht mit einem vorhandenen Hostprozessor für Release 4 koppeln. Wenn dann noch vorher dafür gesorgt wurde, dass die Verarbeitungs-Latenz extrem niedrig ist, dann dürfte das Risiko für die vorhandene Software der Steuerebene sehr niedrig ausfallen.

Dieser Ansatz liefert eine billige, risikoarme und stromsparende Lösung für die Herausforderung einer Anpassung an den Funktionsumfang von Release 5. Er kann aber auch als Zwischenschritt für die Unterstützung künftiger Releases 6 und 7 gesehen werden, denn die IP lässt sich vollständig auf die FPGAs der nächsten Generation portieren. Ein Blick auf die Leistungsmerkmale, die für künftige W-CDMA-Releases im Gespräch sind, zeigt nämlich, dass eine steigende Komplexität der Algorithmen mit Sicherheit mehr Verarbeitungsbandbreite benö-tigt, die gewählte Plattform aber immer weniger kosten darf.

Jobangebote+ passend zum Thema

Entwürfe für Basisstationen der nächsten Generation

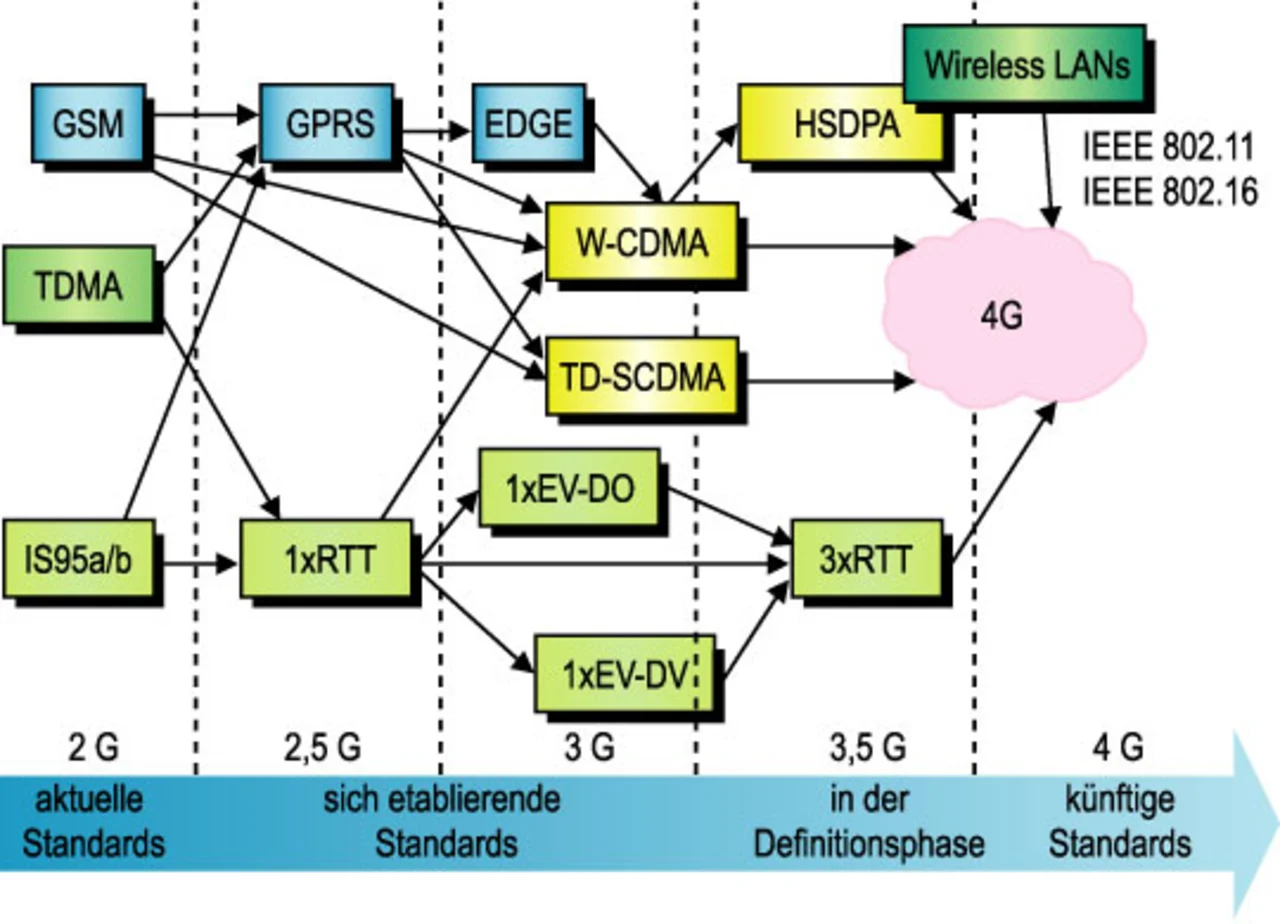

Die Ergänzung bestehender ASIC-Lösungen um externe Bauteile zur Hochrüstung auf neue Funktionen kann nur eine Notlösung sein. Künftige Entwicklungen für Basisstationen müssen flexibler gestaltet werden, wenn sie schnell an veränderte Kundenanforderungen angepasst werden und darüber hinaus die zu erwartende Konvergenz von Mobilfunk und breitbandigen drahtlosen lokalen Netzen beherrschen sollen. Wie in Bild 2 zu sehen ist, bietet die Roadmap der mobilen Technologien eine Vielfalt an Lösungen, sodass Basisstationen aus einer gemeinsamen programmierbaren Plattform viele Vorteile ziehen könnten. Darüber hinaus werden aktuelle Techniken wie Multi-User-Erkennung und Antennenauswahl durch neue technische Herausforderungen wie Kanalbereitstellung und Abstimmung der Basisstation ergänzt, mit denen die Kapazität vergrößert, gleichzeitig aber der Einfluss auf die Dienstequalität (QoS) verringert wird.

Wenn es um Flexibilität geht, sind FPGAs die logische Konsequenz. Außerdem bieten sie durch die Herstellung mit modernen Fertigungstechnologien wie 90-nm-Geometrie auf 300-mm-Siliziumwafern attraktive Preisvorteile, die den aktuellen Erwartungen eines reifen Marktes der drahtlosen Netzkommunikationstechnik entgegenkommen.

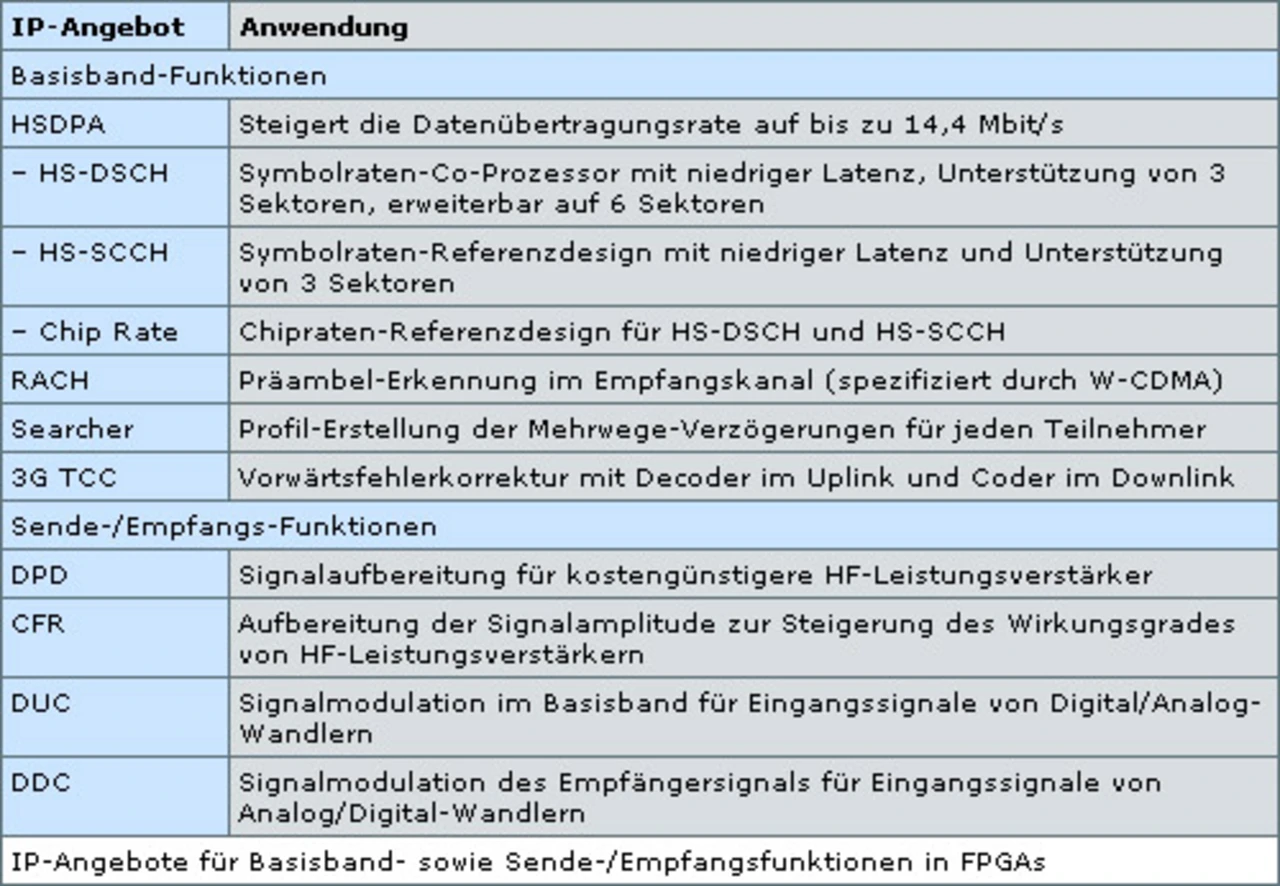

In der Tabelle ist eine Auswahl an IP-Angeboten für Funktionen im Basisband und der Sende/Empfangseinheit zusammengestellt. Dabei sind die genannten Angebote lediglich als Beispiel dafür anzusehen, was möglich ist; sie berücksichtigen ferner, dass Hersteller drahtloser Systeme und Komponenten die Kontrolle über ihre eigenen Verarbeitungsalgorithmen behalten wollen. Auch wenn reife Märkte nach einer Standardisierung verlangen, werden proprietäre Algorithmen als wichtige Differenzierungsmerkmale angesehen, die einen Wettbewerbsvorteil im Basisband und einigen Bereichen des digitalen HF-Moduls bieten.

Während alternative Lösungen wie DSPs und programmierbare ASSPs für sich auch Flexibilität in Anspruch nehmen, lohnt es sich festzustellen, dass FPGAs weiterhin die Technologiekurve bestimmen und vom niedrigen Preisniveau der 65-nm- und 45-nm-Geometrien auf 300-mm-Wafern profitieren dürften. Dieser Roadmap der Kostensenkung ist durch alternative Lösungen immer schwerer zu folgen, da sie es nicht schaffen dürften, die Fertigungskosten einer tiefen Submikron-Technologie über ein breites Spektrum an Anwendungen auf vielen Märkten zu amortisieren.

Leistungsbedarf sinkt trotz kleinerer Prozessstrukturen

Für drahtlose Modems mit ihrem gesteigerten spektralen Wirkungsgrad und höheren Datenraten muss die Komplexität der Algorithmen und die Verarbeitungsbandbreite entsprechend wachsen. Dies verlangt nach höheren Taktraten auf Systemebene oder neuen Parallelverarbeitungsarchitekturen, die am ehesten durch feinere Bauteilgeometrien erreichbar sind. Eine gängige Auffassung in der Industrie lautet nun: Wegen der höheren Transistor-Leckströme bei kleineren Silizium-Prozessgeometrien steigt der statische Leistungsbedarf. Dies dürfte im Allgemeinen zwar zutreffen, nicht aber bei führenden Plattform-FPGAs. Denn deren statische und dynamische Verbrauchswerte haben sich – trotz Skalierung von 130 nm auf 90 nm – um 50 Prozent reduziert.

Die genannten Hardware-Eigenschaften können allerdings erst durch Entwicklungswerkzeuge wie „System Generator for DSP“ effizient genutzt werden. Mit diesem Tool können Schaltungsdesigner DSP-Designs für drahtlose Basisstationen wesentlich schneller entwickeln. Viele Designer bedienen sich dabei der Matlab/Simulink-Entwicklungsumgebung, in der sich Design-Abstraktionen auf Knopfdruck automatisch in FPGA-Plattformen mit der gleichen Performance wie bei vorliegenden VHDL-Beschreibungen compilieren lassen. Sie können dabei auch Beschleuniger mit ergänzenden Universal- und DSP-Prozessoren ankoppeln, die gerne für Funktionen auf der Steuerungsebene von drahtlosen Basisstationen eingesetzt werden.

Für mehr Informationen über Xilinx-Lösungen für drahtlose Kommunikation, Schlüsselmärkte und Endanwender lohnt sich ein Besuch von www.xilinx.com/esp/. Ein Link zu Details über FPGAs der Serie Virtex-4 ist www.xilinx.com/ virtex4/, während dsp>www.xilinx.com/dsp mehr Einzelheiten über den System Generator for DSP und IPs bezüglich DSPs bereit hält.

| David Gamba arbeitet als Senior Marketing Manager seit 2004 bei der Strategic Solutions Marketing Group von Xilinx. Zuvor war er acht Jahre lang bei Firmen wie Aeluros, Conexant and Altera mit verschiedenen Marketing- und Verkaufspositionen betraut. Er hat einen Bachelor’s Degree in Electrical Engineering der UCLA, einen Master’s Degree in Electrical Engineering and Computer Science von UC Berkeley und einen MBA Degree der Stanford University erworben. E-Mail: david.gamba@xilinx.com |

Verwandte Artikel:

- Plattform-FPGAs für drahtlose Basisstationen #####

- Lebensverlängerung der gegenwärtigen Basisstationen