Integrierte Elemente überwachen die Zuverlässigkeit

Lebensdauer-Monitoring auf dem Chip

Fortsetzung des Artikels von Teil 1

Zustandsabhängige Wartungskonzepte

Bisher wurden Bauteile in kritischen Anwendungen nach festgelegten Zeitintervallen ausgetauscht. Nun ist es möglich, solche Bauteile genau dann auszuwechseln, wenn das Ende der Lebensdauer erreicht ist. Die Kosten für die Wartung von sicherheitsrelevanten Anlagen und Geräten können damit erheblich reduziert und optimiert werden.

Viele Anlagen in sicherheitsrelevanten Anwendungen werden vorbeugend nach einem festgelegten Wartungsplan gewartet. Dabei werden Module, die für die Sicherheit der Anwendung wichtig sind, nach einer festgelegten Betriebsdauer vorzeitig ausgewechselt. Demgegenüber erlaubt die „Sentinel Silicon“-Technologie das zielgerichtete Auswechseln von Modulen nach Bedarf im Rahmen eines zustandsabhängigen Wartungsplans. Der Zustand eines Moduls wird unter Verwendung der Informationen aus den „Sentinel Silicon“-Zellen ermittelt. Abhängig vom Ergebnis wird das Modul ausgewechselt. Die Wartungsabstände können damit erheblich verlängert werden, ohne die Sicherheit der Anwendung zu gefährden. Module werden nur dann ausgetauscht, wenn es notwendig wird.

Ein Vorteil dabei ist, dass Bauelemente, die durch andere Einwirkungen oder ungünstige Betriebsbedingungen schneller gealtert sind, dennoch rechtzeitig ausgewechselt werden können. Auch in sicherheitsrelevanten Anwendungen ist damit eine deutliche Erhöhung der Standzeit möglich. Die Verwendung von zwei oder mehreren redundanten Modulen, um in jedem Fall ein funktionierendes Modul zu haben, ist nicht notwendig. Ältere Module oder Ersatzteile, die bereits in Betrieb waren, können nach ihrer noch zur Verfügung stehenden Lebensdauer qualifiziert werden und wieder einer geeigneten Verwendung zugeführt werden.

Jobangebote+ passend zum Thema

Prognose für verschiedene Fehlermechanismen

Die „Sentinel Silicon“-Technologie beruht auf der Anwendung von Designprinzipien für den Entwurf von Teststrukturen, die Fehlermechanismen wie dielektrischen Durchbruch, Elektromigration etc. gezielt beschleunigen können. Diese Teststrukturen sehen während der Betriebsdauer die gleichen Umgebungsbedingungen wie die Schaltung auf dem Bauelement. Dadurch ist eine rechtzeitige Prognose von Ausfällen gewährleistet. Die Entwurfsparameter werden so gewählt, dass eine vorher bestimmte und kalibrierte Ausfallcharakteristik der Teststruktur erreicht wird. Ein Ausfall der Teststruktur zeigt dann eine bestimmte noch zu erwartende Lebensdauer an. Durch die unterschiedlich gestalteten, nebeneinander liegenden Teststrukturen können mehrere Zeitfenster und Fehlermechanismen gleichzeitig abgebildet werden. Die „Sentinel Silicon“-Zellen umfassen speziell auf den Halbleiterprozess abgestimmte aktive und passive Halbleiterstrukturen (Hard Macros) und werden innerhalb des aktiven Chip-Bereiches plaziert. Die IP (Intellectual Property) wird als komplettes Paket zur Integration in industrieübliche Tools für das Halbleiterdesign geliefert. Die gesamte Zelle ist bei Fertigung in einem 0,25-µm-CMOS-Prozess etwa 150 µm2 groß.

Es sind verschiedene Zellen verfügbar, die speziell die Einflüsse von elektrischer Aufladung und Einstrahlung (ESD), von Elektromigration, heißen Ladungsträgern sowie radioaktiver Strahlung erfassen können. Die Ausgänge können in bestehende JTAG-Ketten integriert werden, so dass die Zellen auf einfache Weise innerhalb einer BiST-Routine ausgelesen werden können. Damit kann der Nutzer die Information zu jedem gewünschten Zeitpunkt abrufen.

| Dr. Eckardt Bihler hat langjährige Berufserfahrung in der Anwendung von Mikroelektronik in Industrie, Telekommunikation und Computer. Nach dem Studium der Festkörperphysik an der Universität Stuttgart war er bei IBM in Entwicklung und Produktion tätig. 2001 hat er Forturex gegründet, eine Marketing- und Vertriebsfirma für innovative Halbleitertechnologien und das Design von kundenspezifischen Bauelementen. E-Mail: eckardt.bihler@forturex.com |

| Doug Goodman ist Chairman von Ridgetop Group, Inc., und hat mehr als 25 Jahre Erfahrung im Design rauscharmer Elektronik für die Messtechnik und in der Entwicklung von Werkzeugen für das IC-Design, u.a. bei den Firmen Tektronix, Delco Systems, Bunker Ramo Corp., Analogy, Opmaxx und Fluence Technology. Während seiner Tätigkeit in der Laboratory Instrument Division von Tektronix war er Mitglied des Patent-Komitees und zudem eine Zeit lang außerordentliches Mitglied der Fakultät der University of Arizona in Tucson. Er hat einen BS in Electronic Engineering an der California Polytechnic State University, San Luis Obispo, erworben und den Master an der University of Portland. E-Mail: doug@ridgetop-group.com |

| Dr. Bert Vermeire ist als Chief Technical Officer (CTO) bei Ridgetop Group, Inc., verantwortlich für den Bereich Forschung und Entwicklung. Zuvor hat er als Chefentwickler wichtige Projekte zur Entwicklung fortschrittlicher Halbleiterprozesse und der BiST-Technologie sowie für den Schutz elektronischer Bauelemente vor radioaktiver Strahlung (radiation hardening) geleitet. Nach seinem Aufenthalt am IMEC in Belgien hat er den PhD an der Universität von Arizona, Tucson, erworben; er ist Autor von 27 technischen Veröffentlichungen. E-Mail: vermeire@ridgetop-group.com |

Verwandte Artikel:

Folgende Anwendungen werden hier näher erläutert:

- Warnung vor dem Ende der Lebensdauer („Wear Out“),

- Prozess- und Lebensdauer-Monitoring für kontinuierliche Qualitätskontrolle,

- Monitoring von kritischen Schädigungen durch ESD.

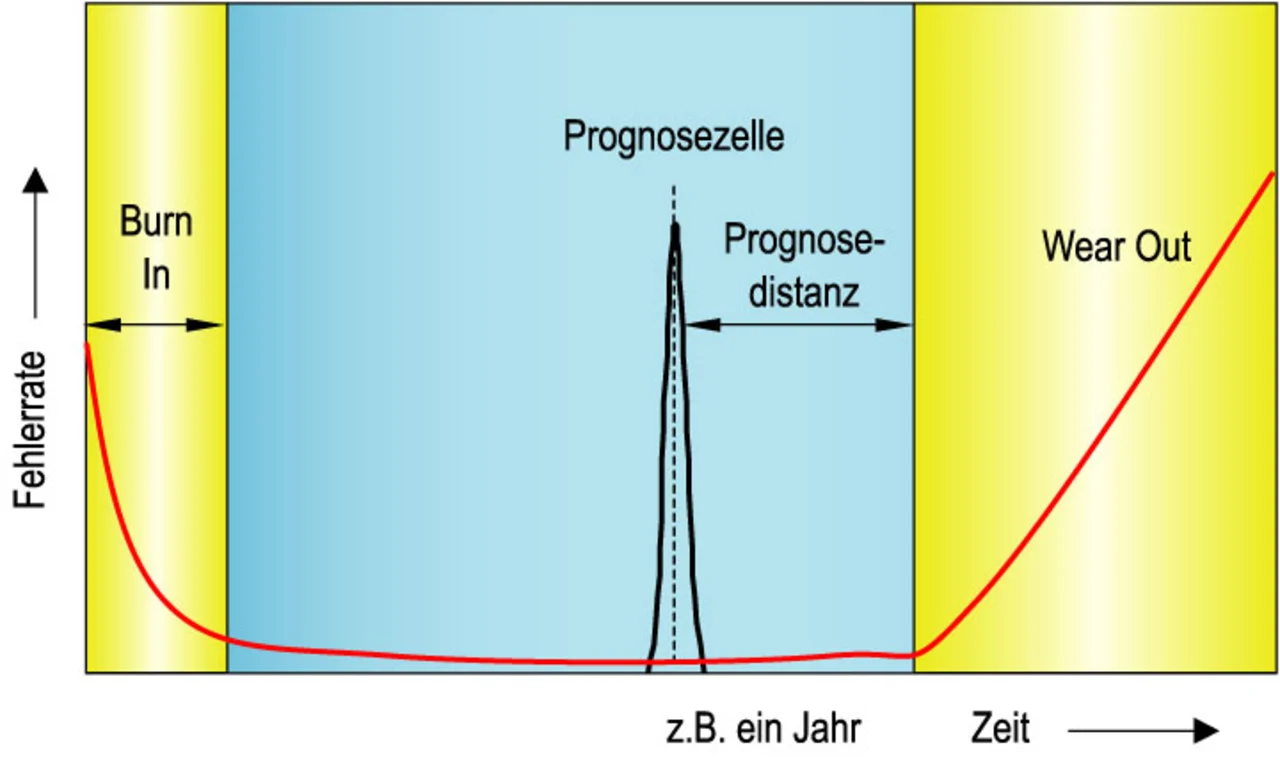

Die „Sentinel Silicon“-Technologie verwendet spezielle, im Chip integrierte Prognose-Zellen, um eine Vorhersage über die noch zur Verfügung stehende individuelle Lebensdauer eines Halbleiterbauelements zu erhalten. Diese Prognose-Zellen degradieren schneller als die restliche Schaltung und lassen sich damit zur Prognose der Alterung verwenden (Bild 2). Die Zeitdifferenz zwischen dem Ausfall der Prognose-Zelle und dem Einsetzen des „Wear Out“ wird als Prognose-Distanz bezeichnet. Diese kann in einem weiten Zeitbereich durch geeignete Wahl der Entwurfsparameter der Prognose-Zelle eingestellt werden. Mehrere Zellen mit unterschiedlichen Prognose-Distanzen können eingesetzt werden, um eine genauere zeitliche Auflösung der noch zur Verfügung stehenden Lebensdauer zu erreichen. Zur Kalibrierung der Prognose-Zellen werden Daten über den Ablauf der Alterungsprozesse für die verwendete Prozesstechnologie verwendet. Die Prognose-Zellen müssen jeweils auf den verwendeten Herstellungsprozess abgestimmt werden.

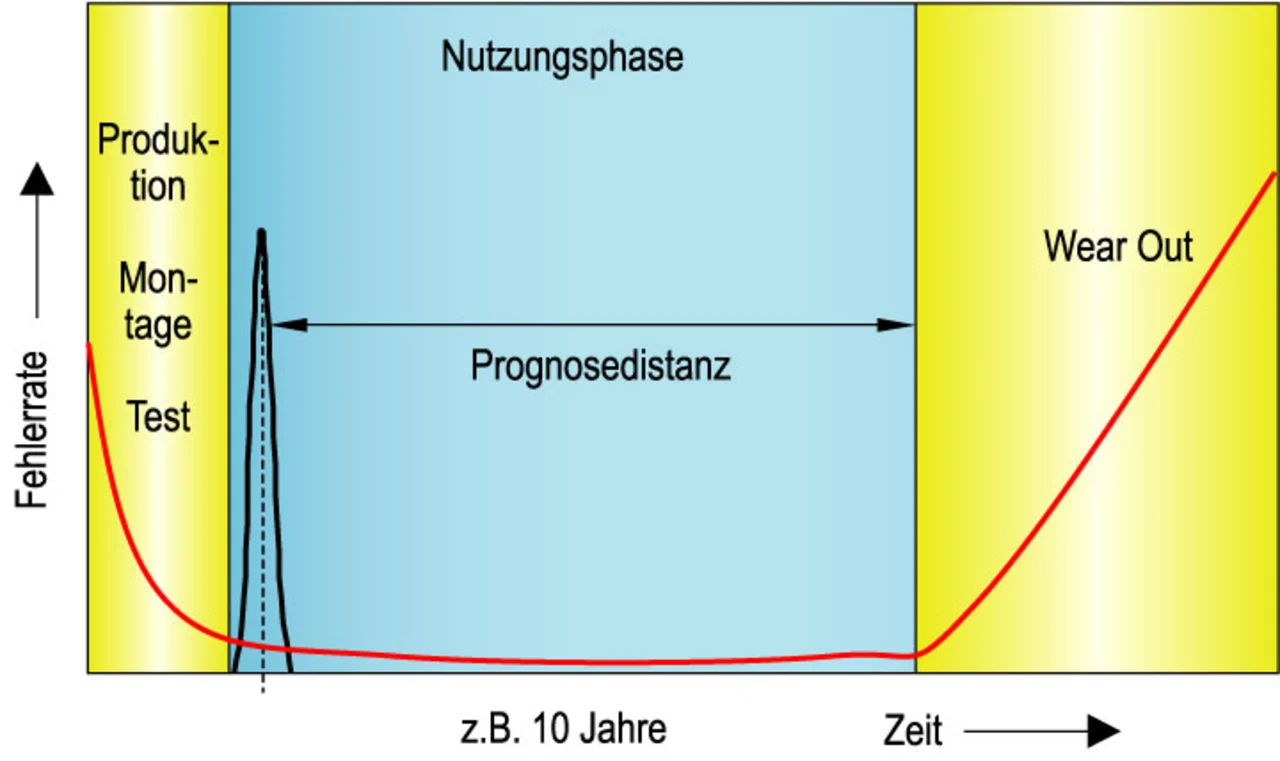

Wird die Prognose-Distanz in den Bereich der mindestens zu garantierenden Lebensdauer für ein Bauelement verschoben, dann ist dies ein wirksamer Monitor zur laufenden Kontrolle und Absicherung einer Mindestlebensdauer für jedes einzelne hergestellte Bauelement (s. Bild 3). Im Gegensatz zu den bisher hierfür eingesetzten Monitoren auf Halbleiterscheiben in der Produktion sind die „Sentinel Silicon“-Monitore in das Bauelement integriert und können zu jedem späteren Zeitpunkt ausgelesen werden, auch wenn eine direkte Kopplung mit der Halbleiterproduktion nicht mehr oder nur noch mit Aufwand herstellbar ist. Das hier vorgestellte Konzept des Monitorings kann insbesondere auch von den Herstellern in der Verwertungskette nach dem Halbleiterhersteller wirksam genutzt werden, z.B. von Systemherstellern, Herstellern ohne eigene Halbleiterproduktion (fabless) oder EMS (Electronic Manufacturing Services). Der Verlauf der Ausfallrate von Prognose-Zellen in Bauelementen, die einwandfrei hergestellt wurden und keine Beeinträchtigungen erfahren haben, ist in Bild 3 dargestellt. Diese Prognose-Zelle war zu allen Zeitpunkten in den Arbeitsschritten der Produktion einwandfrei und wird erst während des regulären Betriebs mit einem Vorlauf von 10 Jahren, wie in diesem Beispiel gewählt, ansprechen.

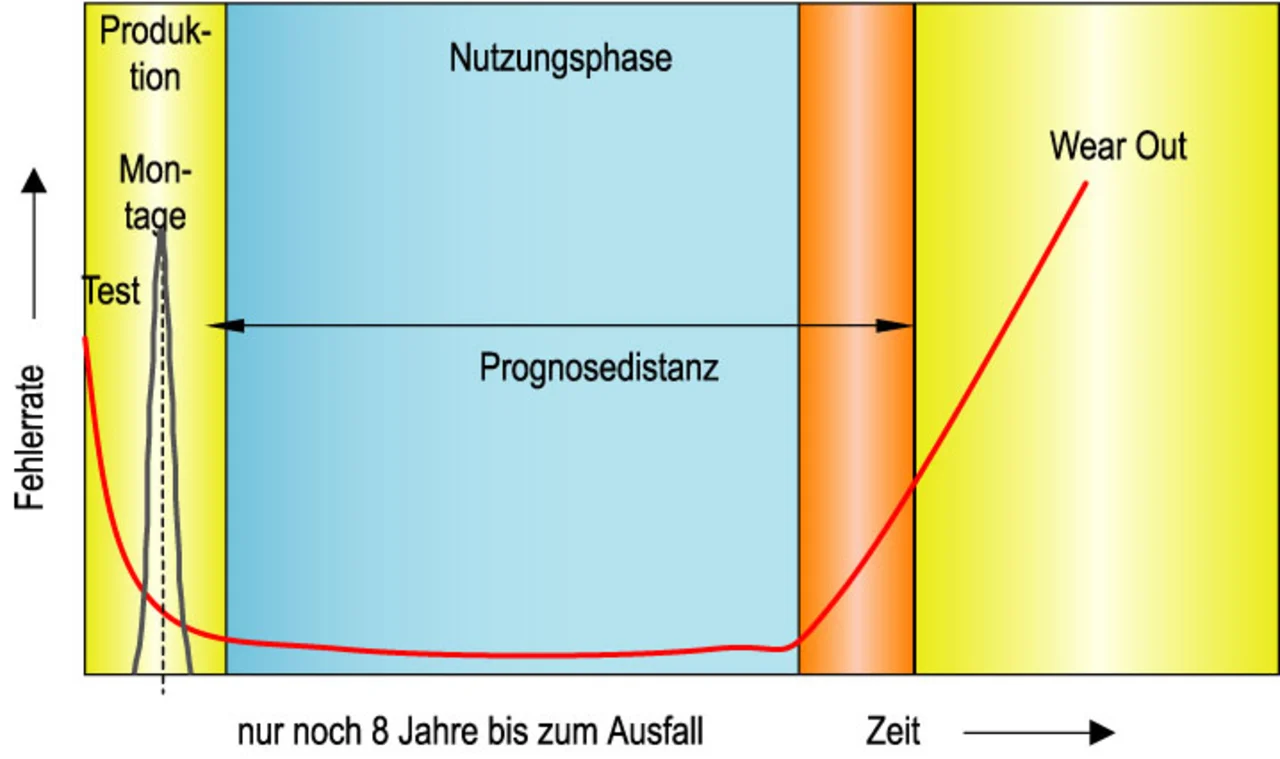

Wurde das Bauelement am Rande der Prozess-Toleranzen hergestellt, durch elektrische Interferenz beschädigt oder anderweitig belastet, ist die Lebensdauer reduziert. Bild 4 zeigt diesen Fall: Die Prognose-Zellen werden bereits während der Produktionsprozesse ausfallen. Der Status der Prognose-Zellen kann vor Auslieferung der fertiggestellten Bauelemente bzw. Module an den Endkunden im Endtest ausgewertet werden. Daraufhin können die gefährdeten Bauteile aussortiert werden. Gegenüber dem Endkunden kann eine garantierte Lebensdauer, bezogen auf das einzelne Modul, nachgewiesen werden.

In der Fertigung von elektronischen Komponenten und Baugruppen haben sich rigide Richtlinien zur Handhabung der empfindlichen Bauelemente durchgesetzt. Schon im Entwurfsprozess werden kritische Stellen durch interne Schutzbeschaltungen innerhalb der Halbleiter und durch geeignete externe Beschaltungen gesichert. Geräte, die in kritischen Anwendungen im Automobil oder in Industrieanlagen eingesetzt werden sollen, müssen in umfangreichen Qualifikationen auf ihre ESD- und EMV-Eigenschaften hin untersucht werden. Dennoch sind nach einer Untersuchung des Jet Propulsion Lab [1] mehr als 30 % der Ausfälle von elektronischen Geräten auf ESD- und EMV-Einflüsse zurückzuführen.

Die Folgeschäden durch diese Ausfälle sind erheblich. Es gibt umfangreiche Untersuchungen, die von weltweit ca. 40 Mrd. Dollar Schäden ausgehen, die durch ESD verursacht wurden. Mit immer kleiner werdenden Prozess-Geometrien in der Halbleiterfertigung werden auch die Ladungsmengen immer geringer, die genügen, um die feinen Halbleiterstrukturen zu schädigen. Die empfindlichste Stelle aller Halbleiter ist dabei das Gate-Oxid. Bereits geringe Ladungsmengen genügen in den dünnen Strukturen, um Feldstärken zu erreichen, die zur dauerhaften Schädigung des Oxids durch eingefangene Ladungsträger führen. Diese Schäden müssen nicht unmittelbar zum Ausfall führen. Die betroffenen Bausteine weisen aber eine deutlich geringere Lebensdauer auf als ungeschädigte Bausteine aus derselben Produktion und können zu einem späteren Zeitpunkt spontan ausfallen.

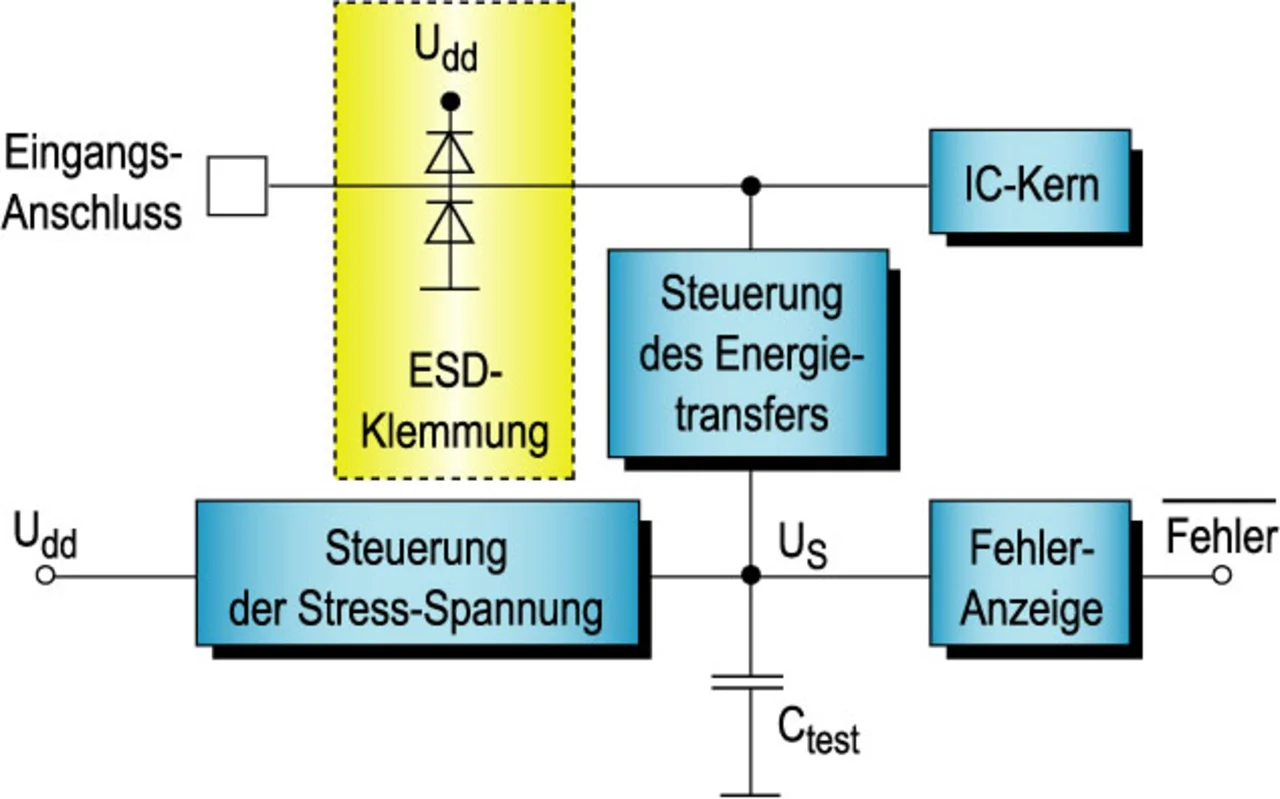

Um das Problem der Empfindlichkeit von Halbleiterstrukturen für EMV und ESD besser fassen zu können, wurden Modelle für die möglichen Einflüsse abgeleitet; hierzu gehören das „Human Body Model“ und das „Machine Model“ der IEC 60749. Die so festgelegten Testbedingungen werden zur Qualifikation der Produkte verwendet. Dadurch werden allerdings nur Extrembedingungen für die Qualifikation von Bauelementen festgelegt. Welchen tatsächlichen Einflüssen ein individuelles Bauelement während des Betriebs unterworfen sein wird, ist damit nicht bestimmt. Eine kontinuierliche Erfassung und Integration aller Umwelteinflüsse auf die Lebensdauer eines einzelnen Bauelementes war bisher nicht möglich. Eine speziell erweiterte „Sentinel Silicon“-Zelle erlaubt das Monitoring von ESD-Einflüssen auf das Halbleiterbauelement (Bild 5).

Dieser Monitor wird direkt mit den Anschlüssen verbunden, deren ESD-Belastung erfasst werden soll. Über eine Schaltung mit hohem Eingangswiderstand zur Steuerung des Energietransfers werden alle auf den funktionalen Teil des Chips wirkenden ESD-Einflüsse „abgehört“. Die erfasste Ladungsmenge wird verstärkt auf den Testkondensator Ctest gegeben. Das Oxid dieses Testkondensators wird gezielt stärker belastet als der restliche Chip. Über eine Auswerte-Elektronik (Fehler-Anzeige, failure indicator) wird der Zustand des Testkondensators bewertet, dieser steht für die Auswertung in einem BiST (Built-in Self Test) oder für andere Diagnosefunktionen auf dem Chip zur Verfügung. Die gesamte Zelle ist in einem 0,25-µm-CMOS-Prozess nur 150 µm2 groß.

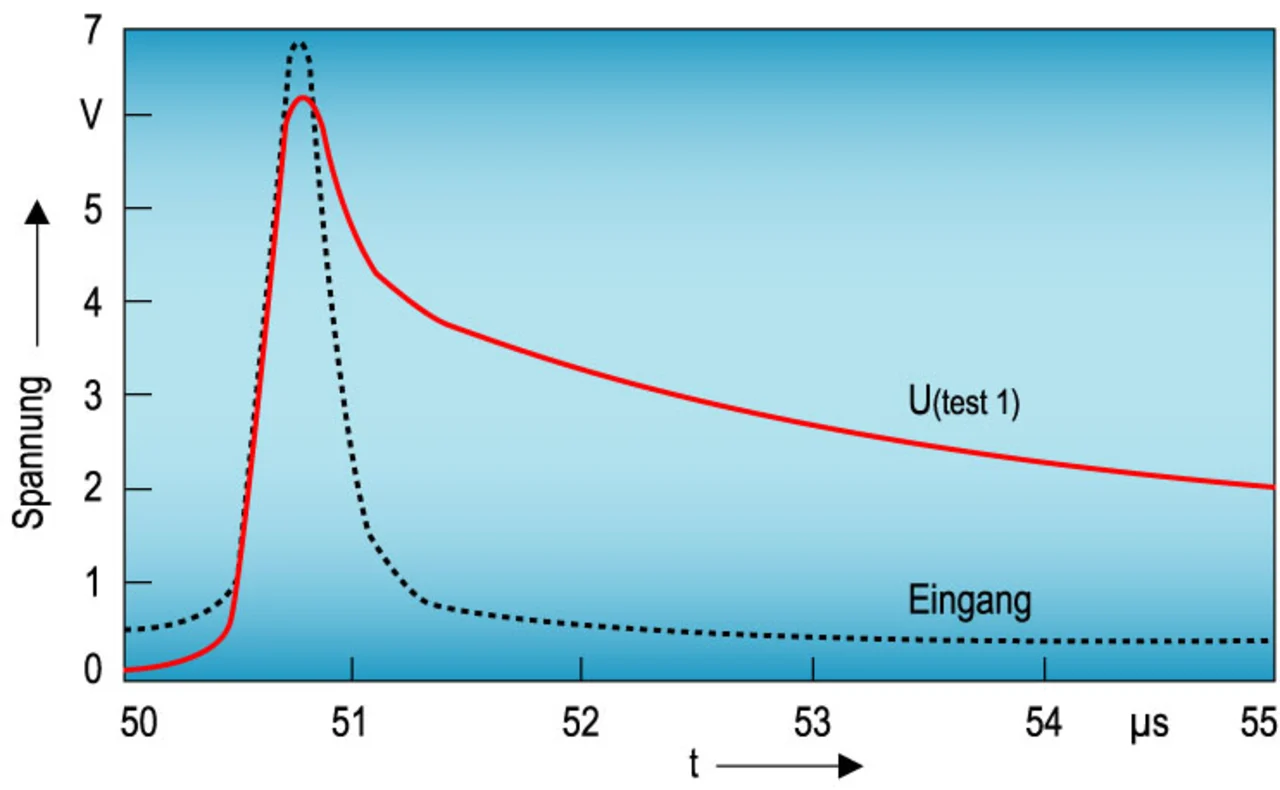

Die Funktion der Zellen ist unabhängig von der Stromversorgung des Bauelements und von der Polarität des ESD-Ereignisses. Bild 6 zeigt den Spannungsverlauf am Testkondensator Ctest. Diese Spannung belastet den Testkondensator und führt zu einer gezielten Alterung des Gate-Oxids. Die Spannung am Testkondensator ist proportional zur Stärke der ESD-Ereignisse. Im vorliegenden Beispiel (Bild 6) ist die Versorgungsspannung des Bauelements abgeschaltet, dennoch funktioniert die Schaltung, und der Testkondensator wird gezielt belastet.

Da sich die „Sentinel Silicon“-Zellen in unmittelbarer Nachbarschaft zur funktionalen Schaltung des Bauelements befinden, wurden sie mit den gleichen Prozess-Parametern hergestellt und haben während des Betriebs dieselben Umgebungsbedingungen hinsichtlich Temperaturen und Handhabung. Einflüsse aus Variationen der Prozess-Parameter und der Umgebungsbedingungen auf die individuelle Lebensdauer des Bauelements werden daher bei der Bewertung in vollem Umfang korrekt mit berücksichtigt. Bauelemente, die durch eine ungünstige Prozess-Führung ein intrinsisch schwächeres Oxid besitzen, werden bereits bei geringeren Belastungen ausfallen. Entsprechend ist auch die „Sentinel Silicon“-ESD-Monitoring-Zelle empfindlicher! Der Zustand der „Sentinel Silicon“-Zelle beeinflusst nicht die Funktion des restlichen Bauelements. Der Zustand der ESD-Monitoring-Zelle kann jederzeit über JTAG-Schnittstellen oder über ein serielles Interface ausgelesen werden.

- Lebensdauer-Monitoring auf dem Chip

- Zustandsabhängige Wartungskonzepte