Mit physikalischer Synthese in das 90-nm-Structured-ASIC-Zeitalter

Interessante Alternative zu FPGAs und Standardzellen-ASICs

Fortsetzung des Artikels von Teil 1

Optimierung für CMG-Strukturen

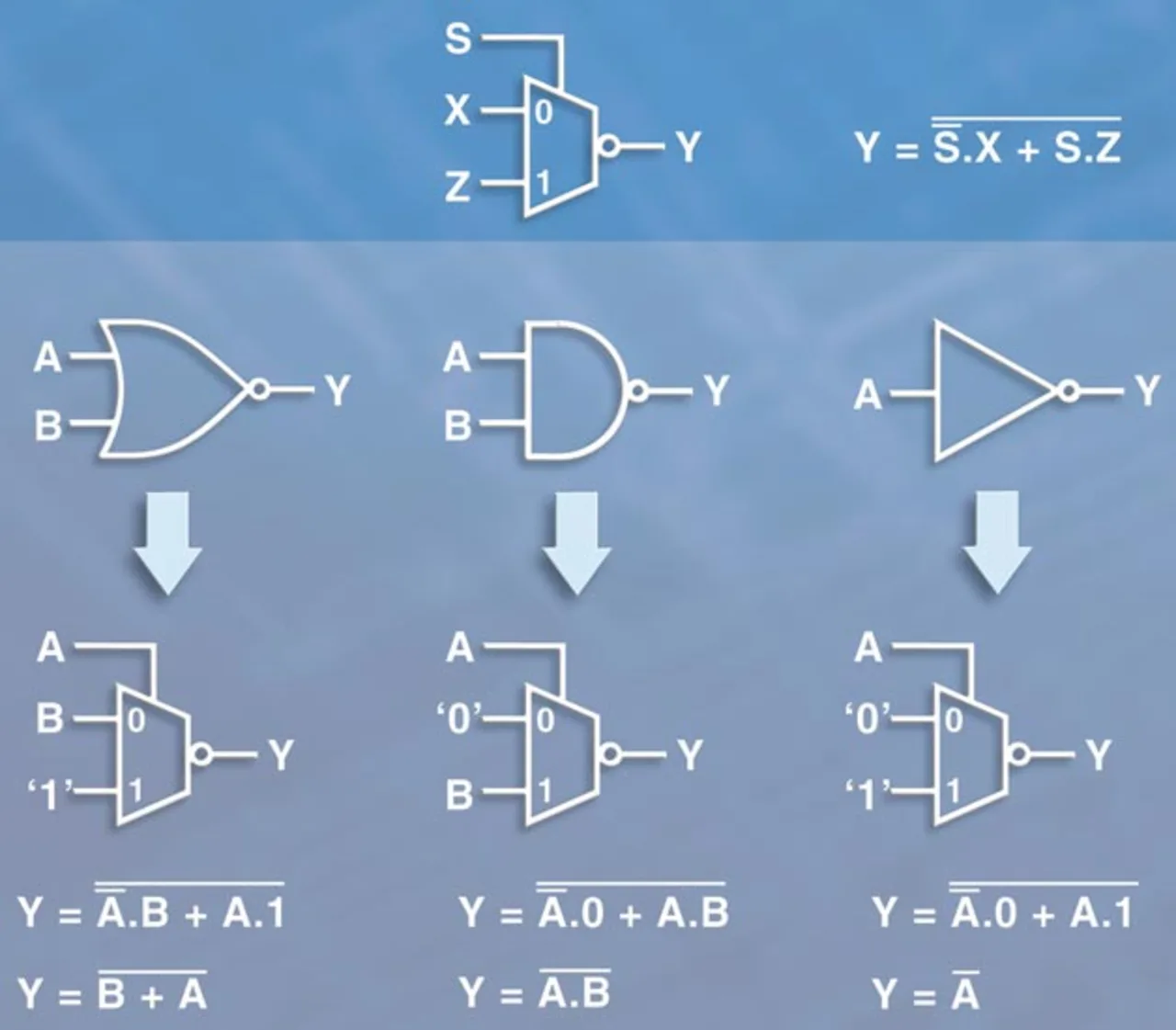

Der mit CMGs besetzte Masterslice setzt voraus, dass das Synthese-Tool sämtliche Fähigkeiten der Zellen ebenso kennt wie die Möglichkeiten, diese Zellen bei der Abbildung eines Designs auf den Masterslice zu kombinieren. Wie Bild 2 zeigt, kann ein invertierender Multiplexer die Funktionen zahlreicher verschiedener Logikzellen abbilden. Voraussetzung ist, dass das Synthese-Tool diesen Ansatz versteht und gleichzeitig weiß, dass das Timing der verschiedenen Signalwege unterschiedlich ist. So kann es im Falle des gezeigten NOR-Gatters sein, dass ein Signal den Pfad von A nach Y um 25 % langsamer durchläuft als den Pfad von B nach Y. Die traditionelle ASIC-Synthese bezieht dieses nicht-homogene Timing-Modell dagegen nicht in ihre Betrachtungen ein.

Jobangebote+ passend zum Thema

Als die CMOS-Geometrien Ende der 90er Jahre die Grenze von 0,25 µm unterschritten, entfielen mehr als 50 % der Signallaufzeiten eines typischen Logik-Pfads in einem ASIC auf die Verbindungen (Interconnect bzw. Wire Delay). Zwangsläufig wurde das Modellieren dieser Signallaufzeiten immer wichtiger, und die bisher ausreichenden statistischen „Wire-Load“-Modelle (WLM) erwiesen sich als zu ungenau. Die EDA-Industrie ging deshalb auf die physikalische Synthese über, um Abhilfe gegen die zu unpräzise Abschätzung der Signallaufzeiten in den Verbindungsleitungen zu schaffen. Als Ziel wurde angestrebt, die WLMs durch Timing-Informationen auf Basis der tatsächlichen Platzierung zu ersetzen. Somit werden dann bei der physikalischen Synthese die kritischen Pfade auf der Grundlage der neu gewonnenen Timing-Informationen optimiert.

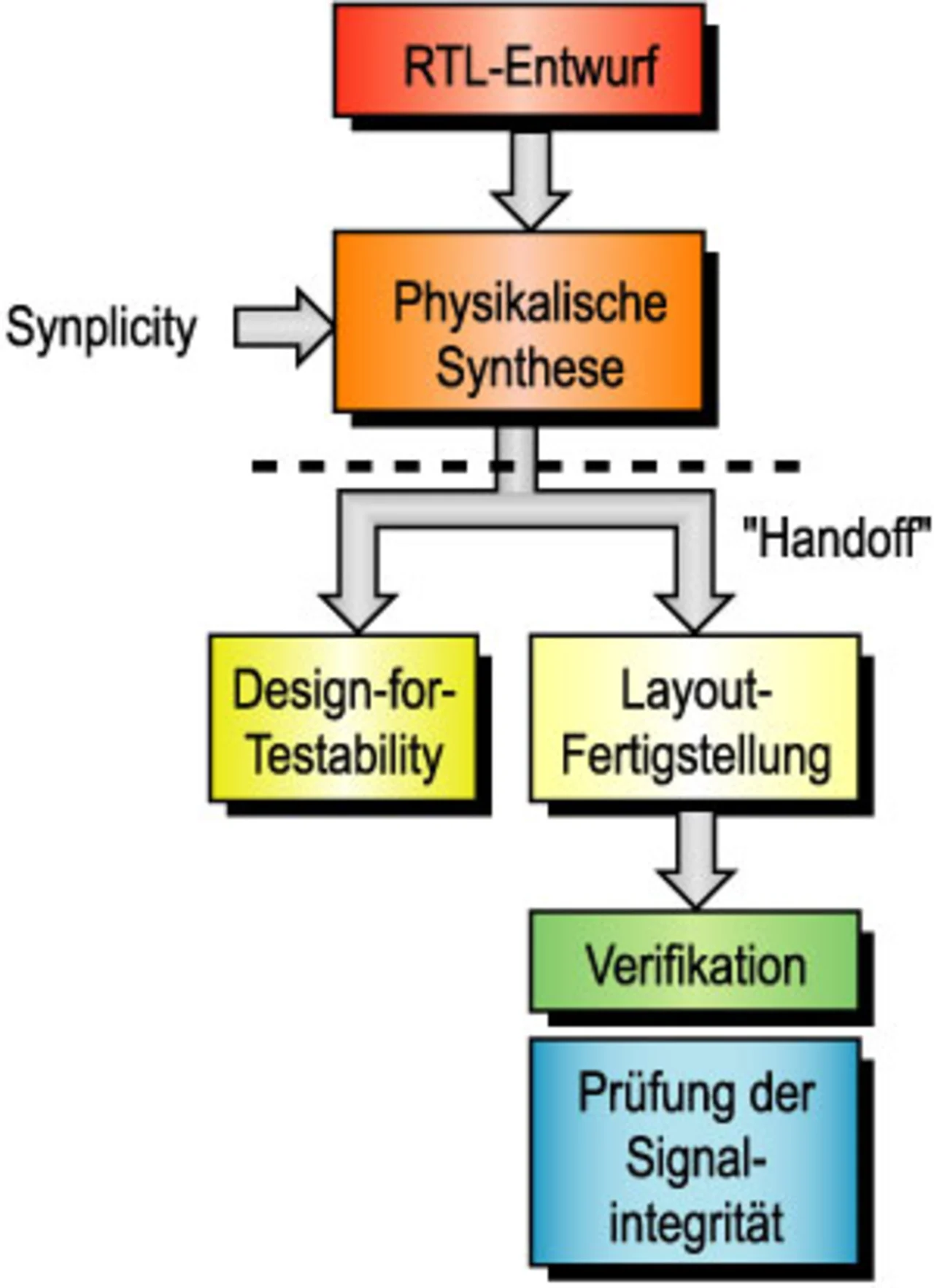

Die Anbieter von EDA-Tools waren bezüglich dieser Vorgehensweise nur teilweise erfolgreich. Dennoch arbeiten Back-End-Design-Teams heute beinahe ausschließlich mit der physikalischen Synthese – sei es in ASIC-Design-Zentren oder bei Kunden mit einem komplett eigenen Tooling-Flow. Nur in sehr geringem Umfang wird die physikalische Synthese dagegen am Front-End eingesetzt, wo der Großteil der Synthese nach wie vor mit WLMs und ihrem ungenauen Timing arbeitet.

Auf dem Structured-ASIC-Markt ist eine neue Art physikalischer Synthese entstanden, die dem Front-End-Designer jegliches Raten erspart. Im Falle der ISSPs handelt es sich dabei um eine Ausweitung der Front-End-Flows dahingehend, dass sie nicht nur die Optimierung und Zuordnung zu den CMGs übernehmen, sondern auch die endgültige Platzierung der CMGs auf dem ISSP-Baustein bestimmen. Dies wiederum ermöglicht den völligen Verzicht auf WLMs, die durch wesentlich präzisere Laufzeitangaben ersetzt werden, bei denen Entfernungen und Hindernisse auf Basis der tatsächlichen CMG-Platzierung berücksichtigt werden.

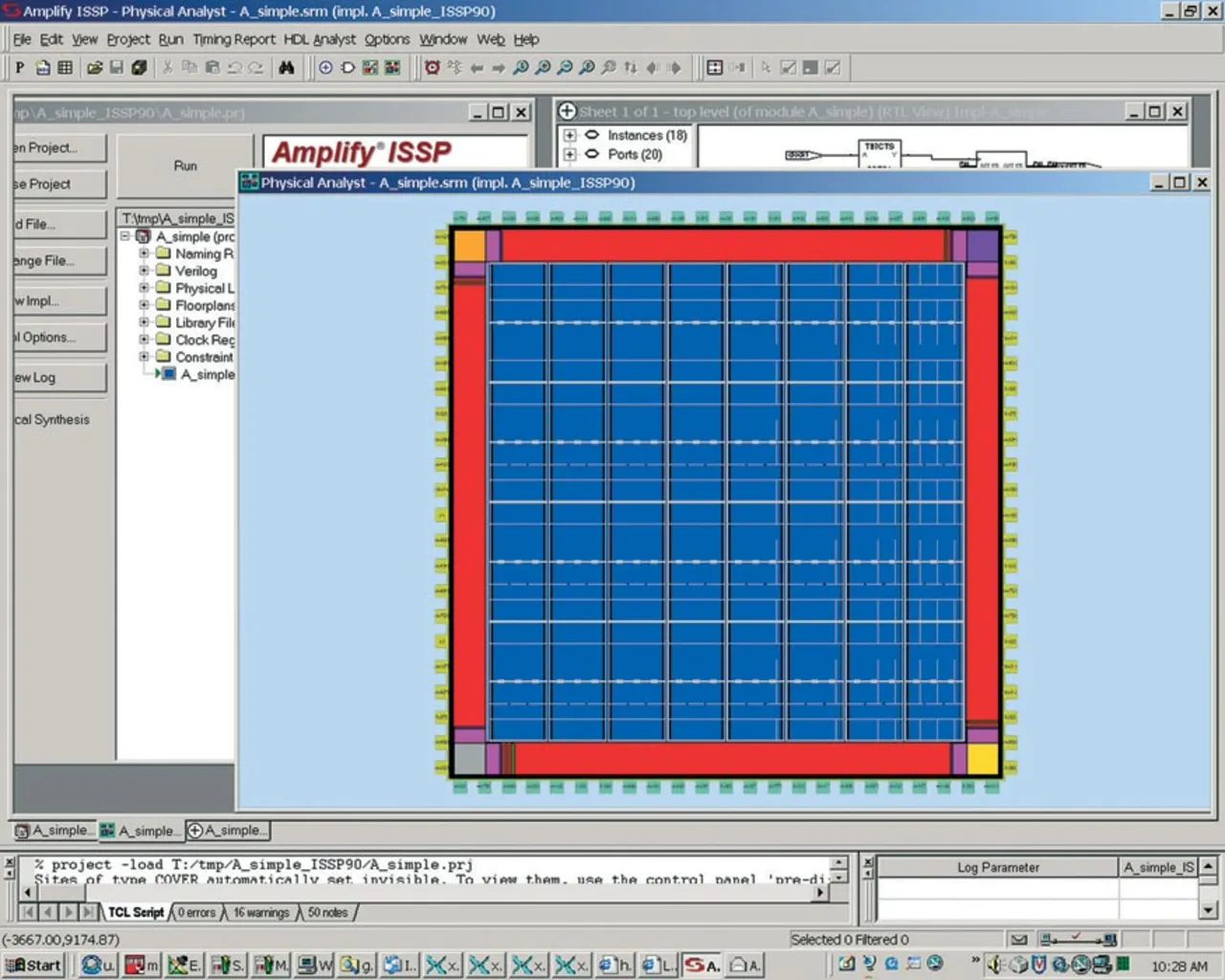

Die gemeinsam von NEC und Synplicity gefundene Anwendung dieses neuen physikalischen Ansatzes führte zur Realisierung des Tools „Amplify ISSP“ als ein schnelles, spezialisiertes Werkzeug, das jedem Front-End-ISSP-Designer die physikalische Synthese zugänglich macht. Ein Screenshot des Tools ist in Bild 3 zu sehen.

In Amplify ISSP verwendet die entfernungsbasierte Modellierung ein so genanntes „Steiner Global Route“-Modell zur Abschätzung des wahrscheinlichen Pfads zwischen zwei platzierten Instanzen auf dem Baustein. Hierzu wird eine orthogonale Matrix aus Pseudo-Routing-Kanälen über den Baustein gelegt, die von der Steiner-Routenmodellierung genutzt werden, um die wahrscheinlichste Route zwischen zwei Punkten zu finden. Dieses pseudo-geroutete Netz wird daraufhin analysiert, die Gesamtdistanz abzuschätzen. Außerdem wird mit eindimensionaler „Parasitic-Extraction“ eine Gesamtlaufzeit für den betreffenden Pfad abgeschätzt. Die Laufzeit lässt sich auf diesem Weg wesentlich genauer bestimmen als mit WLMs und es ist wesentlich wahrscheinlicher, dass die „Buffering-“, „Replication-“ und „Mapping-“ Algorithmen auch bei den kritischen Signalwegen des Designs funktionieren.

Eine weitere Verfeinerung ergibt sich daraus, dass die Steiner-Route der Amplify-ISSP-Software Hindernisse berücksichtigt und in der Lage ist, RAMs, PLLs und andere Blockaden je nach Bedarf zu überqueren oder zu umgehen, wobei die modellierte Laufzeit entsprechend angepasst wird. Das Tool greift sogar auf zusätzliche Puffer und Treiber-Duplizierung zurück, um zu gewährleisten, dass die sensibelsten Netze den erwarteten Routen folgen, wenn im Back-End das abschließende Routing ausgearbeitet wird. Das Ergebnis ist eine wesentlich bessere Korrelation zwischen dem geschätzten und dem tatsächlichen Timing und eine entsprechend weitere Vereinfachung der Timing-Closure.

Insgesamt hat dieses Gemeinschaftsprojekt von NEC und Synplicity dazu geführt, dass der Front-End-ISSP-Designer nunmehr ein Timing erreichen kann, dass nur um 5 % vom endgültigen Timing abweicht, während es mit traditionellen WLMs etwa 50 % waren.

Tool-Kapazität und Laufzeit

Ein weiterer wichtiger Aspekt der Structured-ASIC-Synthese von Synplicity ist, dass das Tool für jedes ASIC-Gatter des Designs nicht mehr als 1,5 bis 2 Kbyte Hauptspeicher benötigt, während bei der traditionellen Synthese 15 Kbyte/Gatter einzukalkulieren waren. Extrapoliert man diesen Wert, so erhält man 2,5 Millionen Gatter als Obergrenze dessen, was im Adressbereich eines 32-bit-Betriebssystems nach dem „Top-Down“-Prinzip verarbeitet werden kann. Mit dem Umstieg auf ein 64-bit-Betriebssystem wie Linux RHEL-3 oder Solaris-64 erzielt man sogar eine praktisch unbegrenzte Kapazität. Selbstverständlich müssen tolerierbare Laufzeiten eingehalten werden. Das besagte Entwurfsprojekt mit 2,5 Millionen Gattern wurde mit einem 32-bit-Linux-Betriebssystem in weniger als zehn Stunden verarbeitet. Dieser Kapazitätsvorteil gestattet die Top-Down-Synthese aller ISSP-Designs, was die Perspektive für zusätzliche Cross-Chip-Optimierungen und Timing-Analysen eröffnet. Da auch der Back-End-Flow den gesamten Chip erfasst, ergibt sich eine bessere Anpassung zwischen Front-End und Back-End mit entsprechend positiven Auswirkungen auf die Timing-Korrelation.

Optimierung auf Basis der Platzierung

Dass Optimierung und Platzierung in der Amplify-ISSP-Software (Bild 4) automatisch zu einer in einem Durchgang stattfindenden physikalischen Analyse kombiniert werden, erlaubt die gleichzeitige Optimierung des Timings und der Platzierung. Den Optimierungs-Algorithmen stehen dabei die aus dem fertig platzierten Entwurf extrahierten, präziseren Leitungs-Laufzeiten zur Verfügung. Somit ist sichergestellt, dass die Logik-Optimierungen von den Timing-Vorgaben des Anwenders korrekt dirigiert und die Aufmerksamkeit den wirklich kritischen Signalwegen des Designs gilt, anstatt sie in jene Pfade zu investieren, die von traditionellen Synthese-Tools als kritisch eingestuft worden wären.

| Dipl.-Inf. Christoph Hecker studierte Informatik an der Universität Passau. Nach dem Studium 1996 arbeitete er bei Infineon Technologies als Design-Ingenieur für ISDN-Chips. Seit 2001 ist er bei NEC Electronics Europe im Produkt-Management beschäftigt und dort für die ISSP-Produkte zuständig. E-Mail: heckerc@ee.nec.de |

| Doug Amos war Mitte der 90er Jahre der erste europäische Ingenieur und technische Direktor bei Synplicity. Als Field Application Engineer war er verantwortlich für die gesamte ASIC- und FPGA-Unterstützung der Firma. Vor seiner Tätigkeit bei Synplicity arbeitete er in verschiedenen Beratungs- und Ingenieursfunktionen für Actel, Altera und Xilinx. Insgesamt verfügt er über eine mehr als 20-jährige Erfahrung in den Bereichen FPGA- und ASIC-Design. E-Mail: douga@synplicity.com |

Verwandte Artikel:

- Interessante Alternative zu FPGAs und Standardzellen-ASICs

- Optimierung für CMG-Strukturen