Kürzere Entwicklungszeit durch geplante Signalzuordnung von FPGAs für optimales Platinenlayout

Freie Fahrt für Signale

Fortsetzung des Artikels von Teil 1

Signalzuordnung für optimale Platinenverdrahtung

Nachdem alle programmierbaren Bauteile beschrieben wurden und ihre Anschlusszuordnungen festliegen, kann die Verbindungsinformation über eine Netzlistendatei oder eine Verbindungstabelle importiert werden. Dann lassen sich die Komponenten auf der virtuellen Platine platzieren und optimieren.

Viele Platinenentwickler wollen möglicherweise schon in einem frühen Entwicklungsstadium die Bauteile auf Systemebene für bestmögliche Verdrahtung optimieren, bevor Platzierung und Verdrahtung der FPGAs festliegen, gleichzeitig aber die wichtigsten Xilinx-Entwurfsregeln auf der I/O-Seite erfüllen. Hier einige Hinweise dazu:

- Verringerung der Anzahl der Leitungsüberkreuzungen, die weniger Durchkontaktierungen erfordern, die möglicherweise mit weniger Verdrahtungsebenen auskommen, die schneller sind und frühzeitige Verbindungsstudien für mehr „Wenn – Dann“-Analysen erleichtern.

- Reduzierung der Einflüsse auf die Signalintegrität und Erzeugung sauberer Signale, auch durch weniger Leitungsüberkreuzungen und Durchkontaktierungen. Bei hoher Geschwindigkeit wirken Durchkontaktierungen nämlich wie Stichleitungen (stubs), die Signalflanken verschlechtern.

Jobangebote+ passend zum Thema

Ein Beispiel aus der Praxis

Bei der Entwicklung eines Systems, das zwei FPGAs aus der Serie Virtex-II mit je 1702 Anschlüssen und ein drittes FPGA mit 1152 Anschlüssen sowie einen kundenspezifischen Prozessor enthielt, tauchten folgende Herausforderungen auf:

- Das Entwicklungsteam war über das ganze Land verstreut: Der FPGA-Ingenieur, der Hardware-Entwickler und die Layouter/Entflechter saßen an verschiedenen Orten.

- Das schnell erstellte Design erreichte die Layout-Phase, in der sich aber herausstellte, dass die Platine nicht zu entflechten war.

- Offensichtlich musste jede Änderung, die zur Entflechtbarkeit der Platine führte, den Designregeln für Xilinx-Bauteile entsprechen.

Statt umfangreiche Anstrengungen vorzunehmen, um alle Ingenieure an einem Ort zusammenzuführen und das Problem von Hand zu lösen, wurde mit Design F/X gearbeitet:

- Der FPGA-Ingenieur sandte die notwendigen .PAD-Dateien an den Hardware-Entwickler.

- Die Layouter/Entflechter schickten die Cadence-Allegro-Platinendatei an den Hardware-Entwickler.

- Der Hardware-Entwickler importierte alle Dateien in Design F/X und optimierte die Platine innerhalb weniger Stunden.

- Der Hardware-Entwickler lieferte die Ausgangsdatensätze, nämlich die geänderte Cadence-Allegro-Platinendatei und die geänderten .UCF-Dateien an seine jeweiligen Teamkollegen.

- Der FPGA-Ingenieur bestätigte, dass die neue Anschlussbelegung für die Xilinx-Bauteile keine der Designregeln verletzt und erteilte die Freigabe.

- Die Layouter bzw. Entflechter konnten die Platine erfolgreich entflechten und trugen die Änderungen per Back-Annotation in den Cadence-OrCAD-Schaltplanein.

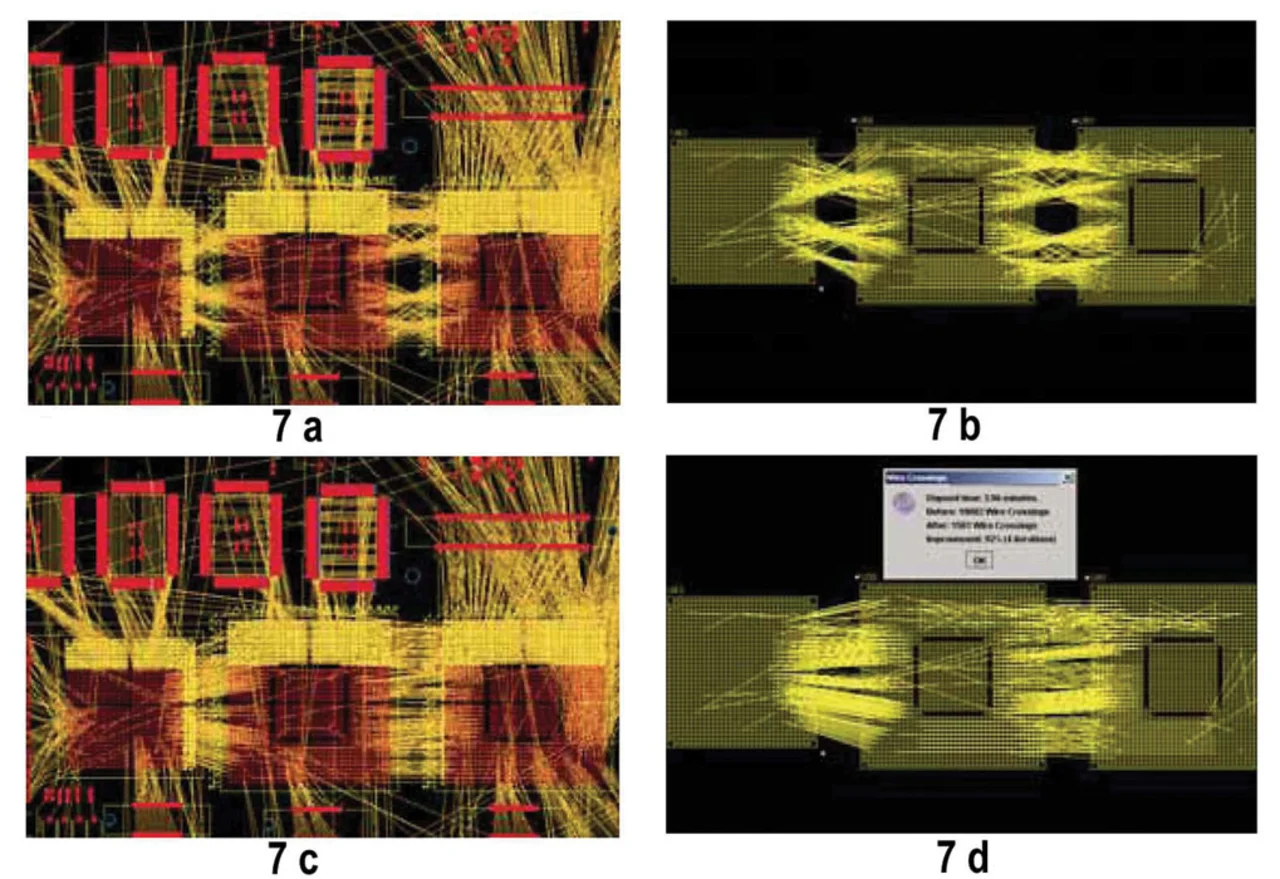

Der gesamte Prozess nahm lediglich Tage statt Wochen in Anspruch. Bild 7 zeigt das Layout der Platine mit den drei FPGAs von Xilinx vor (oben) und nach der Optimierung mit Design F/X (unten) in der Darstellung mit Cadence Allegro (links) und in der Darstellung mit Design F/X (rechts). Während ursprünglich 19 002 Drahtkreuzungen vorhanden waren, konnten sie mit der Optimierung auf lediglich 1501 reduziert werden: Das ist eine Einsparung von 92 %. Vor diesem Hintergrund wird verständlich, dass das ursprüngliche Design, das ursprünglich für die vorgegebene Anzahl der Signallagen nicht zu entflechten war, nun doch erfolgreich durchgeführt werden konnte.

Autoren

Philippe Garrault ist Technical Marketing Engineer bei Xilinx Inc.

E-Mail: philippe.garrault@xilinx.com

Suresh Subramaniam arbeitet bei Xilinx Inc. als Senior Design Engineer.

E-Mail: Suresh.Subramaniam@xilinx.com

Wolfgang Hascher, Elektronik Wireless

Verwandte Artikel:

- Freie Fahrt für Signale

- Signalzuordnung für optimale Platinenverdrahtung