Effiziente SOPC-Designs dank neuer Logik-Architektur

FPGAs – programmierbare Systeme auf einem Chip

Fortsetzung des Artikels von Teil 1

Die Stratix-II-Architektur

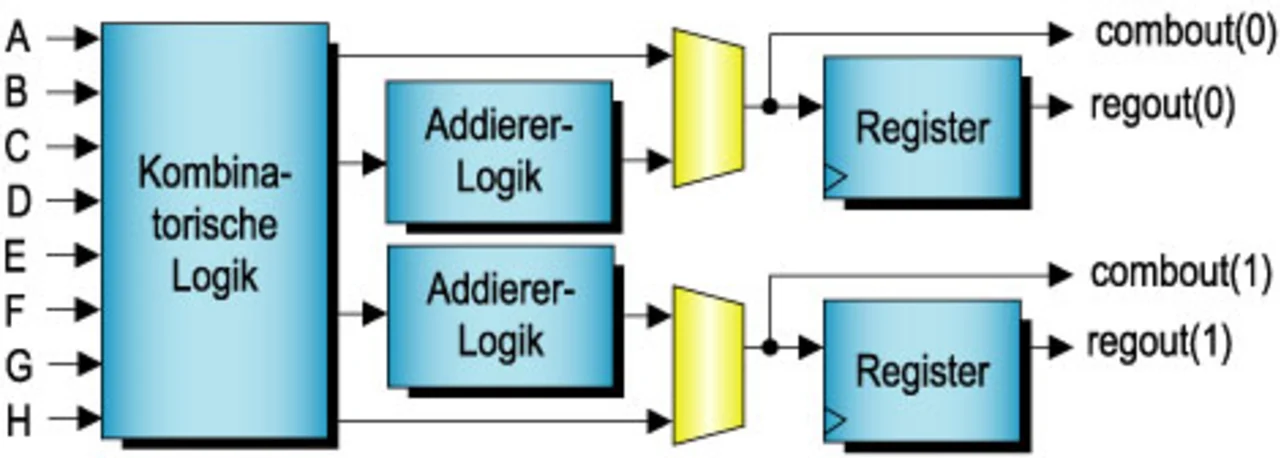

Die flexible neue Stratix-II-Logikstruktur ist um die ALMs herum aufgebaut. Ein ALM hat acht Eingänge, zwei Ausgänge und zwei Register, die unabhängig voneinander oder in Verbindung mit LUT-Ressourcen (Look-up-Tables) genutzt werden können (Bild 3). Außerdem sind Pfade für Übertrag, Kaskadierung und Rückkopplung vorhanden, mit denen sich komplexere Funktionen aufbauen lassen oder dedizierte Addierer für die Unterstützung eines Dreifach-Addierbaums realisieren lassen.

Jobangebote+ passend zum Thema

Die neuen LUT-Ressourcen kann der Anwender in verschiedenen Modi konfigurieren: beispielsweise als eine 7-Input-LUT, zwei gleiche 6-Input-LUTs, zwei 5-Input-LUTs mit zwei geteilten Eingängen, zwei 4-Input-LUTs für die Rückwärtskompatibilität mit der ersten Generation von Stratix-Bausteinen, oder Kombinationen kleinerer Funktionen wie einer 3-Input-LUT mit einer 5-Input-LUT. Einer der wichtigsten Vorteile einer größeren Look-up-Table besteht darin, Multiplexer sehr effizient zu implementieren.

Die Effizienz der Stratix-II-Architektur lässt sich mit den 32 bit breiten 4:1-Multiplexern aus obigem SOPC-Beispiel zeigen: Zur Implementierung ist nur das Äquivalent von 32 LEs notwendig, im Gegensatz dazu waren es in früheren Architekturen 64 LEs.

Die Compilierung des beispielhaften SOPC-Designs demonstriert die Vorteile, die sich durch die Unterstützung von breiten Funktionen ergibt. In einem Stratix-II-Baustein benötigt das Beispielsystem das Äquivalent von nur 1745 LEs, verglichen mit 2851 LEs bei einer Stratix-Implementierung. Die gesparten 1106 LEs bedeuten eine Effizienzsteigerung um 39 %, eine Verbesserung, die mit der 40-prozentigen Steigerung von fmax auf 176 MHz einher geht. Die Geschwindigkeits- und Effizienzssteigerungen ermöglichen die erschwingliche Implementierung von komplexeren, schnellen FPGA-basierenden SOPC-Designs.

Selbstverständlich sind viele praxisgerechte Systeme komplexer als das relativ einfache, hier diskutierte SOPC-Beispiel. In solchen Systemen sind oftmals viele breite Multiplexer erforderlich. Die Quartus-II-Design-Software von Altera konstruiert solch größere Multiplexer, indem sie 8:1-Mux-Funk-tionsbausteine nutzt, gleichzeitig aber die Anzahl der Logikebenen minimiert, um die Leistungsvorteile aufrechtzuerhalten. Multiplexer sind in vielen Systemen mit unterschiedlichen Daten-pfaden sehr häufig genutzte Funktionen. DSP-basierende Systeme, in denen die Blöcke im Zeitbereich gemultiplext werden (was viele I/O-Standards vorsehen), greifen ebenfalls in signifikanter Art und Weise auf Multiplexer-Blöcke zurück. Jedes Protokoll, das Steuerworte umfasst und mit hoher Geschwindigkeit arbeitet, braucht Logik, um diese Steuerworte in den Datenstrom einzufügen und zu löschen. Das Löschen und Einfügen dieser Worte, genauso wie jede Art der Datenverarbeitung in einem Datenstrom, macht die Verwendung eines „Barrel-Shifters“ notwendig, der wiederum ebenfalls aus Multiplexern verschiedener Breiten besteht.

SOCs sind für Systementwicklungen prädestiniert, bei denen die Endanwender eine höhere Leistung auf einer kleineren Plattform zu geringeren Kosten brauchen. Sie bringen enorme Integrationsvorteile und zwar in Bezug auf die benötigte Leiterplattenfläche, die Zuverlässigkeit, Leistung und Kosten. Da Leistung und Komplexität von programmierbaren Bausteinen gestiegen sind, greifen Entwickler verstärkt auf SOPC-Lösungen zurück, weil sie dadurch in den Genuss der zusätzlichen Vorteile kommen, die solche Ansätze bieten: höhere Design-Flexibilität, niedrigere Entwicklungskosten, geringeres Risiko und eine kürzere Markteinführungszeit. Die neuen Stratix-II-FPGAs von Altera setzen auf einer komplett neuen Logikarchitektur auf. Ihre Komplexität ist um mehr als den Faktor 2 größer, die Geschwindigkeit liegt um 50 % höher und die Kosten um rund 50 % niedriger als bei früheren FPGA-Generationen. Allein diese wesentlichen Vorteile erlauben es den Entwicklern, SOPC-Designs für eine große Palette von neuen Applikationen zu implementieren.

Stratix II – neue Logikstruktur für mehr Design-Effizienz

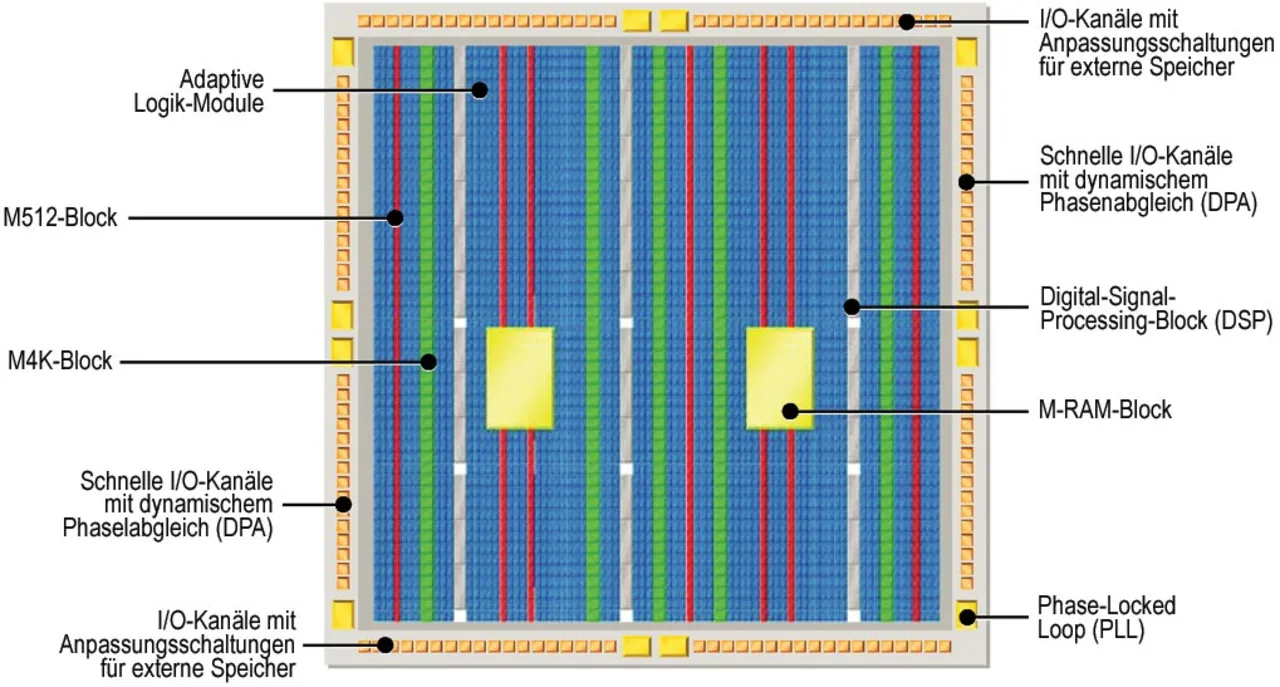

Die neue Stratix-II-Familie ergänzt mit ihrer neuen Logikstruktur die wesentlichen Merkmale, die schon zum Erfolg der ersten Stratix-Generation beigetragen haben, wie TriMatrix-Speicher, DSP-Funktionsblöcke und die externen Speicher-Schnittstellen. Optimiert für den 90-nm-Prozess, wurden die Produktmerkmale nochmals deutlich verbessert:

- Höhere Komplexität und höhere Geschwindigkeit – Bei mehr als der dop-pelten Komplexität und über 9 Mbit Speicher ist die Stratix-II-Familie um mehr als 50 % schneller als die vorherige FPGA-Generation.

- Bis zu viermal mehr DSP-Bandbreite – Stratix-II-Bauelemente liefern eine hohe, vorhersagbare Leistung für komplexe DSP-Funktionen mit bis zu 384 Multiplizierern (18 ? 18 bit) je Baustein.

- Unterstützung für moderne Speicher – Stratix-II-Bauelemente unterstützen mit einer speziellen Schaltung die modernsten externen Speicher-Schnittstellen. Es werden u.a. 256-MHz-DDR2-SDRAM, 300-MHz-RLDRAM II und 200-MHz-QDR-SRAM unterstützt, mit ausreichender Bandbreite und I/O-Pins für den Anschluss 168-/144-poliger 64-bit-DIMMs.

- 1-Gbit/s-I/Os mit dynamischem Phasenausgleich – Mit ihren SerDes- und DPA(Dynamic Phase Alignment)-Schaltungen ermöglichen die Stratix-II-FPGAs I/O-Datenraten von 1 Gbit/s für quellensynchrone Übertragungen ohne zusätzliche Logik-Ressourcen. Damit werden bei sehr schneller Datenübertragung das Leiterplatten-Layout und das Timing-Management vereinfacht.

- Höhere TriMatrix-Speicherbandbreite – Die Stratix-II-Chips bieten bis zu 9 Mbit Speicher (mit Parität), um vielfältige speicherintensive Applikationen zu unterstützen.

Stratix-II-FPGAs verfügen aber auch über neue Funktionen, wie eine nichtflüchtige 128-bit-Verschlüsselungs-Technologie auf Basis des AES-Algorithmus (Advanced Encryption Standard). Sie stellt sicher, dass kundenspezifische IP-Blöcke, die in das FPGA implementiert wurden, geschützt sind. Die Stratix-II-Bausteine sind die ersten SRAM-basierten FPGAs mit einer nichtflüchtigen Verschlüsselung.

| Edward Clarke hat einen Abschluss in Electrical and Electronic Engineering der Universität Bristol. Er ist Product Marketing Engineer bei Altera Europe in High Wycombe, Bucks/England, und verfügt über mehr als zehn Jahre Erfahrung in den Bereichen Halbleiter-Design, Applikationsunterstützung und technisches Marketing. |

Verwandte Artikel:

- FPGAs – programmierbare Systeme auf einem Chip

- Die Stratix-II-Architektur