Maximale Geschwindigkeit durch direkte Anbindung an den Hauptprozessor

FPGA-Coprozessoren in AMD64-Systemen

Fortsetzung des Artikels von Teil 1

FPGA-Coprozessoren am HyperTransport-Interface

Das HyperTransport-Interface wird von FPGAs der Firmen Xilinx (Virtex-2, -2pro, -4) und Altera (Stratix, -II, -GX) als I/O-Standard unterstützt. Zurzeit sind damit HyperTransport-Busfrequenzen bis 400 MHz erreichbar. Der HyperTransport-Protokoll-Stack im FPGA benötigt etwa 250 000 Gatteräquivalente – je nach Größe des FPGAs und der HyperTransport-Link-Konfiguration entspricht das bis zu 25 Prozent der FPGA-Ressourcen. HyperTransport-Controller („caves“) als IP sind von GDA Technology Inc. und Altera in Link-Konfigurationen von 8 bit/400 MHz und 16 bit/400 MHz auf dem Markt. Damit können Datenraten von 3,2 Gbyte/s erreicht werden, die für Co-Processing-Anwendungen notwendig sind.

Jobangebote+ passend zum Thema

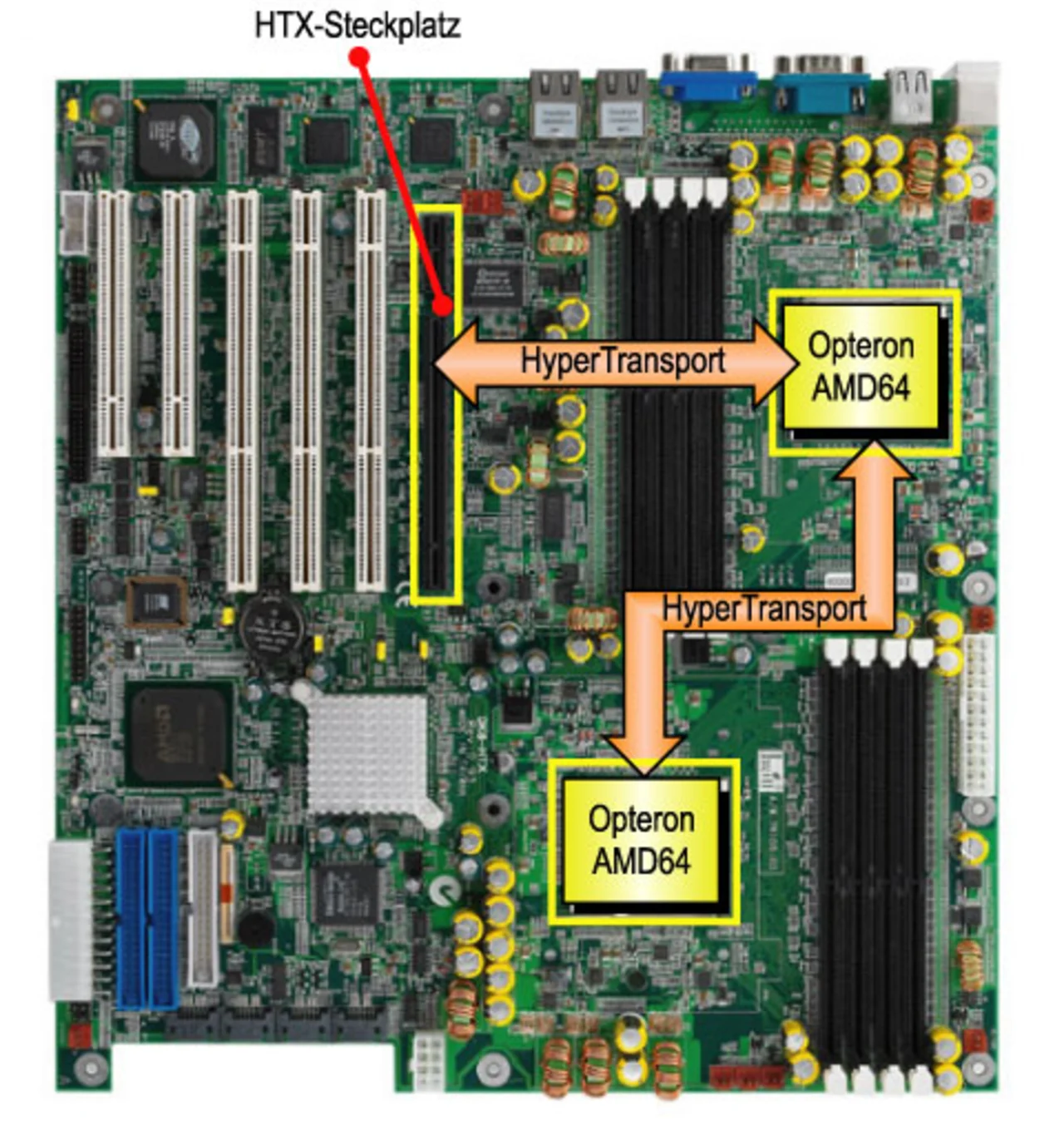

Für die Einbindung des FPGA auf der Plattform gibt es mehrere Möglichkeiten. Neben dem direkten Auflöten des FPGA, was eine eigene Boardentwicklung erfordert, sind das der Anschluss über einen HTx-Steckplatz (Bild 3) oder die Nutzung eines CPU-Sockels auf einer Multiprozessor-Platine.

HTx stellt eine Erweiterung von HyperTransport dar, die es erlaubt, Peripherie-Hardware als Einsteckkarten anzuschließen, ähnlich wie bei PCI-Express. Dabei werden 8-bit- oder 16-bit-Links mit 800 MHz benutzt, die Datenraten von 6,4 Gbyte/s ermöglichen. Vor allem bei Anwendungen, die neben dem Coprozessor weitere Hardware wie PHYs und Steckverbinder erfordern oder die einen hohen Stromverbrauch haben, bietet sich die Verwendung von HTx an. Mit dem iWill DK8 HTx ist bereits ein Dual-Opteron-Board mit HTx-Slot auf dem Markt. An Einsteckkarten für HTx gibt es einen Infiniband-Netzwerkcontroller von Pathscale und eine 10-Gbit/s-Ethernet-Karte von Myricom.

Coprozessor statt Prozessor im Standard-Board

In Multiprozessor-Anwendungen definiert die HyperTransport-Architektur Knoten, welche im Normalfall von den Prozessoren gebildet werden. Ersetzt man eine Opteron-CPU (Knoten) durch einen FPGA-Coprozessor, kann man eine Standard-Multiprozessor-Plattform für das Co-Processing nutzen. Das FPGA wird dabei mittels einer Adapterplatine in einen CPU-Sockel gesteckt. Diese Lösung bietet sich vor allem dann an, wenn außer dem FPGA keine zusätzliche Hardware für die Coprozessor-Anwendung erforderlich ist. Weiterhin kann auf nahezu jede Opteron-basierte Multiprozessor-Plattform zurückgegriffen werden. Für Sockel-940-Plattformen existieren bereits Hardware-Lösungen von DRC (basierend auf Xilinx Virtex 4) und XtremeData Inc. (Stratix II, Bild 4).

Der Einsatz von Coprozessoren in Rechnersystemen wird durch die AMD64-Architektur in besonderer Weise unterstützt. HyperTransport als ein effizientes, skalierbares Bus-Interface erlaubt die direkte Anbindung der Coprozessoren an die System-CPU. Coprozessoren in Form von FPGAs gewährleisten volle Flexibilität für die Hardware-Beschleunigung. Mit der Initiative „Torrenza“ arbeitet AMD gemeinsam mit Industriepartnern wie IBM, HP, Sun und Cray an der weiteren Optimierung der AMD64-Architektur, um Coprozessor-Anwendungen in nahezu allen Bereichen voranzutreiben.

| [1] | AMD, Xilinx, Celoxica (Hrsg.): FPGA Offload Through a Tightly Coupled Computing Architecture. Presentation at Embedded Systems Conference, San Jose, 2006. |

| [2] | Demerjian, Ch.: DRC Opteron accelerator now quickens Crays. The Inquirer (online), 2006. www.theinquirer.net/?article=31398 |

| [3] | HyperTransport Consortium (Hrsg.): HTX High-Performance Connectivity Standard. Presentation, 2005. www.HyperTransport.org |

| [4] | HyperTransport Consortium (Hrsg.): The Future of High-Performance Computing: Direct Low-Latency Peripheral-to-CPU Connections. Whitepaper, 2004; www.HyperTransport.org |

| [5] | HyperTransport Consortium (Hrsg.): HyperTransport I/O Technology Comparison With Traditional And Emerging I/O Technologies. Whitepaper, 2004. www.HyperTransport.org |

| [6] | Yoshida, J.: H.264 codec jeopardizes MPEG-4’s ascendancy. EE Times 2002. www.eetimes.com/story/OEG20020920S0049 |

| Dipl.-Ing. (FH) Thomas Günther studierte Automatisierungstechnik an der HTW Dresden. Seit 2000 ist er im Dresden Design Center von AMD tätig und hauptsächlich mit FPGA-basiertem Rapid Prototyping von Server-Chipsatz-Komponenten beschäftigt. Zurzeit arbeitet er an der Weiterentwicklung eines AMD64-Plattform-Simulators. thomas.guenther@amd.com |

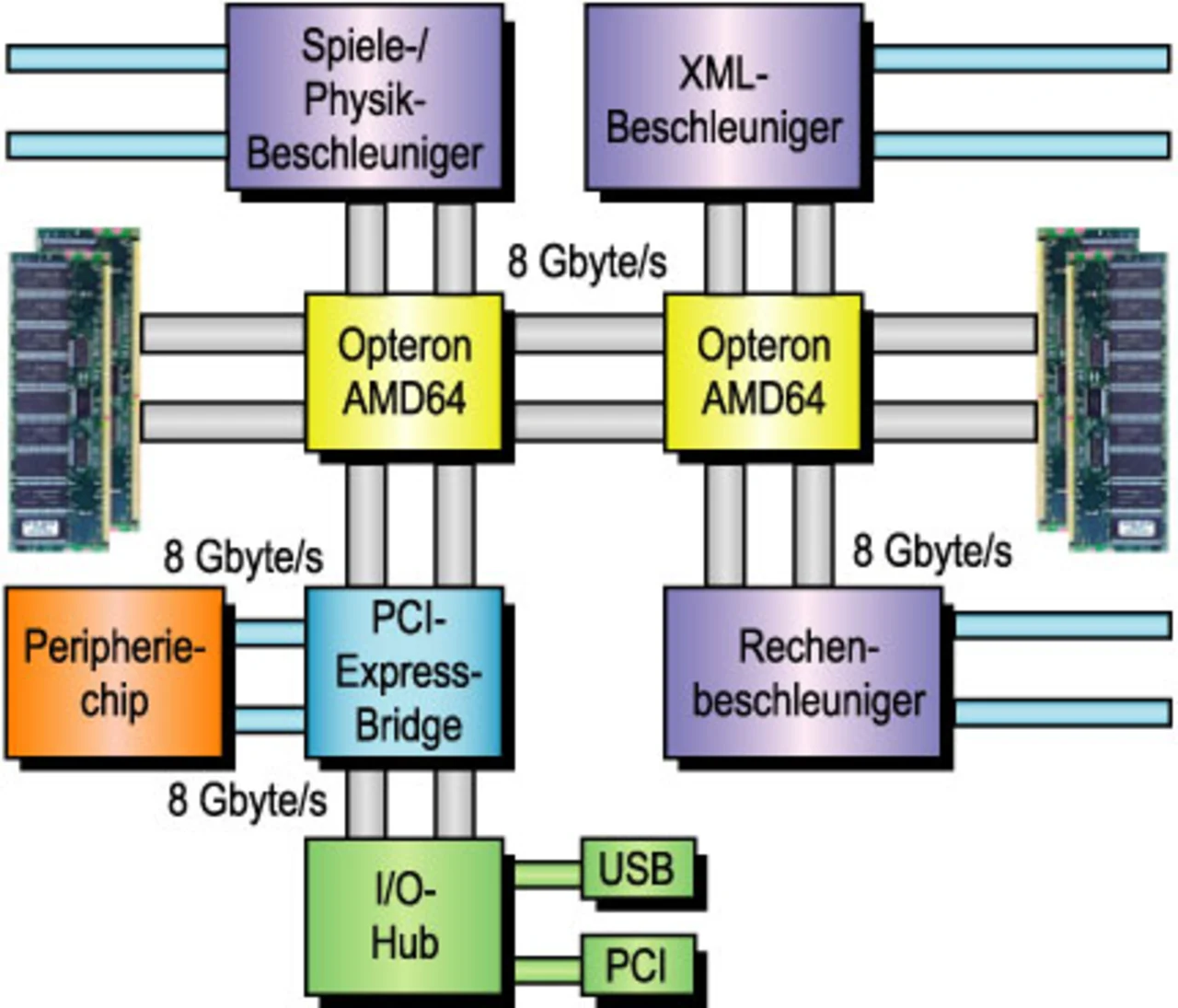

Wesentliche Merkmale der AMD64-Systemarchitektur sind der in den Prozessor integrierte Memory Controller und das HyperTransport-Interface für die Chip-to-Chip-Verbindung. Letzteres erlaubt die direkte Verbindung von CPUs in Multiprozessorsystemen sowie die direkte Anbindung von Peripherie-Schaltkreisen wie I/O-Hubs oder Coprozessoren. HyperTransport ist skalierbar in Linkbreiten von 2 bis 32 bit und Frequenzen von 200 MHz bis 1,4 GHz und unter-stützt Datenraten bis 22,4 Gbyte/s. Jeder Opteron-Prozessor, der für Multiprozessor-Plattformen vorgesehen ist (Serien 200 und 800), verfügt über drei HyperTransport-Links. Je nach System-Konfiguration besteht die Möglichkeit, freie HyperTransport-Links für den Anschluss von Coprozessoren zu benutzen. Bild 1 zeigt eine mögliche Konfiguration.

Die Anbindung über HyperTransport ermöglicht die direkte Ansteuerung des Coprozessors als I/O-Device unter Verwendung der Standard-PCI-Konfiguration. Der Coprozessor wiederum hat durch den integrierten Memory Controller direkten Zugriff zum Hauptspeicher ohne Eingriff der CPU. Die HyperTransport-Architektur erlaubt weiterhin den Einsatz lokaler Speicher am Coprozessor.

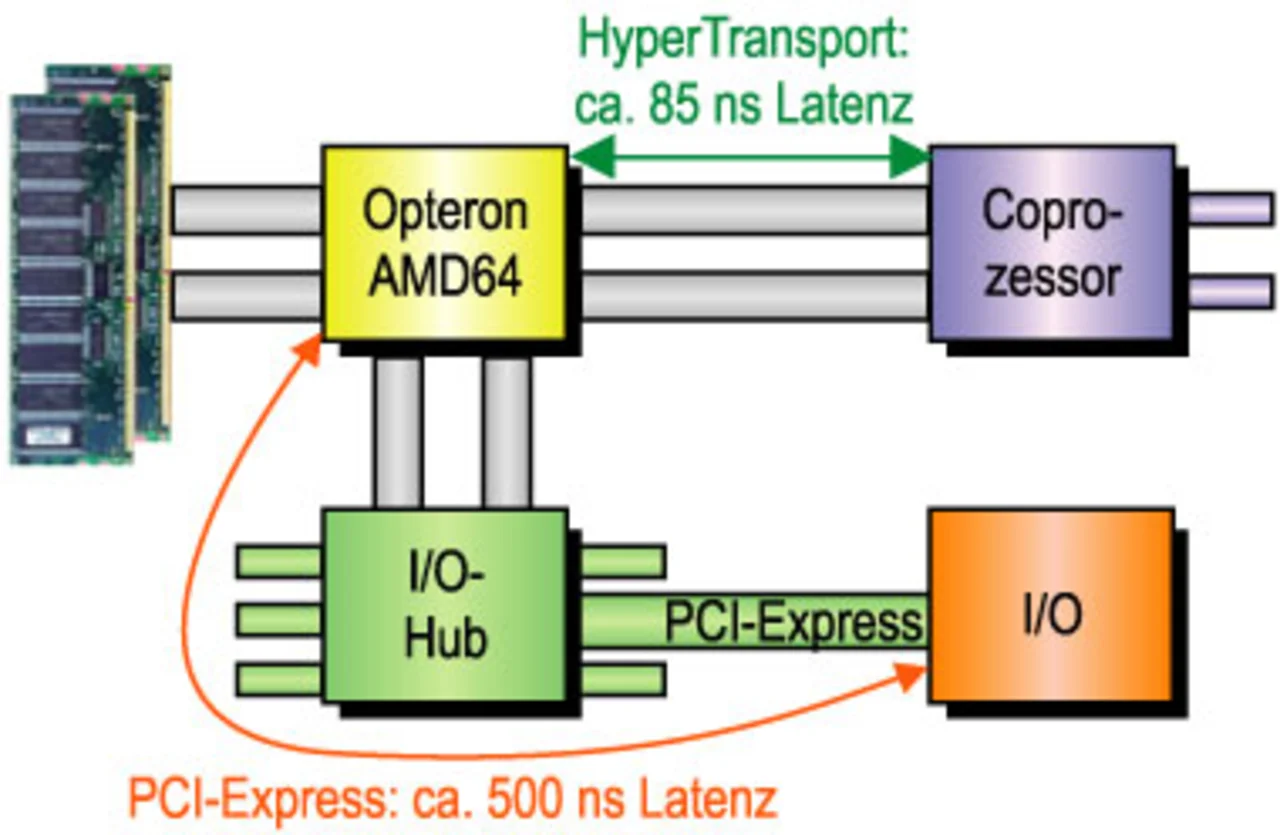

Gegenüber anderen High-speed-Interfaces wie PCI-Express hat HyperTransport Vorteile, die es für die Anbindung von Coprozessoren auszeichnen:

- geringe Speicher-Latenz,

- geringer Protokoll-Overhead,

- separate Taktleitung.

Die Latenz von Speicherzugriffen bei HyperTransport ist um 55 Prozent geringer als bei PCI-Express. Grund hierfür ist die direkte („glueless“) Verbindung des Coprozessors zur CPU, während in herkömmlichen Systemen die PCI-Express-Devices nur über den I/O-Hub erreichbar sind. Weiterhin zeichnet sich HyperTransport durch ein effektives Protokoll aus. Der maximale Overhead pro HyperTransport-Da-tenpaket beträgt 12 Bytes gegenüber 24 Bytes bei PCI-Express. Durch so genanntes „Priority Request Interleaving“ können Lese-Zugriffe in den laufenden Datentransfer eingeschoben werden, was zu geringerer Speicher-Latenz führt (Bild 2).

HyperTransport ist kein SERDES-Interface, d.h., es entfällt die 8-bit-/10-bit-Codierung/Decodierung. Der Takt wird auf separaten Leitungen – eine Taktleitung pro acht Datenleitungen – auf dem Interface mitgeführt. Die Skalierbarkeit der Busfrequenzen von 200 MHz bis 1,4 GHz führen zu deutlich geringerer Stromaufnahme gegenüber PCI-Express-Plattformen (Bustakt 2,5 GHz). Dabei ist die Bandbreite durch das effiziente Protokoll vergleichbar. Auf Basis von HyperTransport existieren be-reits Coprozessoren, zum Beispiel der NetL7NLS1000, ein 10-Gbit/s-Content-Prozessor von NetLogic.

- FPGA-Coprozessoren in AMD64-Systemen

- FPGA-Coprozessoren am HyperTransport-Interface