Anwendung von CRC-Hard-Blöcken verringert Entwicklungsaufwand

Fehlererkennung in FPGAs

Fortsetzung des Artikels von Teil 1

Literatur

Durch die Verfügbarkeit von CRC-Blöcken in FPGAs ist die Implementierung von Fehlererkennungs-Mechanismen in unterschiedlichste Entwürfe einfacher und aufwandsärmer geworden. Vor allem lässt sich dazu die CRC-Wizard-IP im Rahmen der Software COREGenerator nutzen, um Fehlererkennung auch für unterschiedlichste Protokolle wie Aurora und PCIExpress realisieren zu können. (Frank Riemenschneider)

[1] Informationen über den LogiCORE-CRC-Assistenten: www.xilinx.com/crcwizard

[2] Informationen über eingebettete CRCBlöcke in FPGAs der Serie Virtex-5: pdf>www.xilinx.com/bvdocs/userguides/ug196.pdf

arbeitet als Associate Design Engineer bei Xilinx India Technology Services Pvt. Ltd. in Haiderabad, Indien.

sunita.jain@xilinx.com

arbeitet als Technical Lead bei Xilinx India Technology Services Pvt. Ltd. in Haiderabad, Indien.

guru.prasanna@xilinx.com

Programmierbare Chips sollen ASICs, FPGAs und ASSPs ablösen

Jobangebote+ passend zum Thema

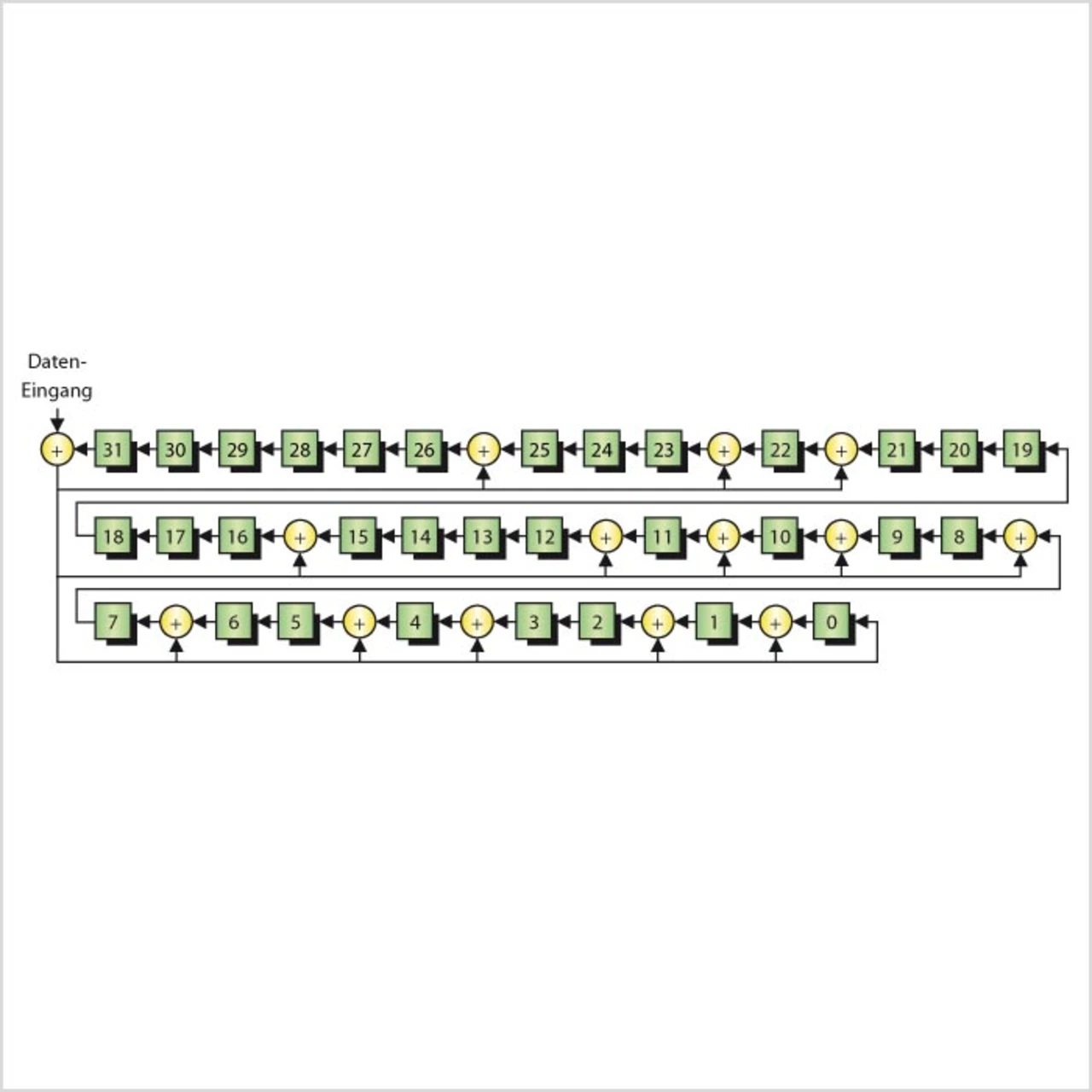

Die Berechnung einer CRC-Prüfsumme ist eine Polynom-Division. Zu ihrer Hardware-Implementierung dient ein Schieberegister, das als CRC-Register bezeichnet wird und dessen Länge dem Grad des Generator-Polynoms entspricht. Damit erfolgt eine CRC-Berechnung in zwei Schritten. Zunächst wird das CRC-Register initialisiert. Anschließend werden Nachrichten-Bits solange empfangen, wie sie am Eingang anstehen. Wenn das höherwertige Bit im CRC-Register 1 ist, wird es um eine Position nach links geschoben und das Ergebnis mit G über XOR verknüpft. Andernfalls wird es nur um eine Position nach links verschoben.

Wenn diese Schritte für eine vorgegebene Nachricht durchlaufen sind, enthält das CRC-Register den Rest. Diese Schritte lassen sich mit einer Schaltung implementieren, die als Schieberegister mit linearer Rückkopplung LFSR (linear feedback shift register) bezeichnet wird. Bild 1 zeigt eine LFSR-Realisierung für die Berechnung des CRC mit dem CRC-32-Polynom. Dabei hängt die Plazierung der XOR-Gatter von den Koeffizienten der entsprechenden Terme im Polynom ab, die 1 betragen. Jedem der nummerierten Blöcke im Bild entspricht ein Speicherelement (Flipflop).

Die Hardware-Implementierung des CRC nutzt ein einfaches LFSR. Obwohl eine derartige Schaltung sehr einfach zu implementieren ist, benötigt sie zur Berechnung des CRC-Werts für einen n bit langen Datenstrom immerhin n Taktzyklen. Diese Latenz kann für schnelle Datennetze nicht hingenommen werden, bei dem Daten-Frames mit höheren Geschwindigkeiten verarbeitet werden müssen. Vielmehr ist für die breitbandige Vernetzung eine Implementierung von CRC-Generierung und -Prüfung für einen parallelen Datenstrom wünschenswert.

Der für die Virtex-5-LXT- und -SXT-Bausteine implementierte CRCBlock hilft Entwicklern, indem er die Prüfsummenberechnung beschleunigt. So basieren die bereitgestellten CRC-Hard-Blöcke auf CRC-32 und CRC-64, die für die CRC-Erzeugung von 4 und 8 byte breiten Dateneingängen eine Latenz von lediglich einem Taktzyklus aufweisen. Die Schnittstelle ist recht einfach strukturiert und leicht anzuwenden. Dabei funktionieren die Hard-Blöcke in Verbindung mit einigen CRC-spezifischen Parametern am Eingang als CRC-Rechner für einen gegebenen Datenstrom. Allerdings enthalten sie keine Funktionalität für einen CRC-Vergleich, der im allgemeinen Bereich des FPGA realisiert wird. Jeder CRC-Hard-Block im FPGA berechnet asynchron eine 32 bit lange Prüfsumme; er ist mit seinen wichtigsten Schaltungsblöcken in Bild 2 dargestellt. An seinem Ausgang CRCOUT erscheinen die Werte bit-invertiert und byte-reversiert.