Pinkompatible 8- und 32-bit-Mikrocontroller ermöglichen einfache Produktskalierung

Einsturz der Bitgrenzen

Fortsetzung des Artikels von Teil 2

Einsturz der Bitgrenzen

Nachdem bislang ausschließlich die CPUs beider Bausteine betrachtet wurden, muss bei der Frage nach der Kompatibilität auch auf die Peripherie eingegangen werden. Um diese sicherzustellen, hat Freescale abgesehen von den CPU-Cores die Peripheriefunktionen und Speicher auf dem Chip so identisch wie möglich entwickelt. Heutzutage sind C-Compiler selbst für kleine Mikrocontroller-Cores verfügbar. Diese, jeweils für einen speziellen Core entwickelten Compiler machen die Unterschiede zwischen den Befehlssätzen für den Entwickler unsichtbar und erlauben die Verwendung einer gemeinsamen Programmiersprache. Die Unterschiede zwischen S08- und V1-Core verlieren sich also sozusagen „im Innenleben“ des Compilers. Wenn man auf eine andere MCU umsteigt, ist es nicht der Rechenkern, der das Problem darstellt, sondern es sind die ganzen ihn umgebenden Komponenten. Unterschiedliche Peripheriefunktionen erfordern immer die Modifikation des Codes.

Um die Flexis-Mikrocontroller-Familien kompatibel zu machen, kommen auf beiden MCUs vom A/D-Wandler bis zu den Timer-Modulen identische Peripheriemodule zum Einsatz. Wenn z.B. auf dem S08 QE128 der UART mit 115,2 Kbit/s, 9 Datenbits, 2 Stopbits und gerader Parität konfiguriert wird, muss dieser Code nicht geändert werden, wenn man die gleichen Einstellungen auf den V1 QE128 übernehmen will.

Jobangebote+ passend zum Thema

Ein Referenzdesign beweist Kompatibilität in der Praxis

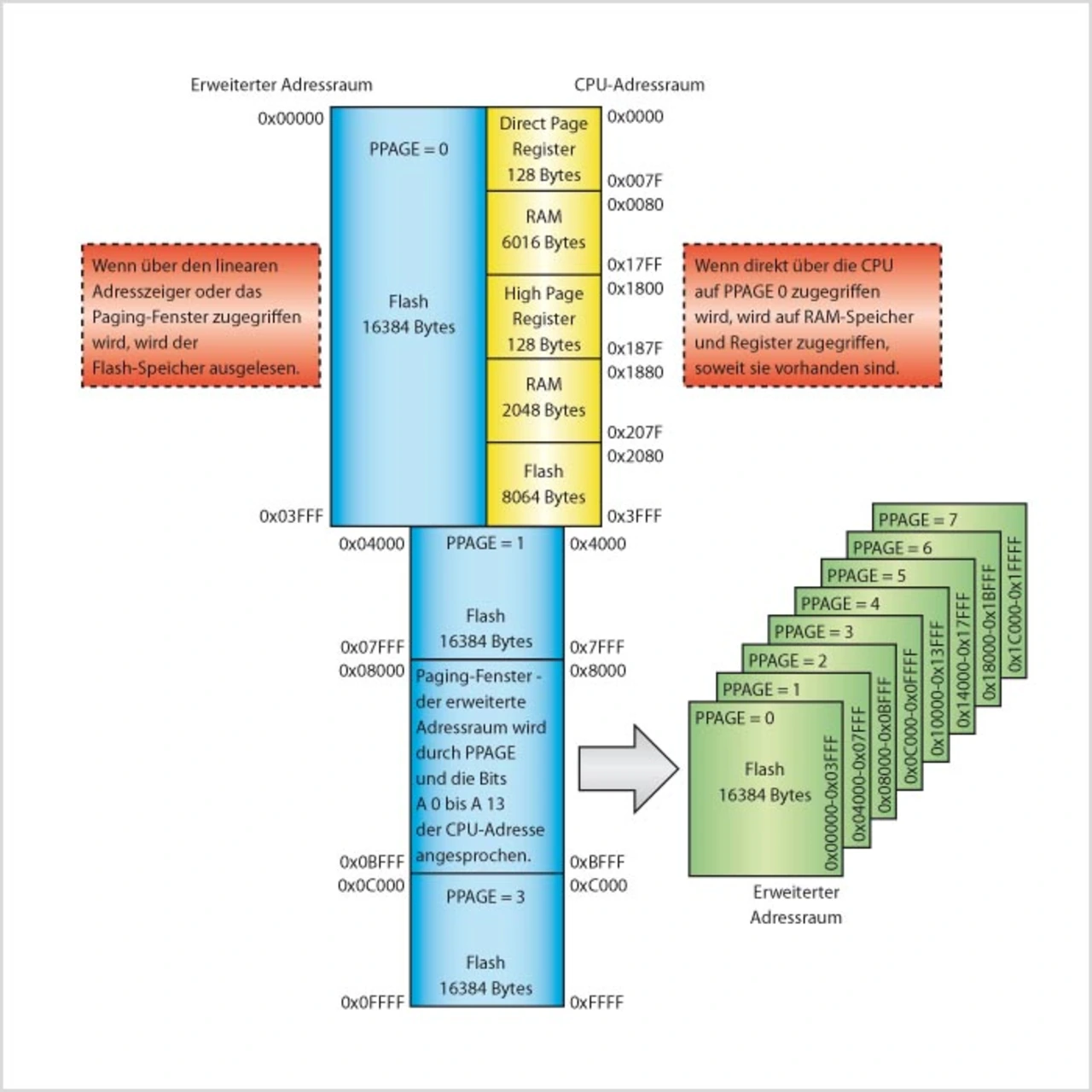

Der Flashspeicher des S08QE ist in 16 Kbyte großen Pages organisiert. Die gewünschte Page wird selektiert, indem ein entsprechender Wert in das PPAGE-Register geschrieben wird. Die Pages 1 und 3 sind im 64-Kbyte-Adressraum des S08 jederzeit außerhalb des Paging-Fensters adressierbar. Das RAM sowie alle Peripherie- und Systemregister sind so angelegt, dass sie mit dem Page-0-Flash überlappen und immer außerhalb des Paging-Fensters adressiert werden können. Auch der Teil des Page-0-Flash, der nicht von RAM bzw. Registern überdeckt wird, ist außerhalb des Paging-Fensters verfügbar. Auf alle anderen Speicheradressen im Flash kann man über das Paging-Fenster zugreifen, indem man das PPAGE-Register setzt.

Außer über das Paging-Fenster können Daten im gesamten Flash-Speicher mit Hilfe des so genannten LAP (Linear Address Pointer) adressiert werden. Der LAP besteht aus jeweils drei Adress- und Datenregistern. Die volle Adresse wird in die drei Adressregister geschrieben, und Daten können unter Verwendung eines der drei Datenregister gelesen bzw. geschrieben werden. Die Funktion des LAP beschränkt sich auf reine Datenbewegungen, der Programmcode muss über den 64-Kbyte-Bereich und das Paging-Fenster abgearbeitet werden.

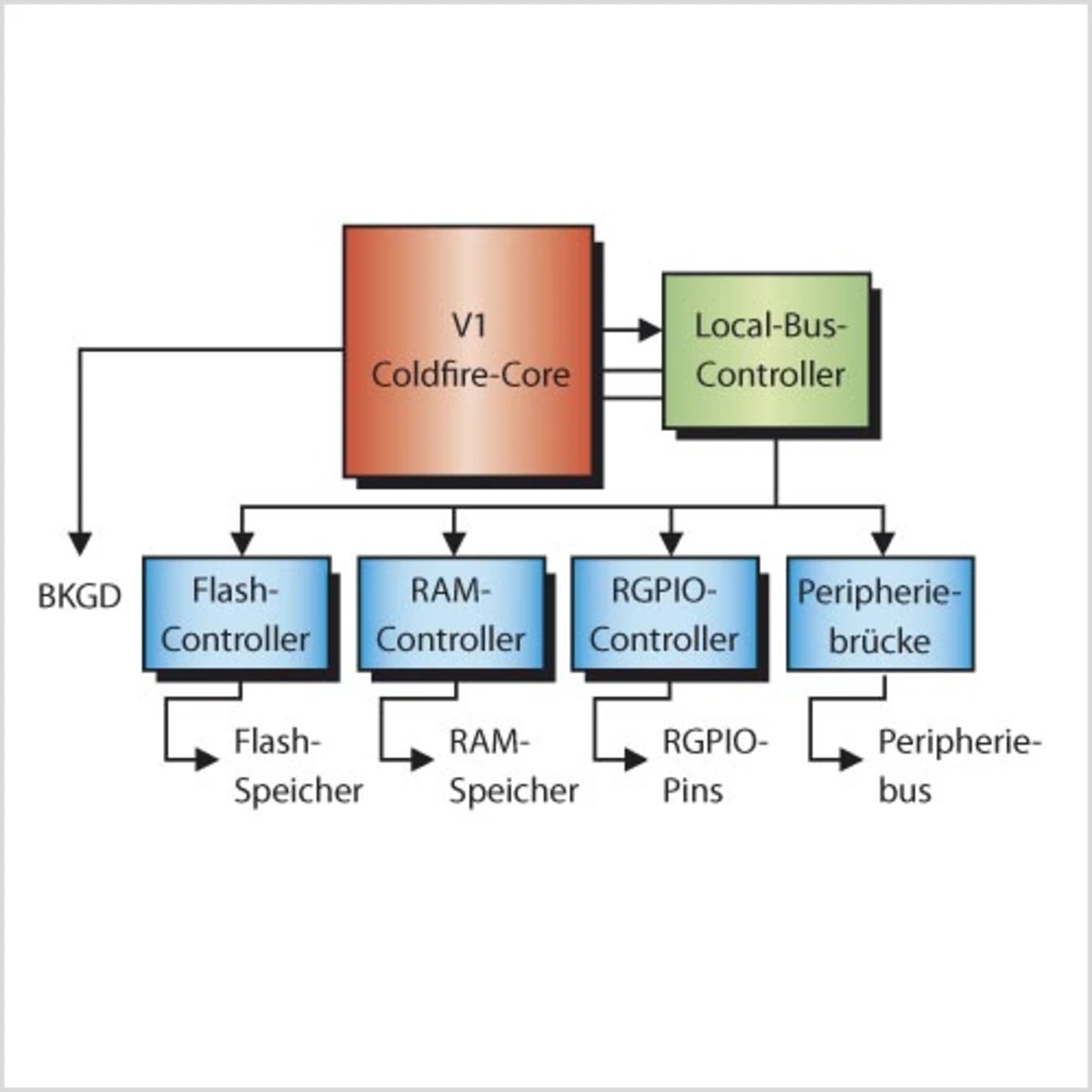

Auf der anderen Seite verfügt der V1 gleich über mehrere Bus-Controller: Local-Bus-Controller, Flash-Controller, RAM-Controller, RPGIO-Controller sowie eine Peripheriebrücke. Wie aus Bild 4 zu entnehmen ist, kommuniziert die CPU je nach Zieladresse über den lokalen Bus mit den vier anderen Controllern. Flash-Speicher, RAM und die RPGIO-Controller verfügen jeweils über eine 32-bit-Schnittstelle. Die Peripheriebrücke auf der Seite des Local Bus ist ebenfalls in 32-bit-Technik ausgeführt, während sie auf der Seite des Peripheriebusses nur 8 bit breit ist, um eine Integration mit den 8-bit-Peripheriefunktionen des S08 zu ermöglichen. Peripheriemodule können mit 8-, 16- oder 32-bit-Zugriffen gelesen bzw. beschrieben werden, wobei jeder Zugriff mit mehr als 8 bit in zwei bzw. vier aufeinander folgende Byte-Zugriffe konvertiert wird. Obwohl die Peripherieregister nur 8 bit breit sind, kann der V1 Zugriffe auf entsprechende Gruppen mit 16- bzw. 32-bit-Befehlen somit viel schneller durchführen.

Vergleich der Befehlssatzarchitekturen und Kompatibilität von S08 und Coldfire V1

Die Befehlssatzarchitektur (ISA) des S08-Cores entspricht der S08-Standardversion, allerdings mit zwei zusätzlichen Befehlen CALL und RTC (Return from CALL) für Call-Funktionen aus dem Page-Speicher. Die S08-Architektur ist so angelegt, dass Befehle schon vorab eingelesen werden, um die Ausführungszeiten zu verkürzen. Der Befehlszyklus des S08 entspricht der Frequenz des Bustaktes bzw. dem halben Takt des Prozessor-Cores.

- Einsturz der Bitgrenzen

- Literatur

- Einsturz der Bitgrenzen

- Einsturz der Bitgrenzen