Cyclone-II-FPGAs mit dem Softcore-Prozessor Nios II ermöglichen kostengünstige und gleichzeitig leistungsfähige Systeme

Ein starkes Team

Fortsetzung des Artikels von Teil 1

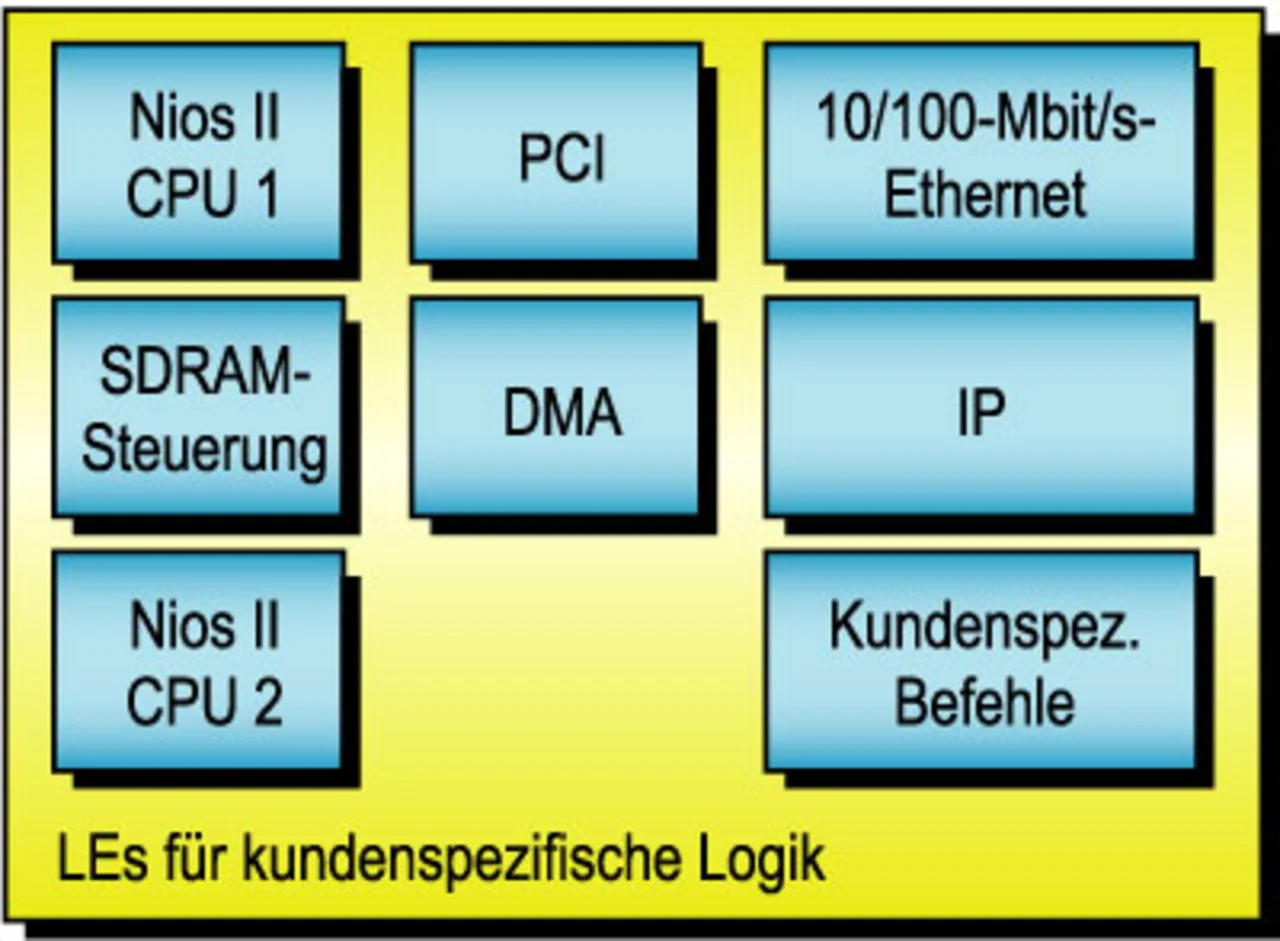

Einfacher Design-Flow

Besonders im Consumer-Markt ist man mit sehr schmalen Zeitfenstern für die Markteinführung und sehr kurzen Produktlebenszyklen konfrontiert. Deshalb stellt Altera einen umfangreichen Satz von Entwicklungswerkzeugen bereit – einschließlich SOPC-Builder, Nios-II-IDE (Integrated-Design-Environment) und der Entwicklungs-Software Quartus-II –, die die Entwicklung der erforderlichen Hard- und Software beschleunigen, die nötig ist, ein komplettes, auf programmierbarer Logik basierendes System in einen programmierbaren Chip (SOPC) zu implementieren. Um diese Aufgabe zu erleichtern, erhält man mit der Nios-II-Lizenzierung ein Entwicklungs-Kit, das neben dem Soft-Prozessor-Core auch den nötigen Satz von Software-Tools enthält, um Nios-II-Designs in einem Altera-FPGA zu realisieren. Bild 3 zeigt ein typisches System für eine Cyclone-II/Nios-II-Implementierung, die sich mit dem SOPC-Builder realisieren lässt.

Der SOPC-Builder ist das Schlüsselwerkzeug, das verwendet wird, um IP in ein Altera-FPGA zu implementieren. Dieses Tool bietet eine „MegaWizard“-Funktion, um automatisch die „Avalon-Switch-Fabric“ zu generieren, die die verschiedenen Funktionsblöcke eines Designs miteinander verbindet. Der SOPC-Builder erzeugt ebenfalls ein kundenspezifisches Software-Entwicklungs-Kit, das – falls nötig – die entsprechenden Sofware-Header-Dateien für die vom Nios-II-Prozessor gesteuerten Funktionsblöcke liefert. Der SOPC-Builder befreit die Entwickler von der zeitaufwendigen Aufgabe der manuellen Verbindung und Verifizierung der Register bzw. Speicher, die in ein Design abgebildet („gemappt“) sind. Dadurch können sie sich vollständig darauf konzentrieren, wichtige Systemfunktionen zu optimieren.

Die Nios-II-IDE ist das primäre Entwicklungswerkzeug für den Nios-II-Prozessor und stellt eine integrierte Entwicklungsumgebung für die Software-Entwicklung dar. Sie umfasst eine grafische Benutzerschnittstelle, die das Projektmanagement, die Code-Entwicklung und das JTAG-basierte Debugging von den einfachsten bis zu den komplexesten Nios-II-basierten Designs ermöglicht. Zusätzliche Elemente des Werkzeugs sind ein Befehlssatz-Simulator, der es erlaubt, Code ohne ein Entwicklungs-Board zu debuggen, das Echtzeit-Betriebssystem Micro/OS II und ein einfacher TCP/IP-Stack. Die Nios-II-IDE lässt sich in Verbindung mit der Quartus-II-Software oder auch als Stand-alone-Tool einsetzen. Diese Möglichkeit des Stand-alone-Einsatzes ist besonders hilfreich für Software-Ingenieure, deren ausschließliche Aufgabe es ist, Software für den Prozessor zu schreiben.

Die Quartus-II-Software umfasst Design-Erfassungs-, Synthese-, Simulations- sowie Place&Route-Funktionen für die Hardware-Entwicklung.

Jobangebote+ passend zum Thema

Design-Beipiel Internet-Zugangssystem

Der Blick auf ein beispielhaftes Internet-Zugangssystem (Bild 3) verdeutlicht die Vorteile, die man durch ein kombiniertes Design aus Cyclone-II-FPGAs und Nios-II-Prozessoren erhält. Den dargestellten Internet-Zugang findet man u.a. in Produkten wie Video-Spiel-Konsolen, Settop-Boxen, „smarten“ Kühlschränken oder Alarmsystemen. Ein solches System kommuniziert z.B. über eine Ethernet-Verbindung und führt eine entsprechende Datenverarbeitung durch. Es umfasst kundenspezifische Peripherie, Hardware-Systemfunktionen, Verbindungslogik sowie die Bedienerschnittstelle.

Der traditionelle Weg, ein solches System zu entwickeln, bedeutet den Einsatz eines DSP, eines Ethernet-MAC/PHY, eines kleinen Mikrocontrollers und eines FPGA. Diese Methode liefert zwar die gewünschte Systemfunktion, benötigt aber mehrere I/Os zwischen dem FPGA und dem DSP, was die Entwicklung komplizierter macht. Zusätzlich erfordert ein solches Design minimal vier Komponenten (Bausteine), was relativ viel Platz auf der Platine bedeutet.

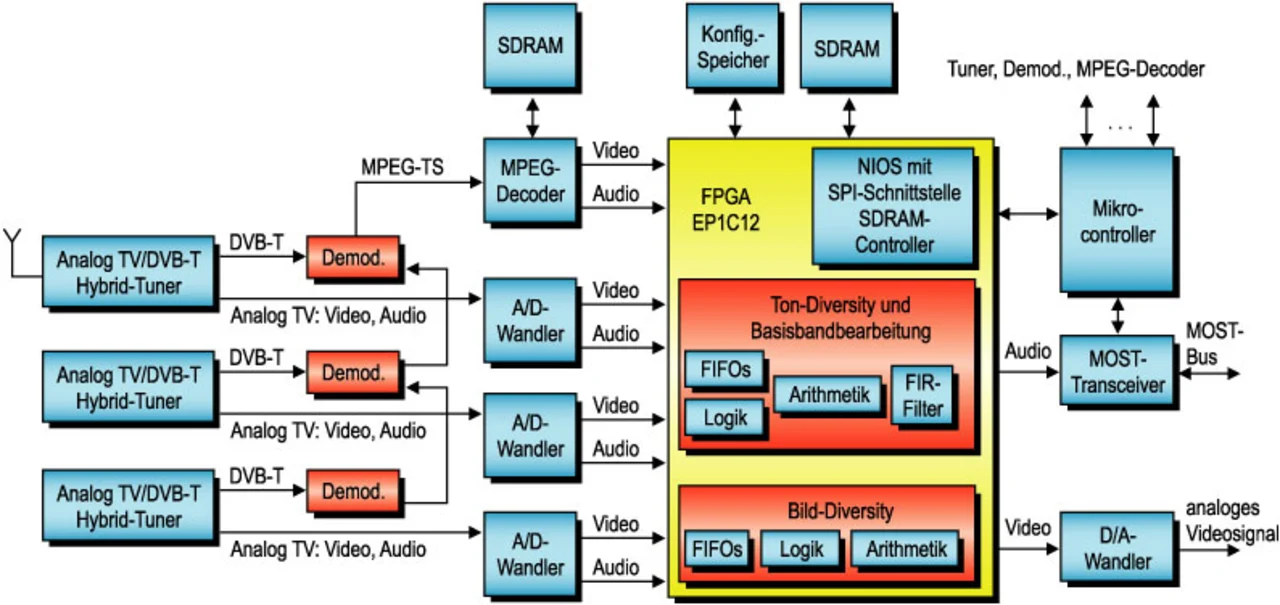

Schon mit der ersten Generation von Cyclone-FPGAs und Nios-Prozessoren konnten leistungsfähige Designs realisiert werden. Ein Beispiel ist der Auto-TV-Empfänger von Hirschmann Electronics (Bild 4), der analogen und digitalen TV-Empfang bietet. Die Cyclone-FPGAs ermöglichten hier die kosteneffektive Implementierung von DSP-Funktionen. Mit dem SOPC-Builder wurde der Nios-Prozessor entwickelt, der für die Antennen-Steuerung erforderlich war.

Doch zurück zu unserem Beispiel. Mit den Cyclone-II-FPGAs und dem Embedded-Prozessor Nios II kann man beispielsweise die DSP-Funktion in dem Nios-II-Prozessor implementieren, wodurch ein Viertel der vorher benötigten Bauteile eliminiert wird. Für sehr DSP-lastige Applikationen bietet der kundenspezifische Befehlssatz des Nios-II-Prozessors spezielle Funktionen, die in Hardware implementiert schneller ablaufen. Ist eine noch höhere DSP-Leistung gefordert, kann auch der gesamte DSP-Funktionsumfang in Hardware realisiert werden, indem man eine Kombination von Altera-IP und kundesspezifischer Hardware einsetzt. Die in den Cyclone-II-Bausteinen eingebetteten Multiplizierer können beispielsweise dazu verwendet werden, komplizierte mathematische Befehle schneller als auf Hochleistungs-DSPs abzuarbeiten. Der Nios-II-Prozessor würde in einer solchen Implementierung dann dazu eingesetzt werden, die Steuerfunktionen, die sonst normalerweise vom DSP durchgeführt werden, zu übernehmen.

Da die Cyclone-II-FPGAs (Bild 5) die dreifache Gatterkomplexität gegenüber der ersten Generation erreichen, sind sie in der Lage, noch vielfältigere und umfangreichere Funktionen zu integrieren, was die Systemintegration und die Zuverlässigkeit steigert und gleichzeitig hilft, die Systemkosten zu reduzieren. Der Nios-II-Prozessor bietet ebenfalls einen erweiterten Funktionsumfang und ein Echtzeit-Betriebssystem (RTOS), mit dem sich beispielsweise ein Web-Server aufbauen lässt, der eine Gerätesteuerung via Internet erlaubt.

Schließlich kann noch ein zweiter Nios-II-Core in dasselbe Cyclone-II-FPGA implementiert werden, um z.B. eine Tastatur und einen LCD-Treiber zu steuern. Auf diese Weise lässt sich ein MMI-Prozessor (man/machine interface) realisieren. Dieser zweite Prozessor arbeitet üblicherweise mit einer geringeren Taktfrequenz als der DSP. Durch den Einsatz von zwei Prozessor-Cores lässt sich jeder Core bezüglich Leistungsfähigkeit und -aufnahme sowie beanspruchter Siliziumfläche an die gewünschte Funktion anpassen.

Literatur

[1] Altera-Homepage: www.altera.com

Gerhard Stelzer, Elektronik

Verwandte Artikel:

- Ein starkes Team

- Einfacher Design-Flow