ARM7-Controller mit umfangreichen Schnittstellen und Analogkomponenten

32-bit-Prozessor zum Sparpreis

Fortsetzung des Artikels von Teil 1

DMA-Controller für die Peripherie

Die Leistungsfähigkeit eines Systems hängt nicht nur von der Taktfrequenz der CPU ab. Eine enge Integration von Prozessorkern und Peripherie sowie DMA-Fähigkeit (Direct Memory Access) sind wichtig, um die Gesamtleistung eines System zu erhöhen, besonders wenn Hochgeschwindigkeits-Peripheriegeräte Daten an die Außenwelt senden oder empfangen.

Eine 32-bit-Prozessor-Architektur umgeben von 8-bit-Peripheriemodulen hätte eine schlechte dynamische Leistung und einen begrenzten Durchsatz. Anstatt 8- oder 16-bit-Peripheriemodule wiederzuverwenden, baut die SAM7S-Familie auf leistungsfähigen Peripheriemodulen aus Atmels SoC-IP-Bibliothek auf, die sowohl für den ARM7TDMI als auch für den ARM926EJ-S verwendet wurden. Dies gewährleistet eine gemeinsame Programmierschnittstelle, die eine Migration von einem Kern auf einen anderen vereinfacht. Peripheriemodule wie SPI oder synchrone UARTs können dadurch einen Datendurchsatz erreichen, wie er bei solch kostengünstigen Peripherieschnittstellen bisher nicht möglich gewesen war (bis 55 Mbit/s).

Aufgrund der Echtzeit-Bedingungen bei hohen Geschwindigkeiten kann die CPU den Datenfluss in das und aus dem System nicht direkt verwalten. Eine Art von DMA-Controller wird benötigt, damit ein Hochgeschwindigkeitsdatentransfer aufrechterhalten werden und die CPU gleichzeitig andere Systemaufgaben wahrnehmen kann. Aber ein kompletter DMA-Controller auf einem Chip mit begrenzter RAM-Größe und ohne externe Busschnittstelle würde die Komplexität der Programmierung nur erhöhen.

Der AT91SAM7S umfasst daher einen „Peripheral DMA-Controller“ (PDC), der für 32-bit-Embedded-Mikrocontroller maßgeschneidert wurde. Nur automatische Transfers von der Peripherie in den Speicher und aus dem Speicher zur Peripherie sind erlaubt. Zum Einrichten des PDC müssen lediglich Quell-Peripheriemodul/Speicher und Ziel sowie die Größe des austauschenden Datenpuffers angegeben werden (bis 64 Kbyte). Der PDC übernimmt dann die Steuerung des Datenaustauschs, ohne dass die CPU eingreifen muss. Wenn dieser im Hintergrund ablaufende Vorgang beendet ist, wird die CPU durch einen Interrupt über den erfolgreichen Abschluss des Vorgangs informiert. Es können gleichzeitig mehrere PDC-Datentransfers eingerichtet werden, was die Implementierung von Brücken zwischen einzelnen Schnittstellen vereinfacht (z.B. Daten vom SPI-Bus lesen und Daten zum UART senden). Neben einer Optimierung der CPU-Auslastung vereinfacht der PDC außerdem die Integration von Peripherie-Softwaretreibern und Echtzeit-Betriebssystemen. Datentransfer im Hintergrund oder eine Datenerfassung bei angehaltenem Prozessortakt sind möglich. Neben einer Senkung der Leistungsaufnahme wird dadurch auch der Rauschpegel bei der Abtastung für eine Analog/Digital-Umsetzung verringert.

Jobangebote+ passend zum Thema

ADC mit erweiterten Anwendungen

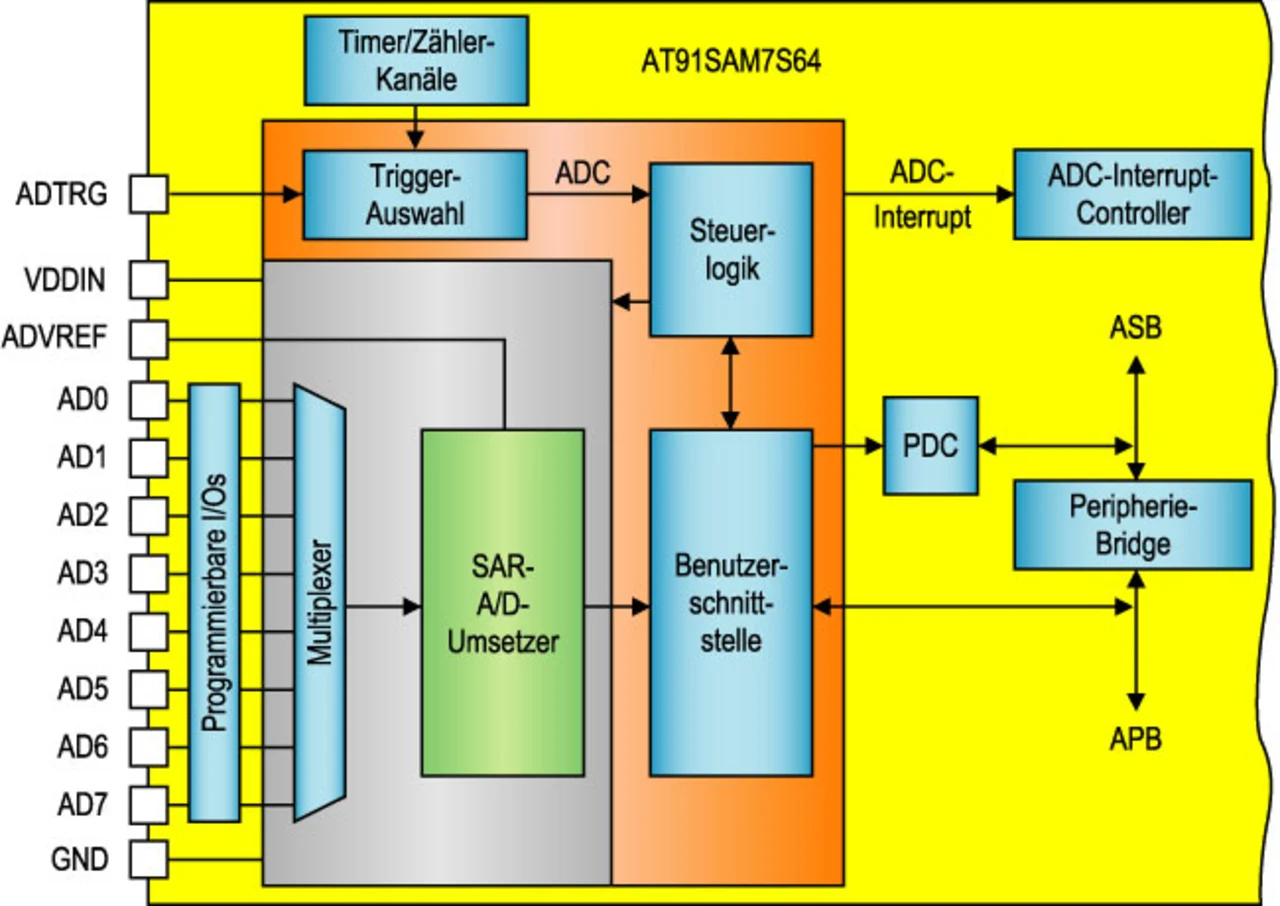

Neben der Integration einer 32-bit-CPU mit leistungsfähigen Peripheriemodulen und Flash-Speicher sind auch Analogfunktionen von besonderer Bedeutung. Wie bereits erwähnt, verfügen die Bausteine der AT91SAM7S-Familie über eine Reihe analoger Komponenten – z.B. POR, BOD und Spannungsregler, die dazu beitragen, dass diese Lösung möglichst viele Systemfunktionen integriert. Ein weiterer analoger IP-Block ist ein mit zahlreichen Funktionen ausgestatteter Analog/Digital-Umsetzer (Bild 6).

Der neue 8-kanalige 10-bit-Analog/Digital-Umsetzer mit einer Abtastrate von 384 kSamples/s wurde auf Anregung von Kunden mit einigen neuen Funktionen ausgestattet, die seine Anwendungsmöglichkeiten erweitern. Erstens nutzt der A/D-Umsetzer den PDC, wodurch die CPU frei wird für andere Aufgaben. Andere Vorteile einer Verwendung des PDC sind eine niedrige Leistungsaufnahme und ein rauscharmer Betrieb. Der A/D-Umsetzer selbst verfügt außerdem über einen automatischen Sleep-Modus, bei dem die analoge Zelle abgeschaltet wird, wenn ein Umsetzungszyklus abgeschlossen ist. In Verbindung mit seinem automatischen Kanal-Abtastmodus ermöglicht der A/D-Wandler eine Datenerfassung im Hintergrund bei niedriger Leistungsaufnahme.

Als Beispiel bietet sich ein batteriebetriebenes Gerät an, bei dem vier der acht Kanäle des A/D-Umsetzers regelmäßig abgetastet werden und die Ergebnisse in einem internen SRAM gespeichert werden müssen, bis genügend Abtastwerte für die weitere Verarbeitung zur Verfügung stehen. Die Ausführung von Code während des Abtastvorgangs verkürzt die Akku-Nutzungsdauer. Durch die Kombination der Möglichkeiten des automatischen Datentransfers über den PDC, des Auto-Sleep-Modus und der automatischen Abtastfunktion lässt sich eine effiziente Datenerfassung im Hintergrund durchführen und ein rauscharmes Verhalten während der Datenerfassung gewährleisten. Die CPU und die meisten Peripheriemodule können deaktiviert werden, wodurch das Eigenrauschen des Bausteins, das das Ergebnis der A/D-Umsetzung beeinträchtigen könnte, auf ein Minimum reduziert wird.

Das Einrichten solcher Transfers beginnt damit, dass die A/D-Kanäle aktiviert werden, die für die Erfassung benötigt werden (z.B. Kanal 1, 4, 5 und 6). Dann wird der PDC mit der Zieladresse im SRAM und mit der gewünschten Anzahl von A/D-Umsetzungszyklen konfiguriert (z.B. 200 Zyklen). Die Interrupts für den A/D-Wandler und PDC werden entsprechend konfiguriert.

Der letzte Schritt besteht in der Konfiguration des Triggerereignisses, das den Umsetzungsprozess einleitet. Eine einfache Möglichkeit, den Auto-Scan einzuleiten, ist der Einsatz eines Software-Triggers von der Hauptanwendungssoftware. Eine weitere Möglichkeit besteht in der Verwendung eines der Timer-Interrupts. Dies ermöglicht automatische Umsetzungszyklen bei jedem Timer-Time-out ohne Eingriff durch die CPU. Die letzte Möglichkeit besteht in der Verwendung des speziellen Triggereingangs-Pins, der die Steuerung des A/D-Wandlers durch externe Hardware ermöglicht.

| Dany Nativel hat an der Universität Paris VI, Frankreich, studiert und einen „Master-of-Science“-Abschluss auf den Gebieten Elektronik und Rechnertechnik erworben. Nach dem Studium war er etwa fünf Jahre als Software-Entwickler bei IBM tätig. Anschließend kümmerte er sich als Applikationsingenieur bei Infineon Technologies um Mikrocontroller für Anwendungen in der Automobiltechnik. Als Nativel zu Atmel kam, arbeitete er vier Jahre lang in Washington D.C. im Außendienst als Anwendungs-Ingenieur für Smart-Card-ICs, später als Business Development Manager für ASICs und Mikrocontroller. Heute ist er technischer Produkt-Marketing-Manager für ARM-basierte Mikrocontroller bei Atmel. E-Mail: dany.nativel@atmel.com |

Verwandte Artikel:

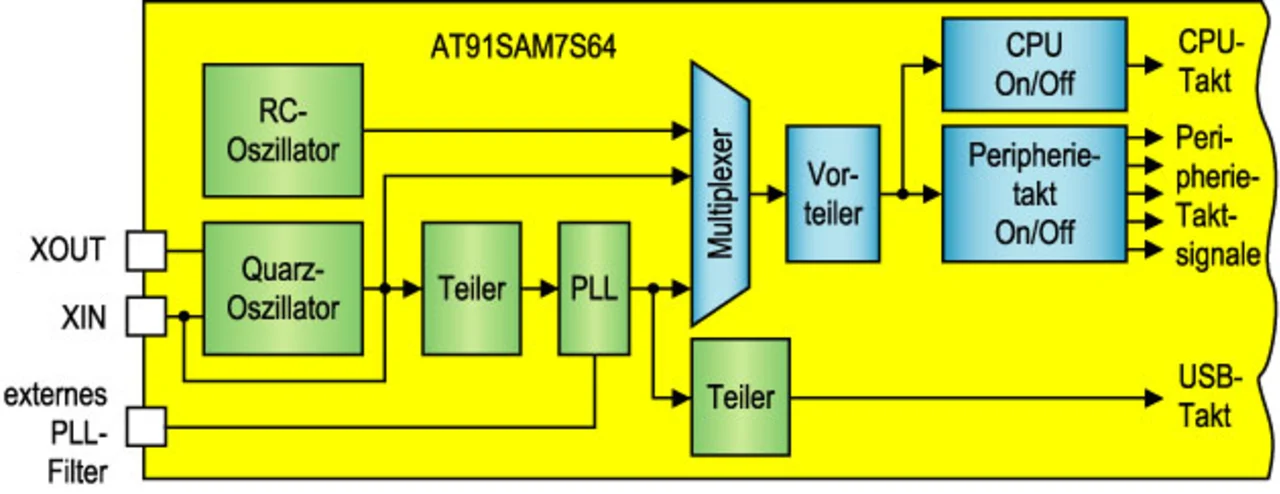

Einer der wichtigsten Faktoren für ein erfolgreiches Leistungsmanagement bei Embedded-Anwendungen ist die optimale Steuerung zweier verschiedener Taktfrequenzen (System und Peripherie). Lediglich zwei Betriebsmodi, bei denen der Chip entweder mit voller Geschwindigkeit oder vollständig abgeschaltet im Sleep-Modus arbeitet, sind heutzutage nicht mehr ausreichend. Beim AT91SAM7S ist der System-Controller um eine Hochgeschwindigkeits-PLL, Vor- und Nachteiler, Taktmultiplexer und ein Taktfreigabemodul herum aufgebaut (Bild 3).

Das der PLL zugeführte Taktsignal lässt sich mit Hilfe des Vorteilers genau justieren, der sich auf einen Faktor zwischen 1 und 255 bei einem Inkrement von 1 einstellen lässt. Die PLL selbst bietet Multiplikationsfaktoren von 1 (PLL umgangen) bis 2048 und zwei Betriebstaktfrequenzbereiche, 80 bis 160 MHz und 50 bis 220 MHz, die vom Anwender je nach dem verwendeten PLL-Multiplikationsfaktor ausgewählt werden müssen. Wie bereits erwähnt, ist es manchmal von Vorteil, wenn man den CPU-Kern mit einer extrem niedrigen Frequenz laufen lassen kann, anstatt ihn vollständig abzuschalten. Dadurch kann die vom Benutzer entwickelte Anwendung Hintergrundaufgaben durchführen und Sensoren effizienter überwachen.

Ein der PLL nachgeschalteter Taktmultiplexer bietet dem Anwender die Möglichkeit einer dynamischen Umschaltung zwischen dem PLL-Taktsignal, dem Taktsignal des Quarz-Oszillators (unter Umgehung der PLL und des Vorteilers) und dem Taktsignal des On-Chip-RC-Oszillators (niedrige Taktgeschwindigkeiten). Der USB-Takt wird direkt vom PLL-Takt abgeleitet und ist damit von der Taktumschaltung unabhängig.

Die Flexibilität, die der Vorteiler bietet, wird durch zusätzliche Nachteiler im System- und im USB-Taktpfad noch weiter erhöht. Neben der Umschaltung zwischen schnellem und langsamem Takt können einige Anwendungen das Takterzeugungsmodul des SAM7S zur Anpassung oder Modulation der Systemtaktgeschwindigkeit je nach Gesamtsystemauslastung nutzen. Dies kann die Konstruktion des Betriebssystems wesentlich vereinfachen, weil die einem „Deep-Sleep“-Modus innewohnenden Begrenzungen und die daraus resultierenden Beschränkungen für ein schnelles Aufwecken entfallen.

Zur weiteren Senkung der Leistungsaufnahme lassen sich alle Peripherie-Taktsignale einschließlich des CPU-Takts deaktivieren. Durch das Anhalten der CPU (auch als Idle-Modus bezeichnet) bleiben die ausgewählten Peripheriegeräte voll eingeschaltet und ausgewählte Interrupts können die CPU wieder aktivieren.

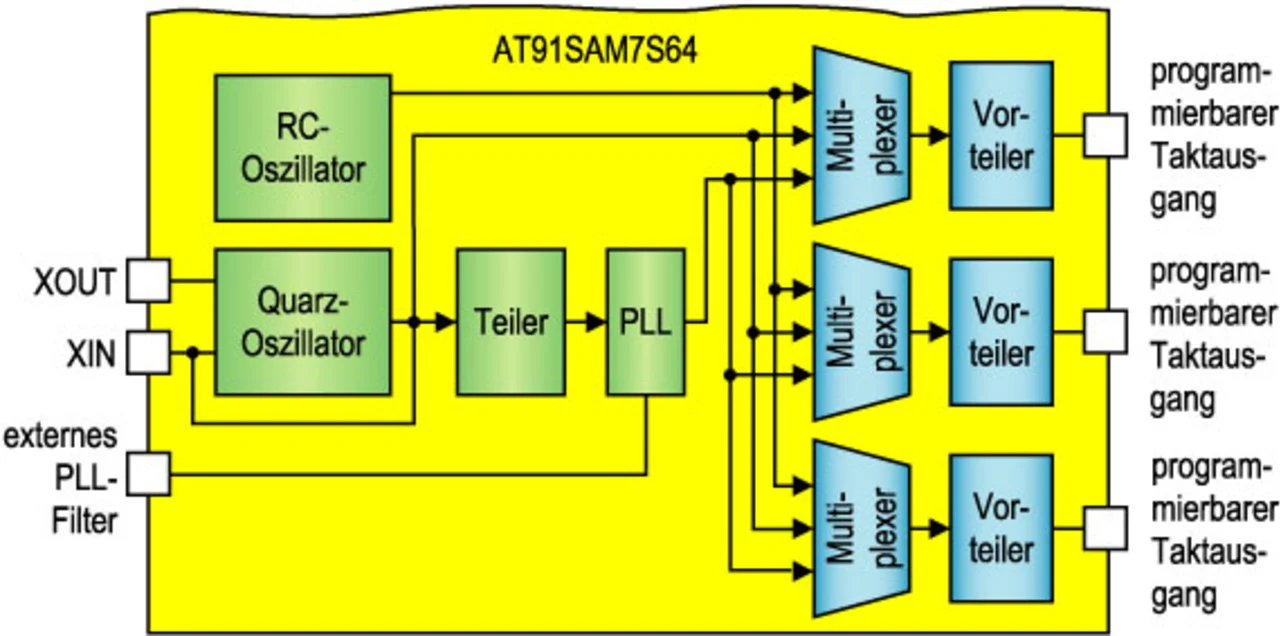

Wie aus Bild 4 ersichtlich ist, können die Chips der SAM7S-Familie außerdem Taktsignale für andere ICs auf der Leiterplatte erzeugen. Für jeden Taktausgang stehen ein separater Multiplexer und ein konfigurierbarer Taktteiler zur Verfügung. Dadurch reduziert sich die Anzahl externer Bauteile zur Takterzeugung wesentlich.

- 32-bit-Prozessor zum Sparpreis

- DMA-Controller für die Peripherie

- Eingebaute Spannungsregelung