Sicherheitskritische Embedded-Systeme

Mit FPGAs zur funktionalen Sicherheit

Fortsetzung des Artikels von Teil 2

Ausfallsicher und deterministisch

Im FPGA wird diese Redundanz nochmals wiederholt, um bei Störung eines FPGA-Flipflops dennoch die Berechnung im FPGA abschließen zu können. Das hat zur Folge, dass bei Verwendung eines Flash-basierten FPGA eine nahezu SEU-immune Implementierung realisiert werden kann. Im sicherheitskritischen Umfeld sind neben der Ausfallsicherheit zusätzlich auch berechenbare Ausführungszeiten gefragt. Das System muss in einer definierten Zeit auf ein externes Ereignis reagieren, und das sogar im Worst Case. Typische Rechnerarchitekturen verwenden jedoch Interrupts und DMA-Topologien, die die Reaktionszeiten einzelner Tasks negativ beeinflussen können, wenn eine andere Task dieselben Ressourcen anfordert. Das geforderte deterministische – also zeitlich exakt vorhersagbare – Verhalten ist dann nur schwer erreichbar. Deshalb verzichtet man bei harten Echtzeitanforderungen auf solche Lösungen. FPGAs unterstützen Echtzeitfähigkeit jedoch von Haus aus, da sie grundsätzlich parallel aufgebaut sind. Dadurch konkurrieren die verschiedenen Prozesse nicht miteinander, sondern nehmen ihren eigenen vordefinierten Weg, der durch andere Events nicht gestört wird. So lässt sich eine deterministische Echtzeitfähigkeit mit zeitlich eindeutig definiertem Verhalten viel leichter sicherstellen.

Im Kontext der funktionalen Sicherheit – englisch Safety – stößt man in Zeiten des Internet der Dinge und der Industrie 4.0 über kurz oder lang auch auf die Sicherheit im Sinne des Schutzes vor Manipulation, also Security. Auch hier bieten FPGAs viele Möglichkeiten zum Schutz der Anwendung vor Manipulation, unerlaubten Zugriff oder Vervielfältigung der Daten. Beispielsweise kann ein eindeutiger Schlüssel in das FPGA programmiert werden. Dort ist er in verschlüsselter Form in einem nichtflüchtigen Speicher sicher verwahrt. Dieser Schlüssel kann dann dafür sorgen, dass Daten nur von Anwendungen und Personen ausgelesen werden können, die diesen Schlüssel kennen. Auch kann der Schlüssel zur Identifizierung der Kommunikation des Device mit anderen Geräten genutzt werden. Dadurch, dass er hardwarebasiert ist, kann er nicht mehr softwareseitig manipuliert werden, was das Device immer eindeutig identifiziert.

Jobangebote+ passend zum Thema

In Hardware gegossener Code kann auch nicht so leicht wie Software kopiert werden. Ein FPGA kann so wertvolle Sicherheitsfunktionen übernehmen, die deutlich weiter gehen als beispielsweise ein Trusted-Platform-Modul. Neben all diesen Vorteilen von FPGAs gibt es natürlich auch Grenzen bei ihrem Einsatz. Zum einen sind die Kosten zu nennen: Sie sind teurer als Standardbausteine, die in großen Losen gefertigt werden. Auch kann man mit FPGAs nur begrenzt komplexe Lösungen umsetzen, denn ab einem gewissen Funktionsgrad ist es besser, auf eine Kombination aus Software und Hardware umzusteigen, da Mikrocontroller und Applikationsprozessoren bereits eine fundamentale Logik inklusive diverse I/O-Interfaces mit sich bringen, die man bei FPGAs erst noch entwickeln müsste. Dennoch kann man mit FPGAs natürlich auch sehr viel machen. Es ist beispielsweise so, dass es sogar schon x86-Logik in FPGAs gibt. Aber wir sind hier sicherlich noch weit davon entfernt, auch die gesamte Softwarelogik, die es für x86 gibt, in FPGAs abzubilden. Vor- und Nachteile sind deshalb je nach Anwendungsfall und vorhandenen Standardkomponenten abzuwägen. Grundsätzlich bieten FPGAs aber für nahezu alle Herausforderungen flexible und sichere Alternativen, wo man auf Hardware- oder Softwareseite schon längst an Entwicklungsgrenzen gestoßen wäre. Viele Applikationen, die auf funktionale Sicherheit bauen, können deshalb heute nicht auf FPGA-Logik verzichten.

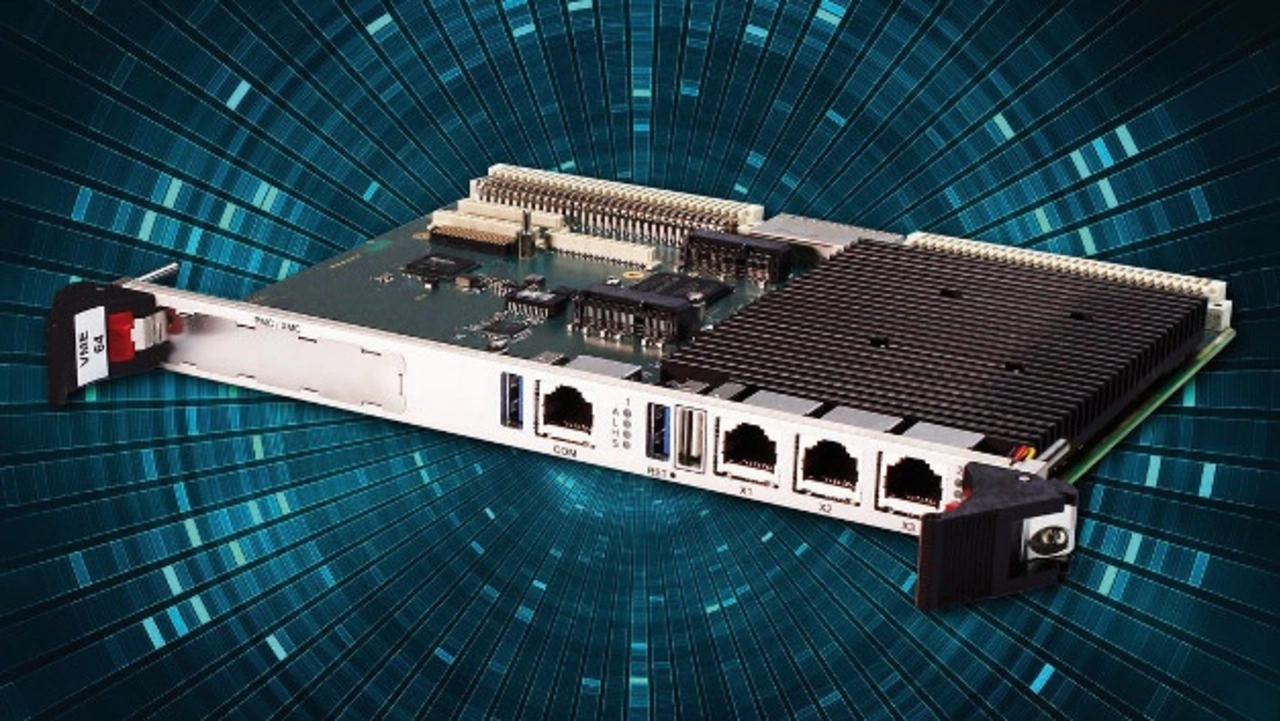

Unternehmen wie MEN Mikro Elektronik haben sich auf solche FPGA-basierten Plattformen für sicherheitskritische Embedded-Systeme spezialisiert und sind auch mit den Anforderungen der spezifischen Branchen vertraut. In manchen Branchen ist es beispielsweise üblich, dass die FPGA-Entwicklung zwar nicht in den Normen berücksichtigt wird, aber Lösungsanbieter heute sehr gerne auf die Simulationsergebnisse der FPGA-Entwicklungs-Tools zurückgreifen, um sich Dokumentationsaufwand für die Zertifizierungen zu sparen. FPGAs können also trotz allem Aufwand bei der Entwicklung auch deutlich Zeit bei den Zertifizierungsaufwendungen sparen, die mitunter aufwendiger sind als die Entwicklung selbst. Die Funktionsbausteine von MEN, die bereits in zertifizierten Applikationen im Einsatz sind, erfüllen zum einen Kernfunktionen der Boards. Zum anderen bilden sie spezifische I/O-Funktionen ab. Die IP-Building-Blocks für FPGAs von MEN umfassen beispielsweise

- Grafik- und Touchdisplay-Controller,

- Feldbus-Interfaces wie CAN und MVB,

- Unterschiedliche UARTs wie RS-232 oder RS-485,

- Ethernet- und HDLC-Schnittstellen,

- SRAM- und Flash-Speicher-Controller sowie

- GPIO, digitale I/O, Counter, Quadratur-Decoder und PWM-Funktionen.

All diese IP-Cores können mit Cores kombiniert werden, die von Altera (Avalon-Bus) oder von der Open Cores Community (Wishbone-Bus) bereitgestellt werden. Von MEN entwickelte Bridges von Wishbone-to-Avalon sowie Avalon-to-Wishbone runden das applikationsfertige FPGA-Logikangebot ab, das zudem auch noch kontinuierlich weiter entwickelt wird und selbstverständlich auch kundenspezifisch angepasst und oder erweitert werden kann.

MEN auf der embedded world 2018: Halle 1, Stand 406

- Mit FPGAs zur funktionalen Sicherheit

- Fehler-Monitoring

- Ausfallsicher und deterministisch