Modellbasierte AUTOSAR-Entwicklung

Fortsetzung des Artikels von Teil 2

Hardware-Beschleuniger für rechenhungrige Anwendungen

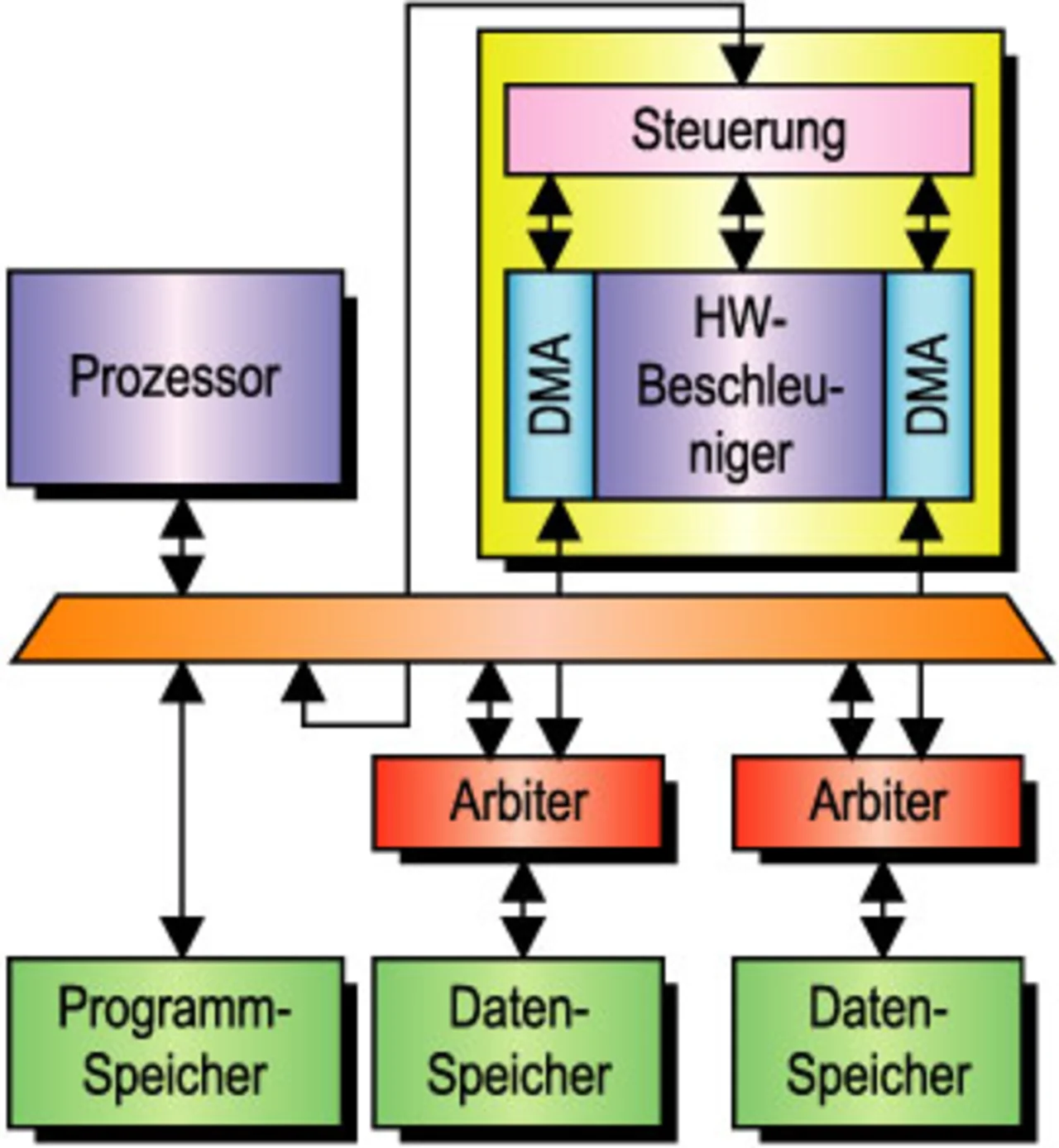

Andere Ansätze zur Steigerung der Gesamtsystemleistung bestehen zum Beispiel darin, Hardware-Beschleuniger (oder Coprozessoren), Companion-Chips für Prozessoren oder kundenspezifische System-on-Chips zu nutzen. Anders als kundenspezifische Instruktionen arbeiten Hardware-Beschleuniger als unabhängige Logikmodule, die ihre Anweisungen von der Embedded-CPU erhalten und ganze Daten-Puffer ohne Eingriff der CPU abarbeiten. Vereinfacht dargestellt, verfügt ein Hardware-Beschleuniger über zwei halbe DMA-Kanäle (einen, um die Eingangsdaten zu lesen, den anderen, um die Ergebnisse zu speichern) und ein Steuerungs-Interface für die CPU, damit sie die Einheit während des Betriebs aufsetzen, starten, stoppen und „pollen“ kann (Bild 4). Hardware-Beschleuniger sind prädestiniert für Aufgaben, bei denen große Datenblöcke involviert sind und das Laden der Daten und das Speichern der Ergebnisse durch die CPU eventuell zu einem Engpass führen könnten. Sie können gegenüber der Software-Variante die Leistung um einige Größenordnungen steigern.

Kundenspezifische Anpassung im Feld

Muss ein Produkt schnell auf den Markt gebracht werden, hat das oft zur Folge, dass die erste ausgelieferte Version weniger Funktionen umfasst und mit einer geringeren Leistung läuft als es ursprünglich geplant war. Die System-Firmware zu erneuern, um Fehler zu beseitigen, Funktionen hinzuzufügen und/oder die Leis-tung zu verbessern, ist daher heute eine gängige Praxis. Systeme, die mit programmierbarer Logik aufgebaut sind, bieten dagegen die Möglichkeit, auch die Hardware-Charakteristik relativ einfach zu ändern. Denn der gleiche Flash-Speicher, in dem die System-Software gespeichert ist, kann auch die Konfiguration für ein oder mehrere FPGAs speichern. Ein Prozessor in einem FPGA übernimmt dann die Aufgabe, den Flash-Speicher mit der Systemkonfiguration neu zu beschreiben. Anschließend kann er eine Rekonfiguration initiieren, die die System-Hardware in Millisekunden auf den neuesten Stand bringt.

Bei netzwerkfähigen Produkten lässt sich die Hardware auch über das Internet rekonfigurieren, um beispielsweise neue Funktionen zu implementieren, die Leistung zu steigern oder Fehler zu beseitigen. Das war vor ein paar Jahren noch ein Novum, heute ist es bei FPGA-basierenden Designs weit verbreitete Praxis. Fehlersichere Entwürfe, die auf mehreren, im Flash-Speicher abgelegten FPGA-Konfigurationen basieren, wobei im Fall eines Datenfehlers ein standardmäßiges, sicheres Design geladen wird, garantieren einen funktionierenden Systembaustein. Das heißt, dass im schlimmsten Fall – wenn der Baustein an der Neukonfiguration scheitert – das standardmäßige Design geladen, ein Report über den Fehler geschrieben wird und das System mit der alten Konfiguration weiterläuft.

Sicherer Systemaufbau

Prozessoren müssen mit dem Speicher, der Peripherie, Coprozessoren und externen Bausteinen kommunizieren. Software-Treiber nutzen verfügbare Mail-Boxen, damit Multiprozessorsysteme über geteilte Speicher kommunizieren können. Verschiedene Blöcke komplexer IP-Funktionen zu verbinden, kann zu Problemen führen, die die Systementwicklungszeit und die Leistungsfähigkeit negativ beeinflussen können. Zu den hierzu üblicherweise benötigten Logikfunktionen gehören Adress-Decodierer, Daten-Multiplexer, Interrupt-Controller, „Wait-State“-Generatoren, Arbitrierungslogik, Busbreitenanpassung, Signal-Timing und Pegelanpassung sowie Taktdomänen-spezifische „Crossing“-Logik.

Erfahrene Hardware-Entwickler können diese Module zwar leicht selbst entwickeln, aber solche eher einfachen Funktionen per Hand in Verilog oder VHDL zu codieren, ist eine Verschwendung wertvoller Entwicklungsressourcen. Routine-Aufgaben wie diese sind perfekte Kandidaten für die Computer-Automatisierung. Moderne Systemerzeugungs-Tools für FPGAs übernehmen diese Aufgaben problemlos und machen es möglich, dass sich Entwickler auf die Aspekte ihrer Projekte konzentrieren können, mit denen sie sich vom Wettbewerb abheben wollen.

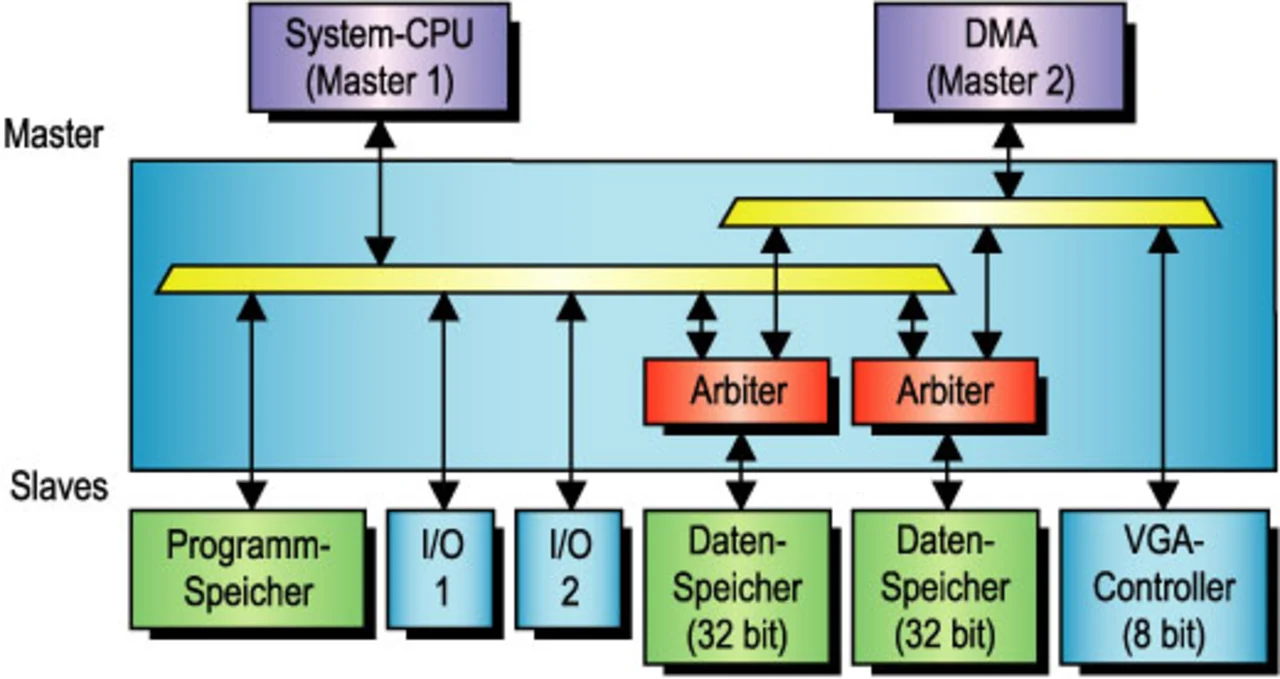

In traditionellen Embedded-Systemen teilen sich die Prozessoren einen Systembus mit anderen Master-Komponenten, die in periodischem Abstand immer wieder den alleinigen Zugriff auf den geteilten Bus fordern. Diese Verbindungstopologie stellt einen potentiellen Engpass dar, nämlich genau dann, wenn zwei Master gleichzeitig auf den Bus zugreifen müssen. FPGAs mit einem hohen Maß an Routing-Ressourcen ermöglichen Konzepte, bei denen die verschiedenen Master über dedizierte, gemultiplexte Datenpfade zu den Slave-Komponenten verfügen.

Der Wechsel von einer Master- zu einer Slave-seitigen Arbitrierung ermöglicht den Ablauf gleichzeitiger Transaktionen, außer zwei Master versuchen gleichzeitig, auf eine Slave-Komponente zuzugreifen (Bild 5). Interne Schalt-Matrix-Elemente steuern alle Verbindungen zwischen den Mastern und Slaves mit unterschiedlichen Busbreiten, mit unterschiedlichen Takt-Domainen und Verzögerungszeiten. Mit dieser „Switch“-artigen Topologie können alle Master mit ihren dedizierten Slave-Komponenten gleichzeitig kommunizieren, was den gesamten Systemdurchsatz ernorm erhöhen kann.

| Bob Garrett ist Senior Marketing Manager für die Nios-Soft-Core-Prozessoren bei der Altera Corporation in San Jose, USA. Bevor er 1999 zu Altera kam, hatte er verschiedene Vertriebs- und Marketing-Positionen bei Fluke Manufacturing und Boulder Creek Engineering inne. E-Mail: BGarrett@altera.com |

- Modellbasierte AUTOSAR-Entwicklung

- Auch für sicherheitskritische Systeme geeignet

- Hardware-Beschleuniger für rechenhungrige Anwendungen