Modellbasierte AUTOSAR-Entwicklung

Fortsetzung des Artikels von Teil 1

Auch für sicherheitskritische Systeme geeignet

Heute stehen dem System-Entwickler Embedded-IP-Funktionen (Intellectual Property) wie CPUs, Signalverarbeitungseinheiten, Peripherie und standardmäßige Kommunikationsschnittstellen, die speziell für FPGAs entwickelt wurden, zur Verfügung. Der Multiprozessor-Ansatz senkt die Bauelementekosten, indem mehrere Prozessorkerne in ein FPGA integriert werden, wodurch z.B. die Leiterplatte kleiner werden kann. Damit sind auch weniger Signalleitungen zwischen den Prozessoren auf Leiterplattenebene erforderlich, und diese einfacheren Prozessorkerne laufen noch dazu mit einer niedrigeren Taktfrequenz. Beides führt dazu, dass auch die Anzahl der Leiterplatten-Schichten reduziert werden kann.

Wenn eine Aufgabe auf mehrere Prozessoren aufgeteilt werden kann, ist es einfacher, die einzelnen Programme zu schreiben, zu debuggen und zu warten. Damit sind enorme Kosteneinsparungen möglich. Die Code-Entwicklung sowie das Debuggen gehen schneller, und wenn das Produkt eine gewisse Reife erreicht hat, kann der Code leichter modifiziert werden, weil er wesentlich einfacher zu analysieren ist.

Multikanal-Anwendungen

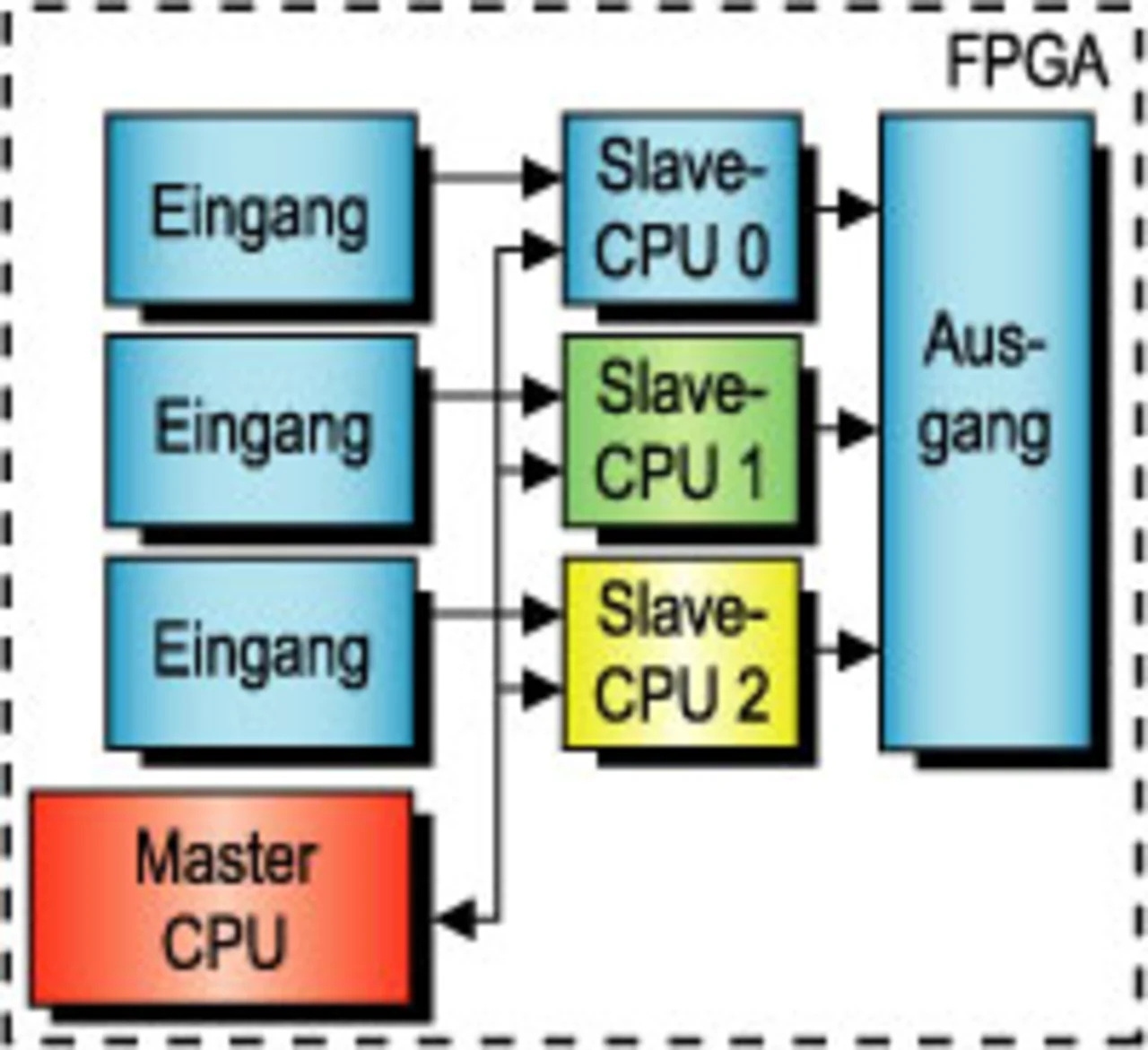

Multikanal-Anwendungen können für den erforderlichen Systemdurchsatz mit Hilfe von mehreren Prozessoren auf einem Chip skaliert werden, wobei jeder Prozessor einen Teil des gesamten Kanaldurchsatzes übernimmt. Jeder Prozessor kann entweder genau den gleichen Code abarbeiten oder einige können die Algorithmen „on the fly“ wechseln, um sich den Systemanforderungen anzupassen. In manchen Fällen ist zusätzlich ein Master-Prozessor vorhanden, der die allgemeinen Aufgaben wie Systeminitialisierung, Statistik und Fehlerbehandlung übernimmt (Bild 1).

Da sich die modellbasierte Entwicklung auch für sicherheitskritische Systeme eignet, bietet MathWorks ab sofort ein „IEC Certification Kit“ an, das helfen soll, nach IEC 61508 bzw. ISO 26262 zertifizierte Produkte zu entwickeln. Das Kit enthält Zertifikate und Prüfberichte des TÜV SÜD, die belegen, dass die Werkzeuge Real-Time Workshop Embedded Coder R2008a, b und R2009a sowie Poly-Space Verifier for C in der Version 4.2 (R2007a+) für die Entwicklung sicherheitskritischer Systeme geeignet sind. MathWorks liefert dabei Werkzeuge, die den linken Ast des V-Modells vollständig abdecken und nach jedem Prozess-Schritt eine Überprüfung des Ergebnisses bzw. einen Äquivalenztest gegenüber Modell oder Spezifikation ermöglichen. Ein entsprechender Referenz-Workflow ist verfügbar. sj

CAN-Kommunikation mit Matlab

Serielle Verbindung von Prozessorkernen

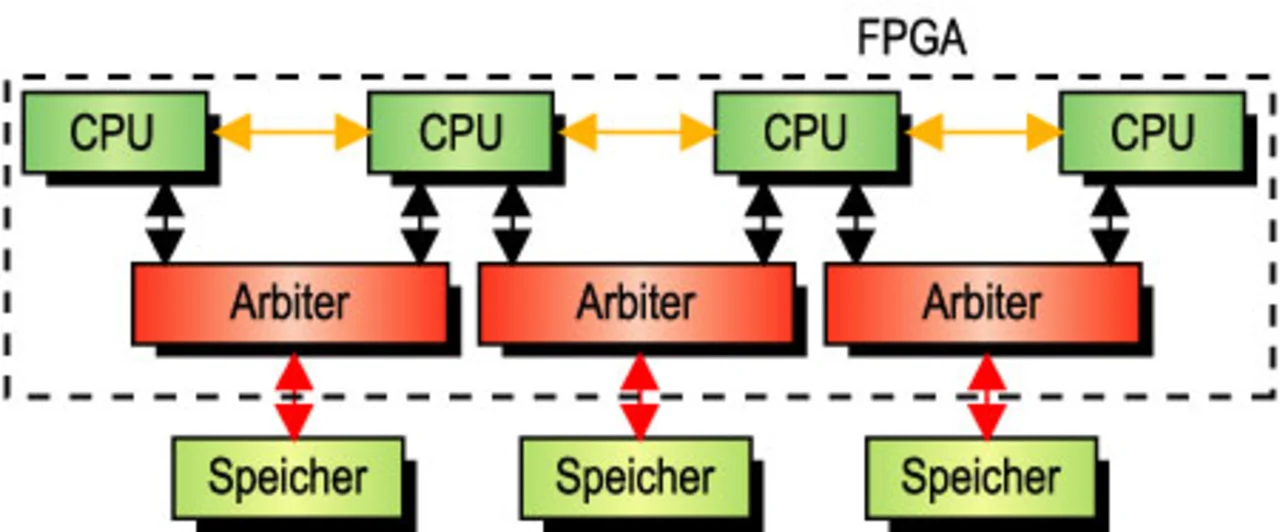

Sind einzelne Prozessoren seriell in einer Kette verbunden, behandeln Systemarchitekten jeden einzelnen als eine Stufe in einer größeren Verarbeitungs-Pipeline (Bild 2). Jede CPU ist verantwortlich für einen Teil der gesamten Verarbeitungsaufgabe und jede CPU hat Zugriff auf den Datenspeicher (arbitrierte oder dedizierte Speicherschnittstellen, wenn der Speicher extern ist, oder Dual-Ported-Speicher, wenn er sich auf dem Chip befindet), um die Ergebnisse vom Ausgang der einen Stufe zum Eingang der nächsten zu „schieben“.

Prozessor-Companion

Diskrete Prozessor- und DSP-Chips, die mit einem FPGA verbunden sind, können von einer Hardware-Beschleunigung, Peripherie-Erweiterung oder Interface-Bridge profitieren, egal ob das FPGA eine CPU enthält oder nicht. Diverse Schnittstellen-IPs für die Chip-zu-Chip-Verbindung sind verfügbar, die den externen Zugriff auf Peripherie, Beschleunigungslogik und I/O-Schnittstellen in einem FPGA ermöglichen.

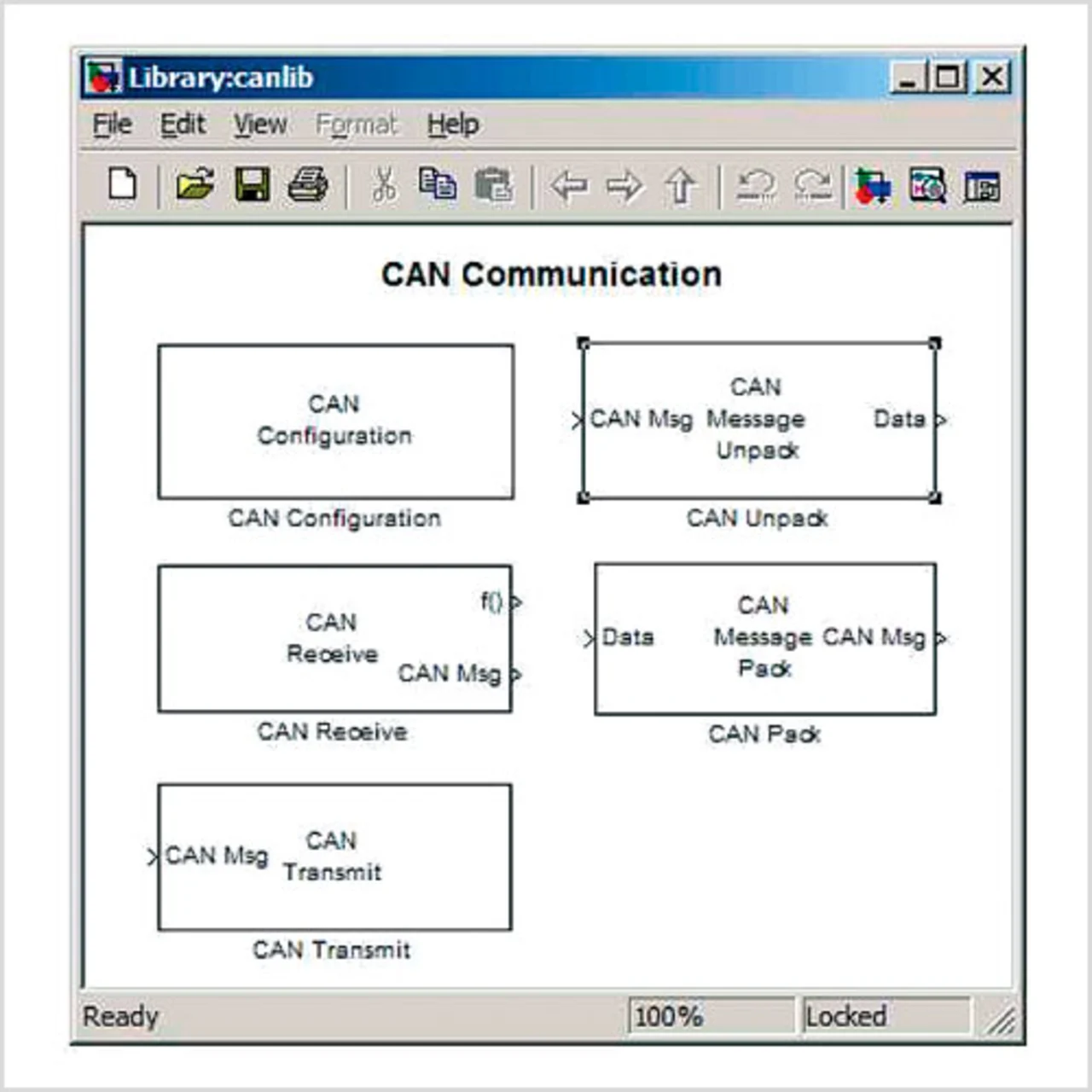

Wurde die Matlab/ Simulink-Entwicklungsumgebung bisher vorwiegend zum Entwurf und zur Simulation einzelner Subsysteme verwendet, so erweitert MathWorks sein Portfolio nun um die „Vehicle Network Toolbox“ (VNT). Damit kann nun die CAN-basierte Kommunikation zwischen verschiedenen Steuergeräten auch in Matlab/ Simulink realisiert werden. Die VNT enthält alle Funktionen, die zur Codierung, Decodierung und Filterung von CAN-Botschaften benötigt werden, und kann zudem die Netzwerk-Informationen aus einer Vector-CANdb-Datenbankdatei (*.dbc) einlesen. Zum physikalischen Anschluss an den CANBus werden verschiedene Hardware-Schnittstellen aus dem Hause Vector unterstützt, beispielsweise CANcase, CANcard oder CANboard. Eine Erweiterung auf andere Bussysteme wie z.B. FlexRay ist geplant, ein genauer Zeitpunkt steht aber noch nicht fest. Der Listenpreis der VNT liegt bei 1000 Dollar.

Erweiterung des Befehlssatzes

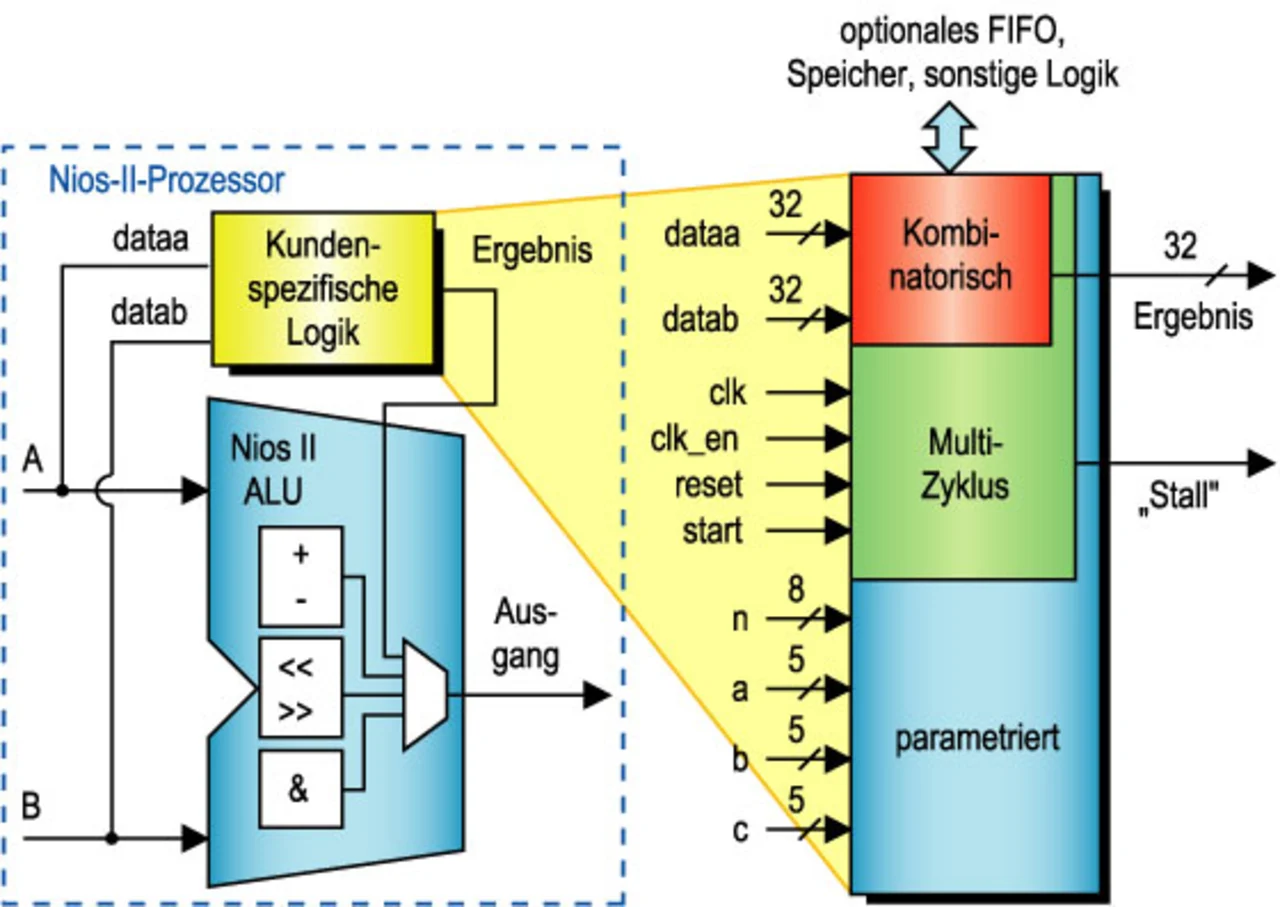

Diverse Prozessor-IP-Anbieter und FPGA-Implementierungen bieten die Möglichkeit, den Befehlssatz des Prozessors hardwaremäßig mit mächtigeren Befehlen für applikationsspezifische Algorithmen zu erweitern. Mit Hilfe der gängigen Lese-/Speicher-Operationen kann ein kundenspezifischer Logikblock mit Daten gefüttert werden, der wiederum zu einem Teil der Prozessor-ALU wird (Bild 3). In einigen Fällen können kundenspezifische Instruktionen Multizyklus-Operationen unterstützen und Zugang zu anderen Systemressourcen wie FIFOs und Pufferspeicher bieten. Typische Anwendungen kundenspezifischer Instruktionen sind beispielsweise Bit-Manipulationen oder komplexe numerische und logische Operationen.

Im Gegensatz zu einem Algorithmus, der mit Hilfe der normalen ALU-Ressourcen abgearbeitet wird, können kundenspezifische Instruktionen signifikante Leistungsvorteile bringen – und das, obwohl die normalen Lese- und Speicheroperationen des Prozessors genutzt werden. Ein Cyclic-Redundancy-Check-Algorithmus (CRC) für einen 64-K-Block mit einer kundenspezifischen Instruktion, die nur wenige Logikelemente benötigt, kann z.B. um den Faktor 27 schneller ausgeführt werden als mit herkömmlicher Software. Auf diese Weise lässt sich im System auch die Leistungsaufnahme reduzieren: Die gleichen Ergebnisse werden in gleicher Zeit, aber mit geringerer Taktfrequenz erreicht.

Wie Entwickler kundenspezifische Instruktionen erstellen können, hängt vom jeweiligen Prozessor-IP ab. Auf der einen Seite des Spektrums muss der Anwender einen neuen Compiler erzeugen, wenn er kundenspezifische Befehle hinzufügen will. Dieser kundenspezifische Compiler leitet dann die Aufrufe kundenspezifischer Instruktionen auf Basis einiger Applikationskriterien ab. Ein einfacherer, eleganterer Ansatz besteht darin, die Instruktion im C-Code aufzurufen, genauso wie eine normale Subroutine aufgerufen werden würde.

- Modellbasierte AUTOSAR-Entwicklung

- Auch für sicherheitskritische Systeme geeignet

- Hardware-Beschleuniger für rechenhungrige Anwendungen