Entwicklung und Ausblick aus Sicht eines Zulieferers

Microcontroller braucht das Auto

Fortsetzung des Artikels von Teil 2

Design für Automotive-Software

Denso hat seine MCU-Architektur mit dem Hintergedanken entwickelt, automobil-spezifische Anweisungen und C-Compiler einzuführen. Als Teil des Entwicklungsprozesses analysierte man Steuer-Software, um die Häufigkeit von lokalen Variablen, globalen Variablen, statischen 16-bit-Variablen und Argumenten, die Größe von Bit-Feldern usw. herauszufinden. Ohne eine hinreichende Codedichte würden die MCUs mehr teure ROMs oder Chip-Speicher benötigen. Denso behauptet, dass der Code, der für die eigenen automotiven MCUs compiliert wird, mindestens 15 Prozent kleiner ist als Code, der für MCUs der Wettbewerber compiliert wird.

Um den Befehlssatz für automotive Anforderungen zu optimieren, wurde Densos proprietäre NDR-Architektur in einigen Bereichen verändert. Es handelt sich um eine Harvard-Architektur (getrennter Speicher für Programmcode und Daten) mit einer fünfstufigen Pipeline. Während die meisten RISCArchitekturen 32 Allweckregister mit jeweils 32 bit beinhalten, hat NDR nur 16 derartiger Register. Zusätzlich gibt es ein so genanntes 32-bit-Spezialregister und ein 4-bit-Systemregister. Das Spezialregister enthält 24-bit-Programmcode und 8 Flags, das 4-bit-Systemregister ein Einzelschritt-Flag, ein Monitor-Flag, ein Fehlerflag, das eine Adressierung außerhalb des festgelegten Adressraumes anzeigt, und ein weiteres Fehlerflag, das einen unbekannten Befehl anzeigt.

Der Befehlssatz folgt generell dem klassischen RISC-Modell, allerdings enthält er sowohl 16- als auch 32-bit-Befehle, wobei mehr 16-bit- als 32-bit-Befehle existieren. Der Befehlssatz entspricht einer RISC-Load-Store-Architektur, d.h., der Prozessor stellt eigene Befehle zur Verfügung, die den Zugriff auf den Speicher ermöglichen und um den Inhalt des Speichers in Register speichern. Mit dem Rest der Befehle kann nur auf Register, Schnittstellen oder Zahlenwerte (Immediate Value) zugegriffen werden. Des Weiteren sind spezielle Befehle für die Operationen Integer-Multiplikation, Integer-Division, Multiplikation und Addition (MAC) sowie Gleitkommaberechnungen vorhanden.

Navigation erfordert High-End-MCU

Konsumentenelektronik-Hersteller benutzen zahlreiche unterschiedliche MCUs für DVD-Spieler, Digitalkameras und andere Produkte. Selbst für unterschiedliche Produkte eines Herstellers finden sich verschiedene MCUs. Da unterschiedliche MCUs in der Regel auch unterschiedliche Entwicklungs-Tools und Software erfordern, ist die Wiederverwendkarkeit der Software sehr eingeschränkt.

Denso versucht hingegen, Standards für unterschiedliche MCUs über unterschiedliche Produktlinien zu schaffen, damit die Investitionen in die Software geschützt werden können. Die Standardisierung ist speziell in der Automobilindustrie wichtig, da die Autos zunehmend immer mehr Konsumentenelektronik enthalten, die relativ häufig leistungsstärkere MCUs erfordert als einfache Steuersysteme. Eine dieser Anwendungen ist ein Navigationssystem, das eine High-End-MCU mit flexibler Upgrade-Möglichkeit erfordert.

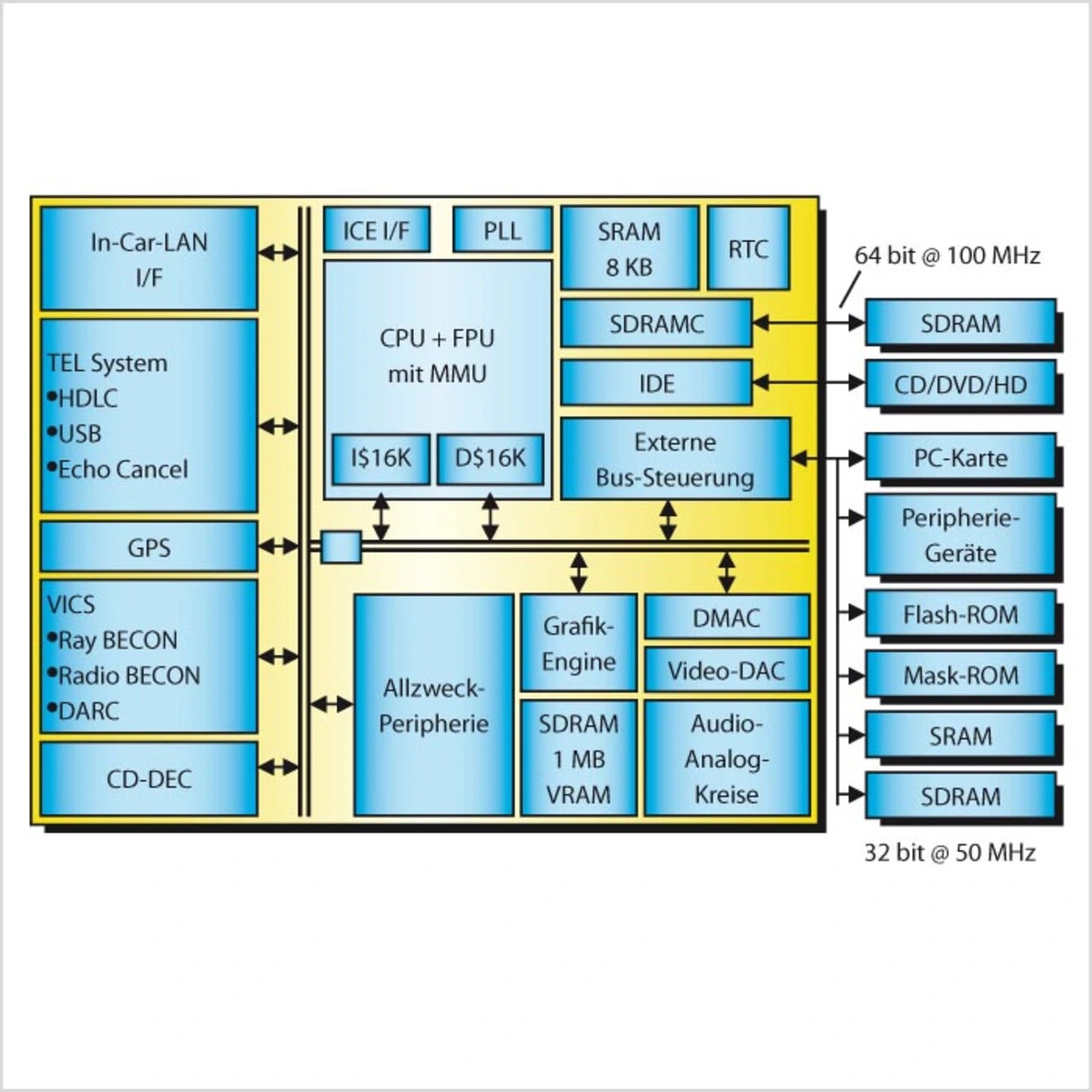

Bild 4 zeigt eine MCU, die für ein Navigationssystem entwickelt wurde. Der Chip integriert einen Prozessor, FPU, Speicher-Management-Einheit (MMU), Peripherie, 1 Mbyte Video-RAM, einen DMA-Controller, einen GPS-Empfänger, Audio-Bausteine, eine Graphics-Engine, zahlreiche I/O-Schnittstellen wie LAN und USB und einen VICS-Empfänger (Vehicle Information and Communication System, siehe Kasten). Des Weiteren befinden sich 8 Mbyte Embedded DRAM und 1,4 Millionen Logik-Gatter auf dem Chip. Der 0,18-μm-CMOS-Chip wurde gemeinsam mit Toshiba entwickelt. Der GPS-Navigator hebt sich insoweit von „gewöhnlichen“ GPS-Chips ab, indem die Positionsfehler dadurch verringert werden, dass das vom Satelliten empfangene Signal mit einem Signal abgeglichen wird, das von einer terrestrischen Station gesendet wird.

Zwei typische Einsatzbeispiele für Mittelklasse- und Low-End-MCUs sind Airbag-Steuerung und „Body Electronics“ wie Innenraum-Steuergeräte (z.B. Sitzverstellung), Wegfahrsperren und Karosseriesteuerung (z.B. Scheibenwischer, Innenbeleuchtung und Türschließmechanismus). Die hier zum Einsatz kommenden MCUs von Denso beinhalten einen V850-Prozessor-Core von NEC und proprietäre Pheripherie von Denso (Bild 1). Dieser 0,25 μ-Mixed-Signal-CMOS-Chip benutzt den Flash-Speicher für die Speicherung von Programm-Code und -Daten und SRAM für Daten, die einen schnelleren Zugriff benötigen.

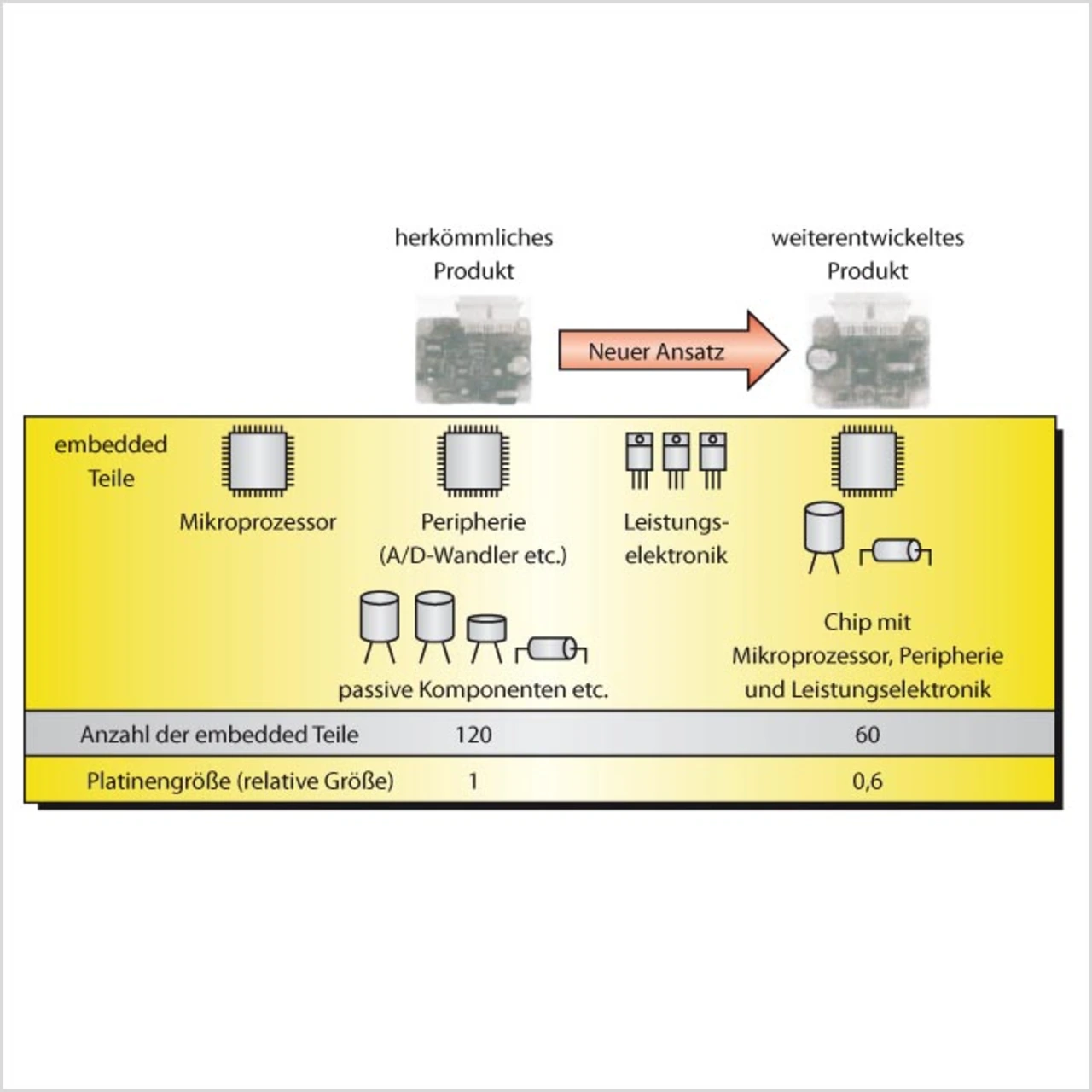

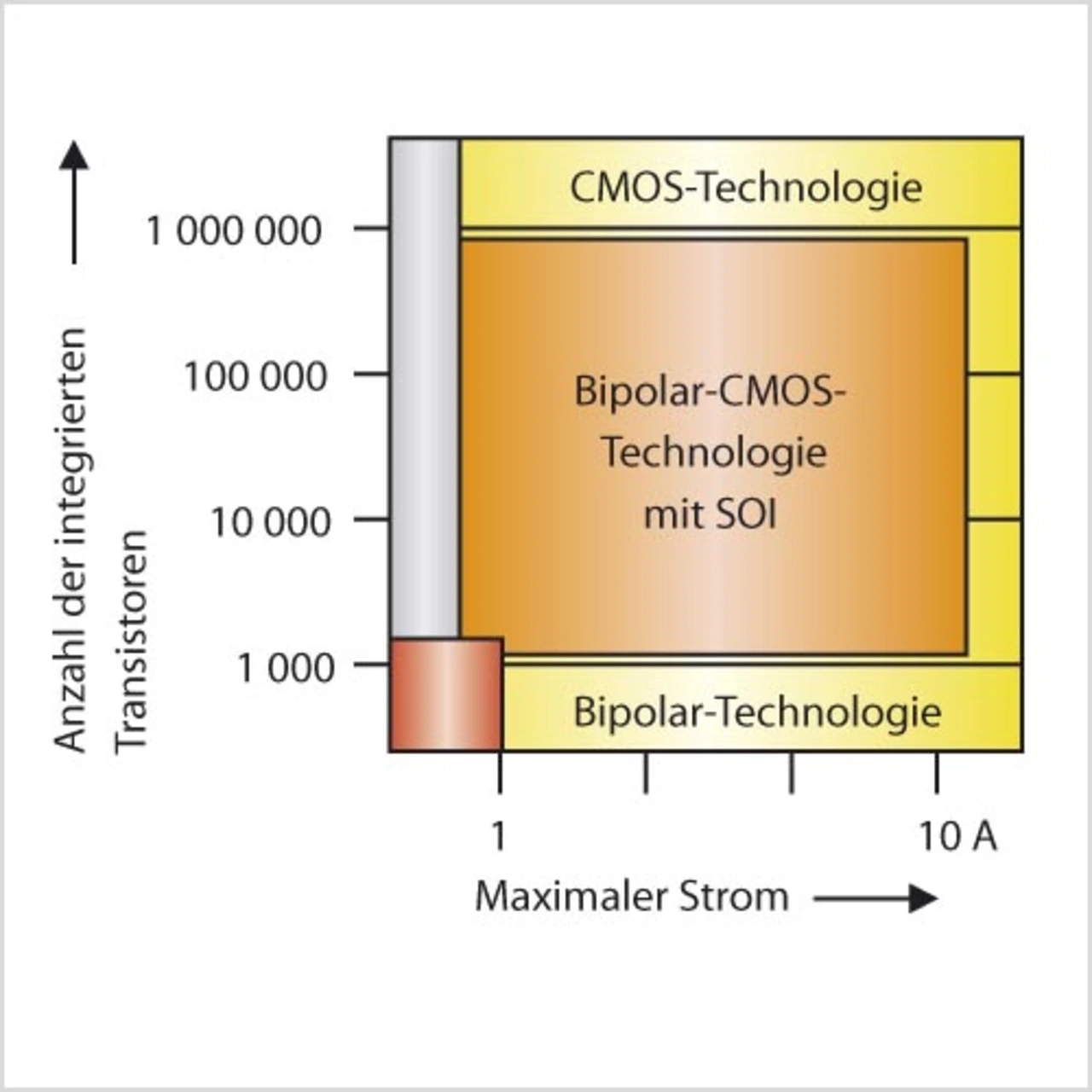

Bislang bestand ein Steuergerät für die Airbag-Steuerung aus rund 120 Teilen: Neben dem Mikroprozessor gab es noch einen separaten Chip für die Peripherie: z.B. für A/D-Wandler, Komponenten der Leistungselektronik (Power-MOS) und passive Komponenten. Ein neuer Airbag-Steuerungs-Chip integriert die MCU, Mixed-Signal-Komponenten und Power-MOS-Transistoren. Insgesamt konnte die Zahl der Teile auf 60 und die Platinengröße um 40 Prozent reduziert werden (Bild 2). Der NDR (Nippon Denso RISC) genannte 32-bit-Mikroprozessor wurde speziell für den Automobilbereich optimiert. Um die Power-MOS-Transistoren von der Logik und den analogen Schaltkreisen zu isolieren, die im Niedrigspannungs-Bereich arbeiten, stellt Denso die Chips in einem SOI-Prozess (Silicon-On-Insulator) her. Wie in Bild 3 ersichtlich ist, kombiniert dieser Prozess den Vorteil von CMOS (hohe Anzahl Transitoren) mit hohen möglichen Strömen.

Auch dieser Chip enthält ROM, Flash-Speicher und SRAM für eine beschleunigte Datenübertragung von und zur CPU. Die relativ geringe Übertragungsrate wird durch einen Betrieb im Interleaved-Modus beschleunigt. Dabei wird der Speicher in mehrere Bänke unterteilt, wobei die Adresse i in einer Bank mod i liegt. Dann liefert eine Speicheradresse bei gleicher Busbreite so viele Einheiten, wie Bänke existeren. Konventionelle Cache-Architekturen sind im Echtzeit-Betrieb nicht sinnvoll, da die Anzahl der Cache-Hits durch häufige Interrupts sehr begrenzt wäre.

Interner Chip-Speicher ist für alle MCUs im Automobil-Umfeld wichtig. Auf der anderen Seite verbraucht er viel Silizium. Densos NDR-Serien haben 192 Kbyte Speicher, der auf dem Chip zehnmal soviel Fläche benötigt wie der Prozessor-Core. Daher konzentriert sich Denso darauf, den Umfang der Software für seine ECUs zu verkleinern, um Speicher und damit Die-Fläche und Energieverbrauch zu reduzieren.

- Microcontroller braucht das Auto

- Microcontroller braucht das Auto

- Design für Automotive-Software