Modulare antriebsregelung für Servoantriebe

FPGAs in der Automatisierung

Fortsetzung des Artikels von Teil 1

Baugruppen eines Servoantriebs

Der Stromregler ist das Fundament eines Servoantriebs. Nur mit einer schnellen Stromregelung kann ein dynamisches Motion-Control-System aufgebaut werden. Die Bandbrei-te des Stromreglers ergibt sich aus zwei Kennzahlen: Abtastfrequenz bzw. Schaltfrequenz der Endstufe sowie Zeitkonstanten des Regelalgorithmus.

Für eine schnelle Stromregelung wäre eine möglichst hohe Schaltfrequenz optimal. Um die Schaltverluste zu begrenzen, beträgt die Schaltfrequenz heutiger Umrichter meist ca. 5 bis 20 kHz. Durch prädiktive Regel-algorithmen können die Zeitkonstanten der Strommessung und der digitalen Regelung kompensiert werden.

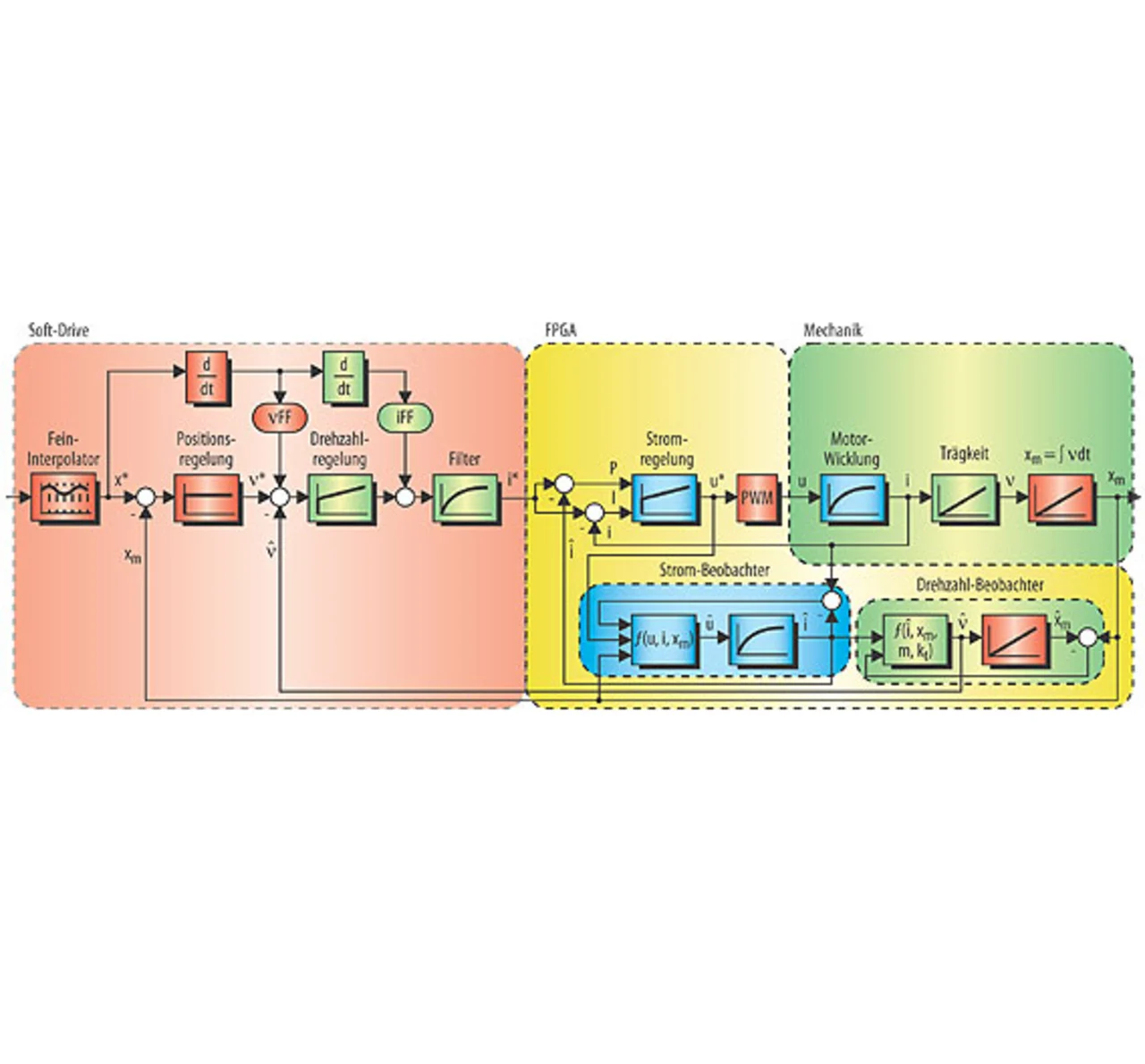

In [1] wurde ein neuer Stromregler mit folgenden Eigenschaften vorgestellt: Patentierte zweikanalige schnelle und genaue Stromregelung, Strom-Beobachter zur Kompensation der Filterzeitkonstanten und Berechnung der Algorithmen in programmierbarer Logik (VHDL).

Der Stromregelkreis ist in einem FPGA in VHDL mit 16/32-bit-Festkomma-Arithmetik codiert. Der Strom wird mit isolierenden Sigma-Delta-Modulatoren zweiter Ordnung mit 20 MHz abgetastet. Zur Unterdrückung von EMV-Störungen wird ein zusätzlicher mit der gleichen Frequenz getakteter Luenberger-Beobachter für den Motorstrom eingesetzt. Dadurch steht die Regelgröße Strom EMV-gefiltert und trotzdem nahezu verzögerungsfrei (wenige ns) zur Verfügung.

Die Regelung in Feldkoordinaten (Id, Iq) erfolgt für beide PI-Regler zweikanalig. Der P-Anteil nutzt das unverzögerte Stromsignal des Beobachters für eine möglichst große Phasenreserve. Der I-Anteil nutzt ein normal gefiltertes (sinc³, 10 μs) über eine PWM-Periode integriertes Signal für eine hohe stationäre Genauigkeit und einen geringen Offset und kann dadurch Störungen, wie sie z.B. bei langen Motorkabeln vorkommen, vollständig unterdrücken (Bild 1).

Die Bandbreite dieses Stromreglers ist direkt proportional zur Schaltfrequenz der Leistungshalbleiter. Zur Entwicklung und zum Test von Regelalgorithmen kann es sinnvoll sein, den Stromregler über einen Echtzeit-Ethernet-Feldbus zu schließen, aber die erreichbare Bandbreite verringert sich dadurch.

Es ist ein großer Vorteil, wenn der Drehzahlregler die Regelgröße (Drehzahl-Istwert) von einem Luenberger-Beobachter erhält. Dieser Beobachter kann mit 32/64-bit-Festkomma-Arithmetik codiert werden. Weil die schnellen, hochfrequenten Änderungen durch die Integration der Beschleunigung (~ Strom) erfolgen und die vergleichsweise langsameren durch eine Differentiation der Lageinformation, ist es vorteilhaft, den Beobachter in die gleiche Baugruppe wie den Stromregler zu platzieren. Der gemessene Strom kann dann unverzögert verarbeitet werden, die Lage kann mit einer geringen Verzögerung über den Feldbus bereitgestellt werden.

Auch wenn sensorlose Algorithmen immer bessere Ergebnisse erzielen, ist bei den meisten Servo-Applikationen ein Rotorlagegeber erforderlich. Der „unkaputtbare“ Resolver ist insbesondere in Europa beliebt. Eine FPGA-basierte Resolver-Digital-Umsetzung (RDC) ist flexibel wie eine MCU-Software-Implementierung und bietet aber zusätzlich eine ebenso gute Stör-unterdrückung wie die analogen, integrierten Bausteine. Encoder mit voll digitaler Schnittstelle, wie BiSS, EnDAT oder Hiperface-DSL, werden fast immer über programmierbare Logik (FPGA) angesprochen.

Die Auswertung des Motorfeedbacks kann vorteilhaft im gleichen FPGA erfolgen wie die Stromregelung. Das ist aber nicht unbedingt notwendig. Wenn die Baugruppen über ein schnell getaktetes Echtzeit-Ethernet - z.B. EtherCAT XFC mit 16 kHz - vernetzt werden, ist das, verglichen mit den heute üblichen Antrieben, nicht langsamer.

Drehzahl- und Lageregelkreis

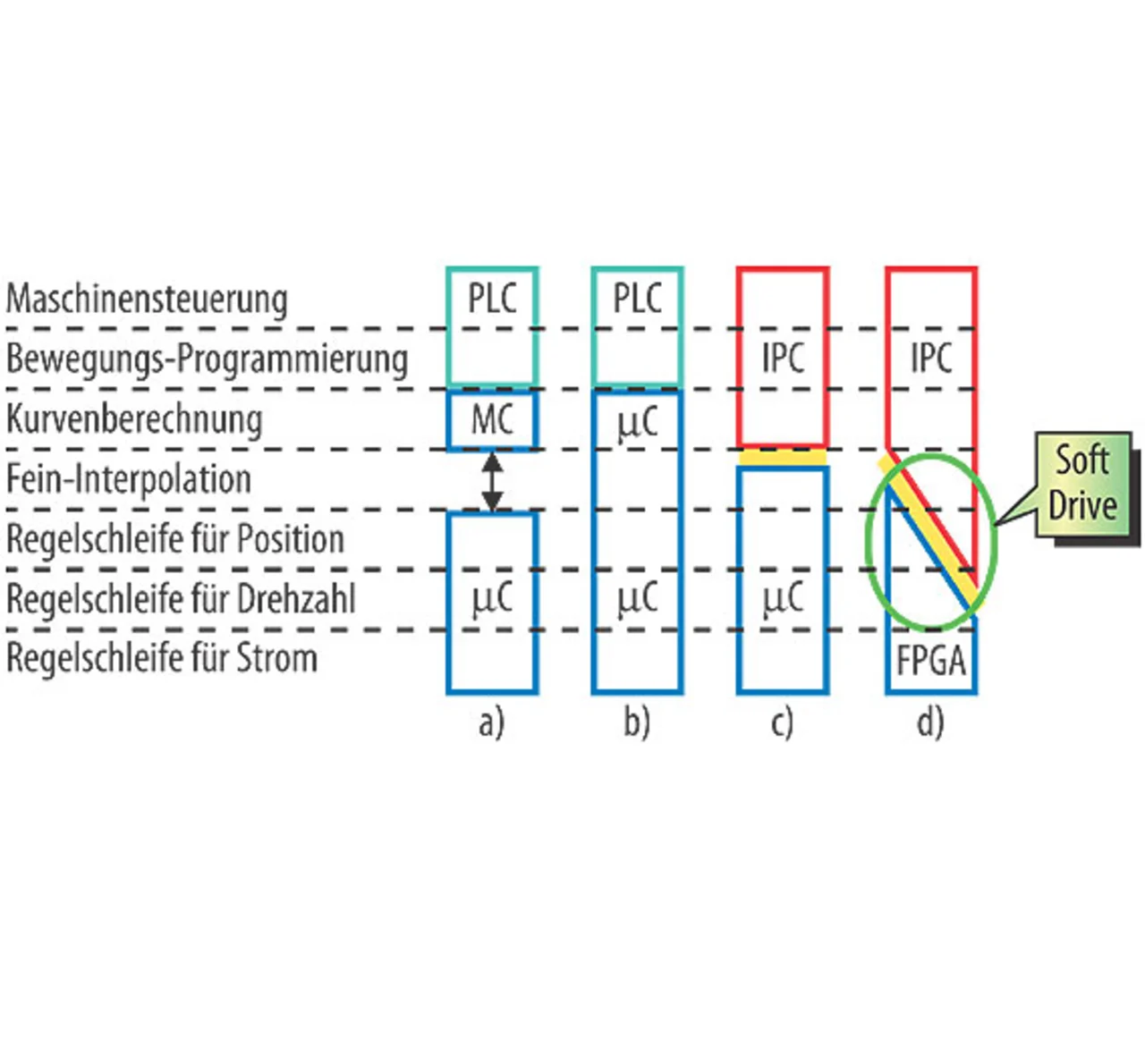

Basierend auf einem sehr schnellen Stromregelkreis können Drehzahl- und Lageregelkreis alternativ im Servoregler und/oder zentral in einer überlagerten Steuerung geschlossen werden (Bild 2).

Beim Drehzahl- und Lageregler ist es nicht ganz so selbstverständlich, dass die Algorithmen in einer Hardware-Beschreibungssprache codiert werden. Hier muss abgeschätzt werden, ob eine dezentrale, parallel ausführbare Signalverarbeitung in Hardware oder eine sequenzielle mit Hilfe einer schnellen CPU sinnvoll ist. Auch ist zu entscheiden, ob die Algorithmen in Festkomma- oder Gleitkomma-Arithmetik codiert werden sollen. Die höchste Regelkreisbandbreite und geringste Feldbuslast werden erreicht, wenn die Regelkreise ohne nennenswerte Totzeit z.B. in einem FPGA geschlossen werden. Volle Flexibilität und freie Programmierbarkeit bieten in der überlagerten Steuerung (IPC) implementierte Regelkreise. Eine solche Konfiguration erlaubt auch aufwen-dige Algorithmen und IP. Ein zweiter Encoder oder ein Ferraris-Sensor lassen sich problemlos über den Echtzeit-Ethernet-Feldbus integrieren. Nachteilig ist eine zusätzliche Totzeit von standardmäßig zwei Buszyklen, die die Regelkreisbandbreite des Drehzahlreglers verringert. Bei besonders schnellen Feldbussen können Regelgröße und Stellgröße vor bzw. nach der Berechnung des Regelalgorithmus in nur einem Abtastzyklus übertragen werden, z.B. bei EtherCAT eXtreme Fast Control (XFC). Das halbiert die Totzeit auf nur noch einen Abtastzyklus. Ein neuer Ansatz ist ein hybrider Drehzahlregler, der zum Teil im Antrieb und teilweise in der Steuerung geschlossen wird. Auch komplexere Algorithmen lassen sich zwischen Servoregler und Steuerung so aufteilen, dass die Buszykluszeit regelungstechnisch - exakt oder zumindest näherungsweise - kompensiert wird.

Für eine möglichst geringe dynamische Nachgiebigkeit (= „steife Achse“) sind hohe Kreisver- stärkungen und damit auch hohe Abtastraten erforderlich. Diese Abtastrate ergibt sich direkt aus der Schaltfrequenz der Leistungselektronik. Wenn jeder Satz Schaltflanken der drei Motor-phasenspannungen separat berechnet wird, ist fa = 2∙f s, also z.B. 16 kHz Abtastfrequenz bei 8 kHz Schaltfrequenz.

Betrachtet man andererseits den gewünschten Verlauf der Führungsgrößen (Sollwerte) hinsichtlich des Abtasttheorems, so ist keine so hohe Abtastrate erforderlich. Die von einem Motion-Controller (CNC) zu berechnende Führungsgrößenfolge kann deshalb mit einer deutlich niedrigeren Frequenz generiert werden. 1 kHz ist heute Standard, 4 kHz sind auch für sehr dynamische Anwendungen fast immer ausreichend.

Bei Werkzeugmaschinen ist es seit vielen Jahren üblich, dass diese mit verschiedenen Abtastraten mit einem Fein-Interpolator überbrückt werden. Aus der Soll-Wertefolge der CNC werden mit Hilfe einer Spline-Interpola-tion Zwischenpunkte berechnet. Das ist viel ressourcen-sparender, als wenn die CNC mit vollem Drehzahlreglertakt gerechnet würde - auch wenn das heute bei den hohen Feldbusbandbreiten möglich wäre. Der Fein-Interpolator berechnet zusätzlich noch die Geschwindigkeits- und Beschleunigungsvorsteuerung, um den Schleppfehler zu minimieren.

Trajektoriengenerierung und Safety

Bei den etablierten Feldbussen war es notwendig, die geringe zur Verfügung stehende Bandbreite effizient zu nutzen. Deshalb wurde über den Feldbus oft nur ein Fahrbefehl-Kommando übertragen. Die Trajektorie mit ihrer Sollwertfolge wurde dann erst im Servoregler berechnet. Bei Robotern oder bei Werkzeugmaschinen wurde dieses Verfahren nicht verwendet.

Außer einer Not-Rampe für gesteuertes Stillsetzen im Falle eines Feldbusfehlers ist heute eine Trajektorien-Generierung im Servoregler nicht mehr erforderlich. Wird diese zentral in der Steuerung generiert, sind Mehrachs-Synchronisation, Override, Monitoring usw. viel einfacher umsetzbar.

Aktuell werden die Produkte zum sicheren Betrieb von Maschinen und Anlagen von zwei Richtungen geprägt: sichere Antriebstechnik und sichere Feldbusse.

Es ist absehbar, dass von den Maschinenkonstrukteuren durchgängige Sicherheitsfunktionen - vom Feldbus bis zur Endstufe - erwartet werden. Durch die höheren Kosten werden nicht alle Safety-Merkmale standardmäßig angeboten. Vielmehr ist davon auszugehen, dass ein Teil optional, z.B. mit einer zusätzlichen Leiterkarte, realisiert wird.

Durch die hohen Fixkosten für die Zertifizierung der Sicherheitsfunktionen werden in Zukunft sicherlich weniger verschiedene Feldbusse angeboten werden. Da der notwendige Overhead des Safety-Protokolls die nutzbare Bandbreite reduziert, wird es gerade im Motion-Control-Bereich noch wichtiger, einen schnellen Echtzeit-Ethernet-Feldbus zu nutzen. Wenn die Regelkreise auch dezentral geschlossen werden sollen, ist es notwendig, dass die Verarbeitungszeiten so klein wie möglich sind. Optimal ist es, wenn Stromregler und Feldbus-IP in einem FPGA platziert werden.

Lage- und Drehzahlregelkreis in einem verteilten System

Durch die Verteilung der Regelkreise wird es möglich, die Ressourcen eines Automatisierungssystems je nach Anforderung optimal zu nutzen. Primäres Ziel ist, den Maschinenkonstrukteur von der Hardware - also Rechenleistung und Feldbuskommunikation - zu abstrahieren. Die für den Anwender transparente Verwaltung der notwendigen Ressourcen erfolgt in der Automatisierungs-Software TwinCAT.

Für den Anwender ist es sekundär, wo die Regelkreise geschlossen werden. Wichtig ist, ob die geforderten Eigenschaften auf wirtschaftliche Art und Weise zur Verfügung stehen. Für die Parametrierung über die einheit-liche Benutzerschnittstelle ist nicht relevant, in welchem Gerät die Regelkreise geschlossen werden. Eine andere Konstellation beeinflusst die Regelkreisparameter ähnlich wie ei-ne Umschaltung der IGBT-Taktfrequenz.

Unabhängig von der Regelkreisstruktur kann eventuell erforderliche Sicherheitstechnik - zum Beispiel über eine optionale Leiterkarte - implementiert werden.

Bei der Gestaltung der Komponenten sind folgende Aspekte ausschlaggebend: Viel Rechenleistung zu relativ geringen Kosten stellen x86- bzw. ARM-Prozessoren bei nicht ganz so hohen Anforderungen an die Rechenleistung bereit. Diese Prozessoren sind sehr gut für die zentrale Maschinensteuerung geeignet. Außerordentlich schnelle Signalverarbeitung bei überschaubaren Anforderungen können mit programmierbarer Hardware realisiert werden.

FPGAs sind deshalb sehr gut geeignet für I/O, Resolver- bzw. Encoder-Schnittstellen und zur Stromregelung bei Antrieben. Ein Kompromiss bezüglich Ausführungsgeschwindigkeit und Ressourcenbedarf sind Soft-Core-Prozessoren, die zum Beispiel gut Service-Daten-Objekte (SDO) bearbeiten können (EtherCAT Mailbox).

Der so genannte Soft-Drive enthält die Algorithmen von Drehzahl- und Lageregelkreis sowie Feininterpola-tion und Vorsteuerung. Je nach Anforderung können diese Algorithmen - nach Art eines verteilten Systems - entweder im Servoregler oder zentral in der Steuerung abgearbeitet werden. Bei einer Ausführung im Servoregler ist bei einfachen Algorithmen eine Ausführung in Hardware (FPGA) möglich.

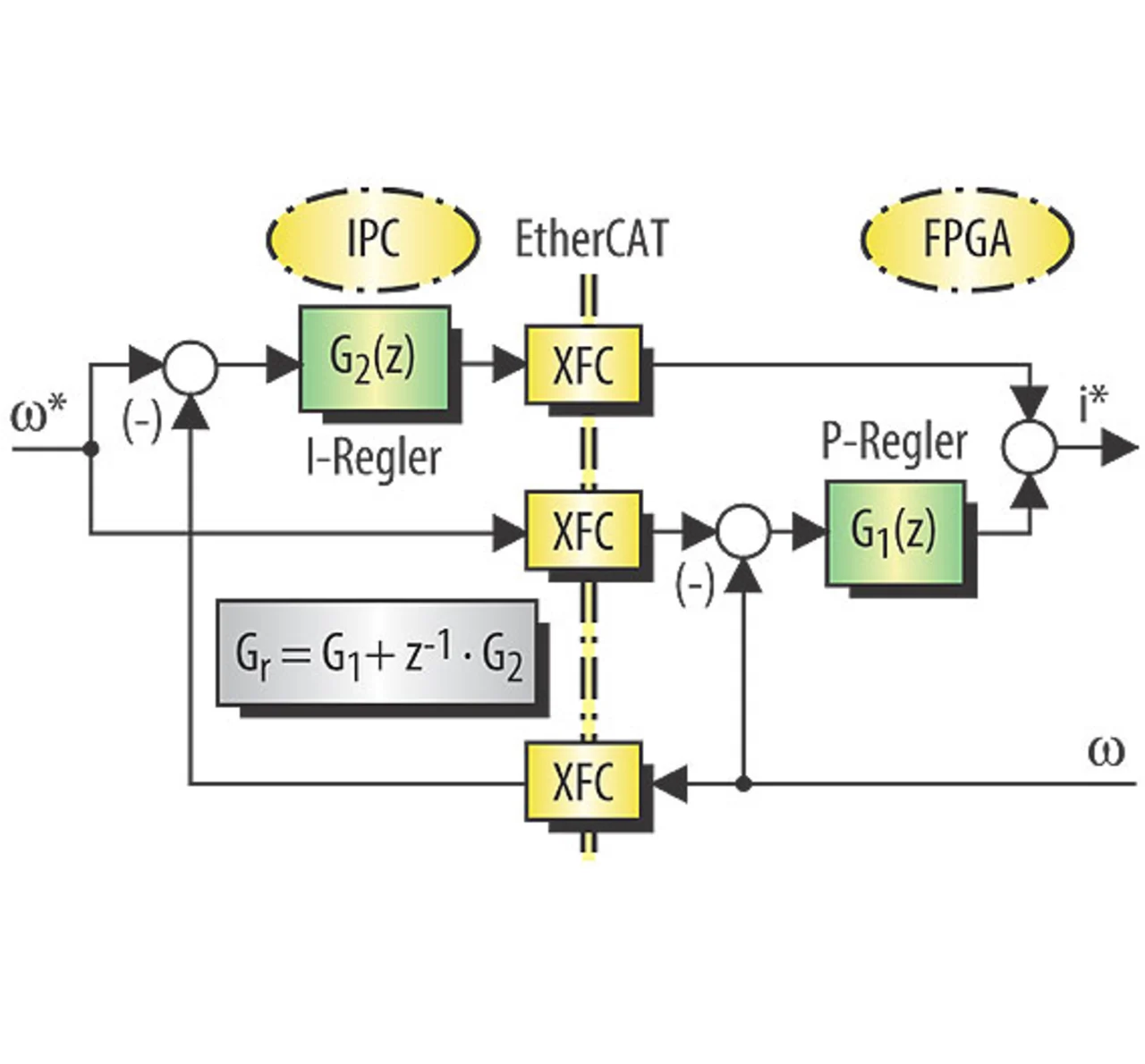

In einer neuartigen hybriden Drehzahlregler-Struktur werden die Algorithmen des Abtastreglers in zwei additive Komponenten aufgeteilt (Bild 3). Eine erste Komponente, die ausschließlich in programmierbarer Logik (FPGA) berechnet wird, und eine zweite Komponente, die mit einer freiprogrammierbaren CPU (Matlab - C) gerechnet wird - im FPGA oder zentral über den Feldbus.

Die erste Komponente kann mit einer nicht besonders aufwendigen, fest codierten Struktur berechnet werden. Diese Struktur ist Bestandteil der FPGA-Konfiguration und wird applikationsabhängig parametriert. Diese erste Komponente wird ohne nennenswerte Verzögerung mit programmierbarer Logik berechnet und zu der um einen (Feldbus-)Zyklus verzögerten (z - 1 = Zykluszeit) zweiten Komponente addiert.

Die zweite Komponente ist dadurch gekennzeichnet, dass der erste Koeffizient der Impulsantwort immer identisch Null ist. Deshalb bleibt der Algorithmus auch dann kausal, wenn die gewünschte Impulsantwortfolge zur Kompensation der Verarbeitungszeit um eine Abtastzeit nach links geschoben wird. Dieser Algorithmus kann entweder über einen sehr schnellen Feldbus wie EtherCAT auf einem IPC mit FPU ausgeführt werden, oder er wird z.B. auf der Soft-Core-CPU Nios II mit FPU-Erweiterung gerechnet. Wesentlich ist, dass die Zeit zur Berechnung inkl. eventueller Feldbus-Übertragungszeiten kleiner als die Drehzahlregler-Zykluszeit ist.

Diese neuartige Struktur verbindet die Vorteile einer vollständigen Realisierung in Hardware (VHDL) (deutlich schneller als 1 μs) mit den Vorteilen einer prozessorbasierten Implementierung (flexibel und offen, effiziente Ausnutzung der Ressourcen und gute Unterstützung bezüglich des Design-Flows).

Besonders vorteilhaft ist, dass diese Komponenten in der hybriden Struktur auch gleichzeitig additiv genutzt werden können. In einem sehr einfachen Beispiel wäre die erste Komponente ein P-Regler und die zweite Komponente ein I-Regler. Zusammen ergibt sich ein PI-Regler. Dass die I-Komponente um einen Taktzyklus verschoben ist (z - 1), spielt keine nennenswerte Rolle und könnte in diesem einfachen Beispiel auch bei der Berechnung der Koeffizienten mathematisch exakt berücksichtigt werden.

Der für die Stabilität (Phasenreserve) wichtige P-Anteil wird ohne Zeitverzug berechnet, der I-Anteil inklusive Anti-Wind-Up, Reset usw. zentral in der Steuerung. Wenn eine motorintegrierte Antriebstechnik mit einem schnellen Stromregler und einer schnellen Feldbusanschaltung versehen ist, kann mit Hilfe der verteilten Regelungstechnik aus diesem Antrieb ein „vollwertiger Servoantrieb“ mit optionaler Sicherheitstechnik werden.

Ergebnisse

Ein erstes Beispiel ist die sensorlose Regelung von Antrieben. Je nach Motor und Anwendung gibt es diverse Verfahren (Algorithmen), die nicht exakt identisch sind, sondern verschiedene Stärken und Schwächen aufweisen. Der Maschinenbauer kann diese heute nur durch die Wahl des Antriebsherstellers auswählen, da es heute noch kein Standard ist, dass IP im Antrieb eingesetzt werden kann. Auf der Hannover Messe 2010 [2] wurde eine vollständig in Matlab codierte und auf einem IPC unter TwinCAT 3 ausgeführte sensorlose Regelung eines permanenterregten Linearmotors vorgestellt.

Durch die massiv parallelen Signalverarbeitungspfade in FPGAs sind komplexe, digitale Regelalgorithmen besonders schnell ausführbar. Auch bei hohen Schaltfrequenzen - größer 20 kHz - kann jede Schaltflanke berechnet werden. Die erreichbare Bandbreite der Stromregelung hängt dadurch nur noch von der Schaltfrequenz der Leistungshalbleiter und von der effektiven Verzögerungszeit der Stromsensoren ab.

Des weiteren wurden am Beispiel eines 5-kW-Direktantriebs einer Werkzeugmaschine Messergebnisse vorgestellt [3], die zeigen, welche außerordentlich hohe dynamische Steifigkeit Direktantriebe mit einem FPGA-basierten Servoumrichter erreichen können. Bei Beschleunigungen von bis zu 40 m/s² und Frequenzen bis 130 Hz beträgt der Schleppfehler des eisenlosen Linearmotors weniger als 1 μm.

Die Laboraufbauten basieren auf dem FPGA Development Board „Mercury Code“ [4], das eingesetzte FPGA ist aus der Cyclone-Familie von Altera. Von den zur Verfügung stehenden 40 000 Logikelementen werden knapp 30 000 genutzt.

Literatur

[1] Klarenbach, C.; Krah, J.O.: Fast and High Precision Motor Control for High Per-

formance Servo Drives. PCIM-Konferenz, Nürnberg, Mai 2010.

[2] Klarenbach, C.; Holzapfel, J.; Krah, J.O.: Sensorlose Regelung eines Servomotors mit Matlab Simulink und TwinCAT 3.0. EtherCAT Technology Group, Hannover Messe, April 2010.

[3] Klarenbach, C.; Krah, J.O.: Fast and High Precision Motor Control for High Per-

formance Servo Drives. PCIM-Konferenz, Nürnberg, Mai 2010.

[4] Krah, J.O.; Richter, R.: FPGAs eröffnen neue Möglichkeiten für Motion Control - Teil 1. Elektronik 2008, H. 24, S. 42ff.

[5] Krah, J.O.; Klarenbach, Ch.: Die Mischung macht`s - Strommessung mit Sigma-Delta-Modulatoren erlaubt hochdynamisches Motion Control. Elekronik scout 2011, S. 32ff.

Die Autoren:

| Prof. Dr. Jens Onno Krah |

|---|

| wurde 2004 zum Professor für „Allgemeine Regelungstechnik“ in der Fakultät für Informations-, Medien- und Elektrotechnik der Fachhochschule Köln berufen. Nach seinem Studium der Elektrotechnik an der Universität Wuppertal promovierte er dort 1993 im Bereich Antriebsregelung. Bis 2004 arbeitete er bei Kollmorgen (Danaher) und war unter anderem für die weltweite Entwicklung der Kollmorgen Servoregler verantwortlich. Sein Interesse gilt der digitalen Signalverarbeitung mit FPGAs und Motion Control. |

Jens_Onno.Krah@FH-Koeln.de

| M.Sc. Christoph Klarenbach |

|---|

| studierte von 2001 bis 2006 an der Universität Wuppertal Elektrotechnik und erlangte seinen Master of Science im Jahr 2006. Seine Schwerpunkte liegen in den Gebieten Regelungs- und Antriebstechnik sowie Leistungselektronik. Momentan arbeitet er an seiner Promotion im Bereich Antriebsregelung mit FPGAs. |

Christoph.Klarenbach@FH-Koeln.de

- FPGAs in der Automatisierung

- Baugruppen eines Servoantriebs