Mit Single-Chip-Lösung Profinet in Feldgeräte und Antriebe integrieren

Der Tiger im Automatisierungsnetzwerk

Fortsetzung des Artikels von Teil 1

Zwei Chips in einem

Der Tiger-Chip besteht aus zwei einzelnen Chips, die durch eine SIP-Lösung (System-in-Package) zu einem ASIC zusammengeführt wurden. Beim TPS-1 ist der 100-Mbit-Dual-PHY in 150-nm-Technologie abgebildet. Beim ARM-Subsystem inkl. der Profinet-Hardware-Unterstützung hingegen kommt auf Grund der Verlustleistung, des integrierten Speichers und der Kosten eine Strukturgröße von 90 nm zum Einsatz.

Die Konsistenz der E/A-Daten wird durch eine autarke Multibuffer-Konsistenzeinheit gewährleistet. Bei dieser Einheit wird der Buffer mit den aktuellen E/A-Daten nach dem Transfer durch ein explizites Kommando per Schreibzugriff freigeben. Die Protokollvorverarbeitung der Profinet-Consumer-Maschinen in Hardware wertet dabei den APDU-Status aus; außerdem wird ein Konsistenz-Check auf Frame-Länge und Source-MAC-Adresse durchgeführt; der Applikation werden so nur gültige E/A-Daten bereitgestellt.

Bei den Zugriffzeiten zwischen den einzelnen Modulen wird der Jitter durch eine Multilayer-AHB-Busarchitektur nahezu auf Null reduziert (siehe Bild 2). Hierbei sind auf jedem Bus Parallelzugriffe möglich, sodass der RT/IRT-Kommunikationskanal nicht durch Zugriffe anderer Komponenten wie der ARM966-CPU gestört wird. Die Abarbeitung des NRT-Netzwerkverkehrs und der azyklischen Events hat somit keinen Einfluss auf die Echtzeit-Kommunikation.

Die ARM966-CPU ist mit zwei „tightly capped“-Speichern von jeweils 384 KByte ausgestattet, die direkt an die CPU angebunden sind. Der Speicher ist in Daten- und Befehlsspeicher unterteilt. Jeder Zugriff des ARM966 auf den Speicher erfolgt bei dieser Architektur ohne Verzögerung und führt im Vergleich zu Varianten mit externen Speichermodulen zu einem massiven Leistungsschub. Um den Speicher auch für kommende Firmware-Generationen flexibel nutzen zu können, lassen sich einige der Sub-Speicherblöcke alternativ dem Daten- oder Befehlsbereich zuweisen. Dies erfolgt während der First-Level-Bootsequenz und ist dann für den laufenden Betrieb nicht mehr veränderbar.

Die Firmware und die Konfiguration, z.B. Speicheraufteilung, werden über einen SPI-Master in den Befehlsspeicher des ARM966 geladen. Zur Gewährleistung der Datenkonsistenz der Firmware und zum Ausschluss von Übertragungsfehlern sind alle Bereiche des Flash-Speichers mit einer Check-summe gesichert. Zur Überprüfung der Checksumme wird im Baustein eine eigenständige Hardware-Einheit genutzt. Die Anforderungen des „Fast StartUp“-Szenarios mit 500 ms bis zur RT-Verbindung werden dabei trotz Verwendung eines seriellen Flash-Bausteins erfüllt. Zur Verarbeitung der NRT-Frames verfügt der Chip über eine eigene Verarbeitungseinheit mit Ressourcenverwaltung und speziellen Filtern. Diese schützt den ARM966 per Hardware vor Überlastungssituationen durch NRT-Netzwerkverkehr. Zur schnellen und zuverlässigen Übertragung von Echtzeit-Daten an die Ein- bzw. Ausgänge wurde ein Timer mit einer Auflösung von 10 ns integriert. Der Timer löst die Kopierprozesse zwischen Konsistenzsteuerung und den GPIOs aus. In der Betriebsart IRT wird dieser Timer kontinuierlich auf die IRT-Zeitsynchronisation abgestimmt.

Die komplette RT/IRT-Kommunikation bis hin zu den E/As findet also ohne Beteiligung der internen CPU statt. Dies hat den Vorteil, dass neben der konstanten Transferzeit auch sehr geringe T-Input-/T-Output-Zeiten erreicht werden. Dadurch können die Zeiten zum Einlesen oder Ausgeben der Daten sehr nah an den Applikationszyklus gelegt werden. Im Anwendungsfall mit externer Host-CPU dienen diese Signale zur Synchronisierung der Host-Applikation auf den Profinet-Kommunikationszyklus.

Für die Profinet-Zeitsynchronisation ist ein erweiterter Hardware-Support mit Unterstützung des One-Step-Verfahrens im ASIC implementiert. Die nötigen Zeitstempel werden mit einer Stempeleinheit erfasst, welche mit einer Abtastrate von 400 MHz arbeitet und dadurch auch bei Linientopologien mit vielen Teilnehmern je Linie für einen geringen Jitter der IRT-Uhren sorgt. Der Line Delay Responder für Kabellängenmessungen wurde in Hardware abgebildet und ermöglicht eine sehr kurze Antwortzeit von ca. 10 µs. Dadurch ist eine genaue Synchronisation auch bei Linientiefen von 100 Geräten im IRT-Betrieb möglich.

Zur Überwachung der internen CPU und der externen Host-CPU sind im Tiger-Chip zwei Watchdog-Timer integriert. Eine externe CPU kann dem Chip ihr „Alive“-Signal einfach per GPIO mitteilen. Wird der Watchdog nicht rechtzeitig zurückgesetzt, so wird dies der externen Host-CPU durch einen Flankenwechsel am Watchdog-Ausgang angezeigt.

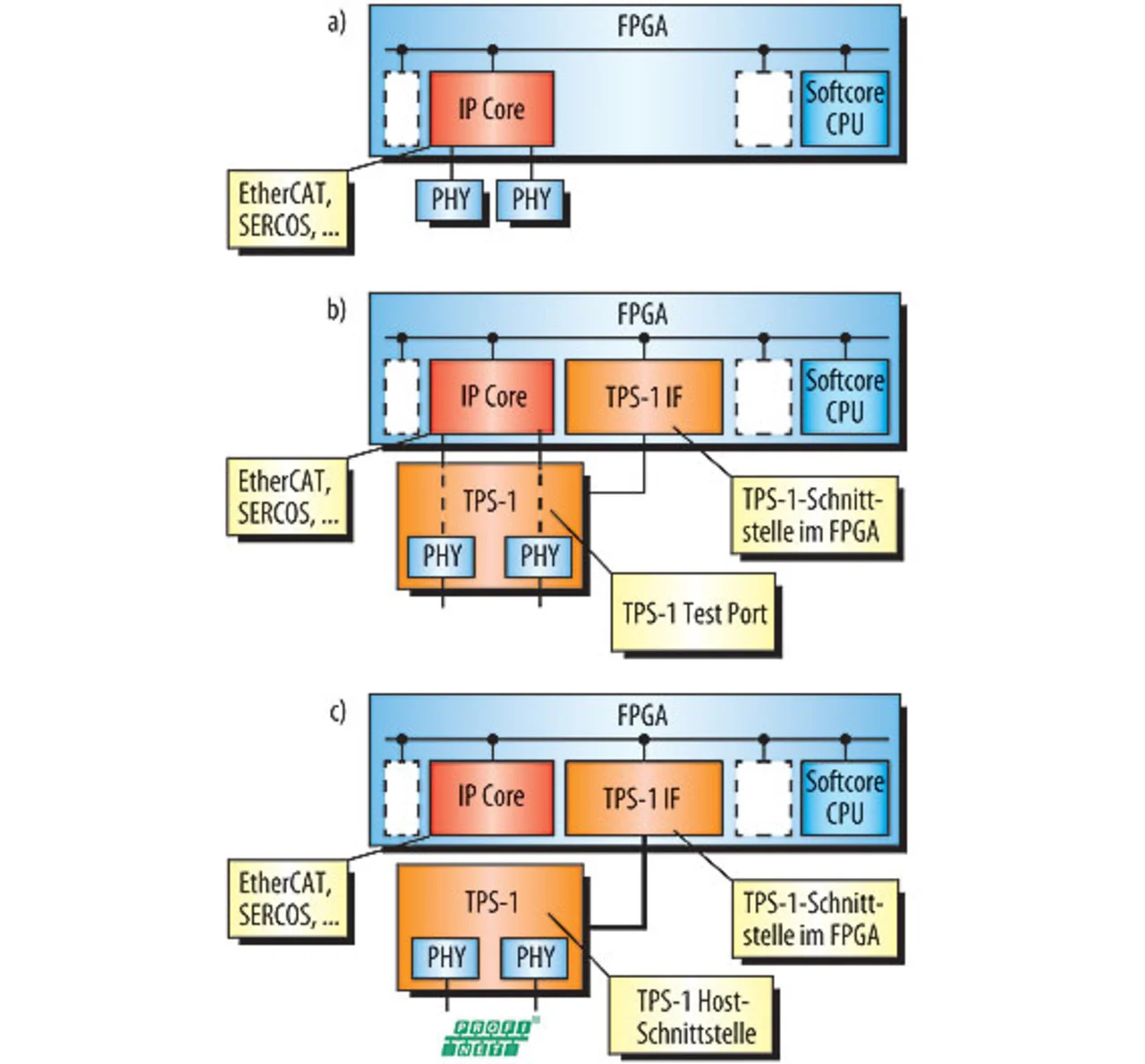

Der Baustein kann auch in Verbindung mit flexiblen FPGA-basierenden Schnittstellenlösungen verwendet werden. Dabei können über eine entsprechende Betriebsart ausschließlich die integrierten PHYs des Bausteins genutzt werden. In dieser Betriebsart wirkt dieser wie ein Dual-PHY und kann von allen auf IP-Core basierenden Ethernet-Systemen aus dem FPGA heraus verwendet werden (Bild 5). Der Clou: Durch einfache Umschaltung in die „normale“ Betriebsart kann eine im FPGA integrierte Softcore-CPU die komplette Profinet-Funktionalität des TPS-1 über dessen Host-Interface nutzen. Die Mehrkosten gegenüber dem ohnehin benötigten Dual-PHY sind im Vergleich zur dadurch nutzbaren Profinet-Funktionalität sehr gering.

Lichtwellenleiter als Übertragungsmedium werden vom TPS-1 unterstützt. Der Chip bietet für jeden der beiden externen Ethernet-Ports eine separate I²C-Schnittstelle, an die jeweils ein Fiber Optic Transceiver von Avago angeschlossen werden kann. Aufgrund der Trennung der beiden Schnittstellen muss keine spezielle Adressierung erfolgen. Spezielle Applikationsprofile wie PROFIsafe oder PROFIenergy sind in höheren Protokollschichten angesiedelt und werden daher „oberhalb“ des TPS-1 implementiert.

Zur einfachen Konfiguration der verschiedenen Betriebsarten bietet KW-Software entsprechende Firmware- und Software-Komponenten an. Die Firmware enthält den eigentlichen Profinet-Stack sowie weitere Funktionen zur internen Steuerung des Chips und zum Update der Firmware über unterschiedliche Schnittstellen. Als Konfigurationswerkzeug unter Windows wird der TPS-Configurator eingesetzt. Neben der Betriebsart des Chips werden hier auch Details wie MAC-Adressen, Informationen des I&M-Profils und weitere Daten konfiguriert.

Gemeinsam entwickelt

Mit dem TPS-1 haben Phoenix Contact und Siemens eine Single-Chip-Lösung entwickelt, mit der sich Geräte und Antriebe schnell und einfach an Profinet ankoppeln lassen. Phoenix Contact hat sein Know-how aus der Entwicklung des Interbus-Systems in den Tiger-Chip eingebracht und zusätzlich neue Ideen zur Leistungssteigerung von Profinet beigesteuert. Der neue Baustein reduziert den Integrationsaufwand und unterstützt die aktuelle Profinet-Spezifikation bis Conformance Class C.

Die Autoren

| Peter Fuchs |

|---|

| studierte Elektrotechnik mit dem Schwerpunkt Informationsverarbeitung an der FH Bielefeld. Seit 1989 arbeitete er mehrere Jahre bei Phoenix Contact in der Entwicklung von Interbus-Systemkomponenten und übernahm anschließend die Leitung des Interbus Support Centers und des Fieldbus Competence Centers. Seit 2007 ist er Leiter des Geschäftsfelds Profinet bei der KW-Software GmbH in Lemgo. |

| Carsten Pieper |

|---|

| studierte Ingenieurinformatik mit Schwerpunkt Elektrotechnik an der Universität Paderborn. Bis 2009 war er am Institut Industrial IT beschäftig und ging dann zum Fraunhofer Kompetenzzentrum Industrial Automation (INA). Heute beschäftigt er sich mit der Entwicklung von IP-Cores und ASICs für die Kommunikation in der Automatisierungstechnik. |

- Der Tiger im Automatisierungsnetzwerk

- Zwei Chips in einem