Microsemi

SmartFusion 2 SoC FPGA - ohne Analogtechnik

Fortsetzung des Artikels von Teil 1

Kurzinfo zu SmartFusion2

Die SmartFusion2 Familie umfasst sechs Bausteine, die eine Komplexität von 5K LUT bis 120K LUTs abdecken. Kunden können mit dem SmartFusion2 Engineering Sample M2S050T sofort mit der Entwicklung beginnen. Microsemi gibt an, dass Silizium aus der Serienfertigung bereits im Frühjahr 2013 verfügbar sein soll.

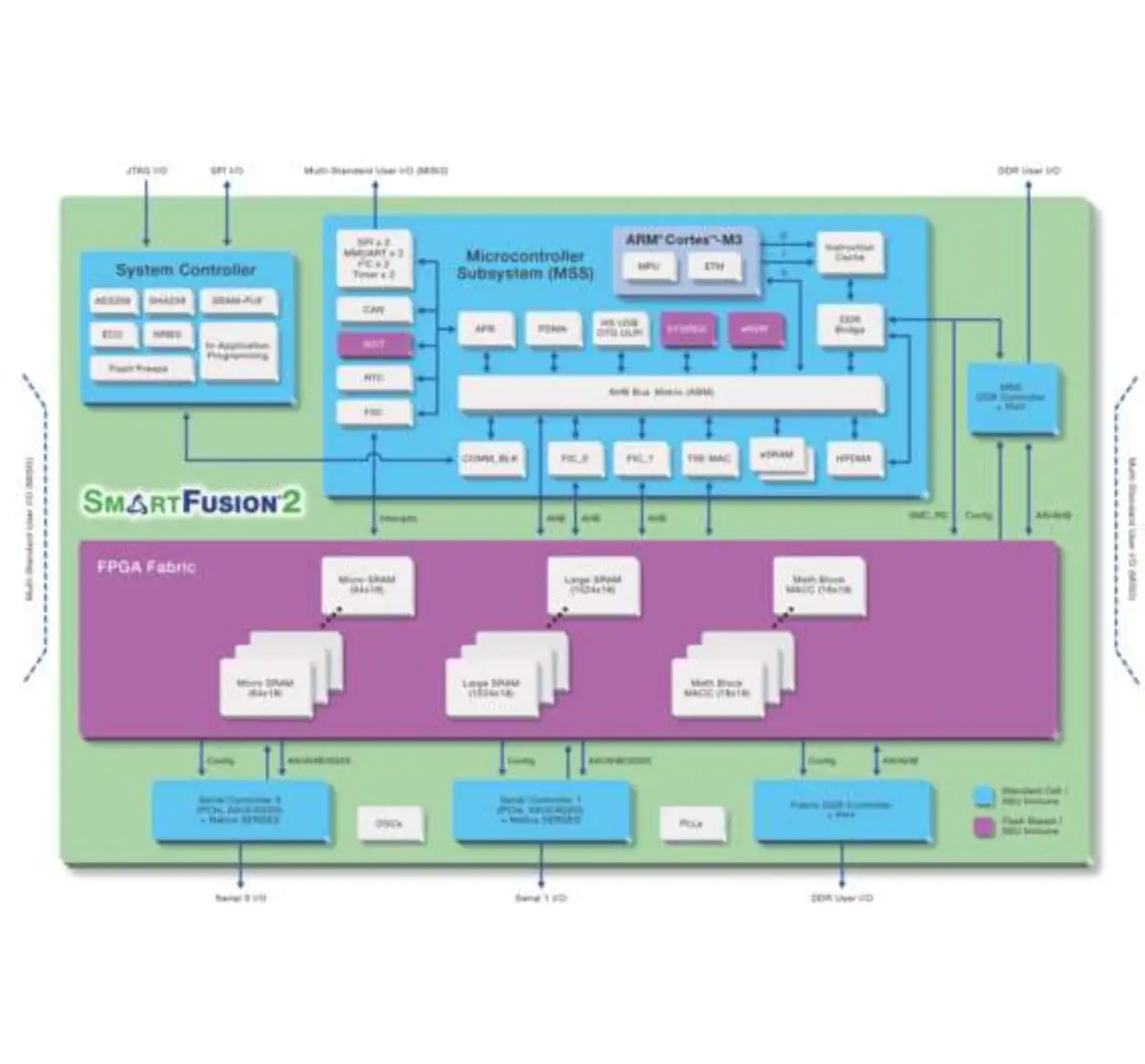

Die Bausteine sind mit Embedded Memory und Multiple Accumulate Blöcke für die digitale Signalverarbeitung ausgestattet. Darüber hinaus verfügen sie über Interfaces mit hoher Bandbreite wie PCI Express (PCIe) mit flexiblem 5G SERDES neben schnellen DDR2/DDR3 (Double Data Rate) Memory Controllern. Darüber hinaus hat Microsemi in die FPGAs ein Mikroprozessor-Subsystem (MSS) mit einem Cortex-M3-Prozessorkern (166 MHz), 64 KByte eSRAM und 512 KByte eNVM integriert. Das MSS ist mit ETM (Embedded Trace Macrocell) ausgestattet und enthält ferner 8 KByte Befehls-Cache sowie Peripherie inklusive CAN (Controller Area Network), Gigabit Ethernet und High Speed USB 2.0.

Jobangebote+ passend zum Thema

- SmartFusion 2 SoC FPGA - ohne Analogtechnik

- Kurzinfo zu SmartFusion2