Die Anforderungen des 10-Gbit/s-Ethernet bringen den Umschwung

Neue Rechnerstrukturen für die Kommunikation

Fortsetzung des Artikels von Teil 3

Neue Rechnerstrukturen für die Kommunikation

Für die Programmierung des Prozessors ist ein Software Development Kit verfügbar, der zwei Anwender-Programmier-Schnittstellen (API) zur Verfügung stellt:

- Das „Database API“ bietet einen Mechanismus, nach dem der Anwender eine Datenstruktur in einer PCRE-Standard-Syntax (Perl Compatible Regular Expression) aufstellen und managen kann.

- Das „Dataplane API“ stellt eine Schnittstelle zur Verfügung, über die alle Aspekte des NetL7-Prozessors während der Laufzeit steuerbar sind. Neben der Überwachung und Beeinflussung der Mustererkennung lassen sich zusätzlich neue Datenstrukturen „online“ laden oder auslagern.

Zu dem Chip ist der Hardware Development Kit NLEVC-1 erhältlich, der den NetL7 auf einer PCI-Platine sofort systemfähig macht. Der Kit umfasst neben der PCI-Platine noch die Treiber-Software und API, Software-Code mit Anwendungsbeispielen, Schaltbilder und ein Benutzerhandbuch. Als Anwendungen für den Chip nennt der Hersteller Layer-7-Router und -Switches, Lastverteilung in Data Centers, Protokoll-Analysatoren, Systeme für das Digital Rights Managements sowie Intrusion Prevention Systems.

Jobangebote+ passend zum Thema

| Eugene Lessard ist seit 1999 Test-Entwicklungsingenieur bei ON Semiconductor. Vorher war er Produkt-Ingenieur für Cherry Semiconductor, heute ON Semiconductor. Er studierte an der Universität von Rhode Island, RI (USA), und erhielt 1993 einen BSEE an der Roger Williams University, Bristol, RI. E-Mail: Gene.Lessard@onsemi.com |

Referenz-Design in FPGA

Mit den 40-nm-FPGAs kommt für den Entwurf von Bausteinen für das 10-Gbit/s-Ethernet eine weitere Technologie ins Spiel, deren größter Vorteil in der Rekonfigurierbarkeit liegt. Dies ist besonders interessant, wenn es darum geht, innerhalb eines Anwendungsfeldes – etwa der Kommunikation – Bausteine zu entwickeln, die sich für Nischenmärkte eignen. Die Anwendungen für das 10-Gbit/s-Ethernet reichen von der Verbindung im System („Backplane“) über die Kopplung von Rechnern an Speichersysteme und so genannte Metro-Ethernet-Verbindungen bis hin zu dedizierten „Long Haul“-Verbindungen. Dies wird noch potenziert durch die unterschiedlichen Funktionen und Prozesse, die an dem jeweiligen Einsatzort auf den Ethernet-Datenstrom angewendet werden müssen: „Quality of Service“-Prozeduren, Intrusion Detection, Layer-4/7-Switching etc. Insgesamt führt dies zu einer hohen „Granularität“ der Anwendungen, dadurch reichen die Stückzahlen oft nicht aus, hier in die Entwicklung von ASSPs (Application Specific Standard Products) einzusteigen.

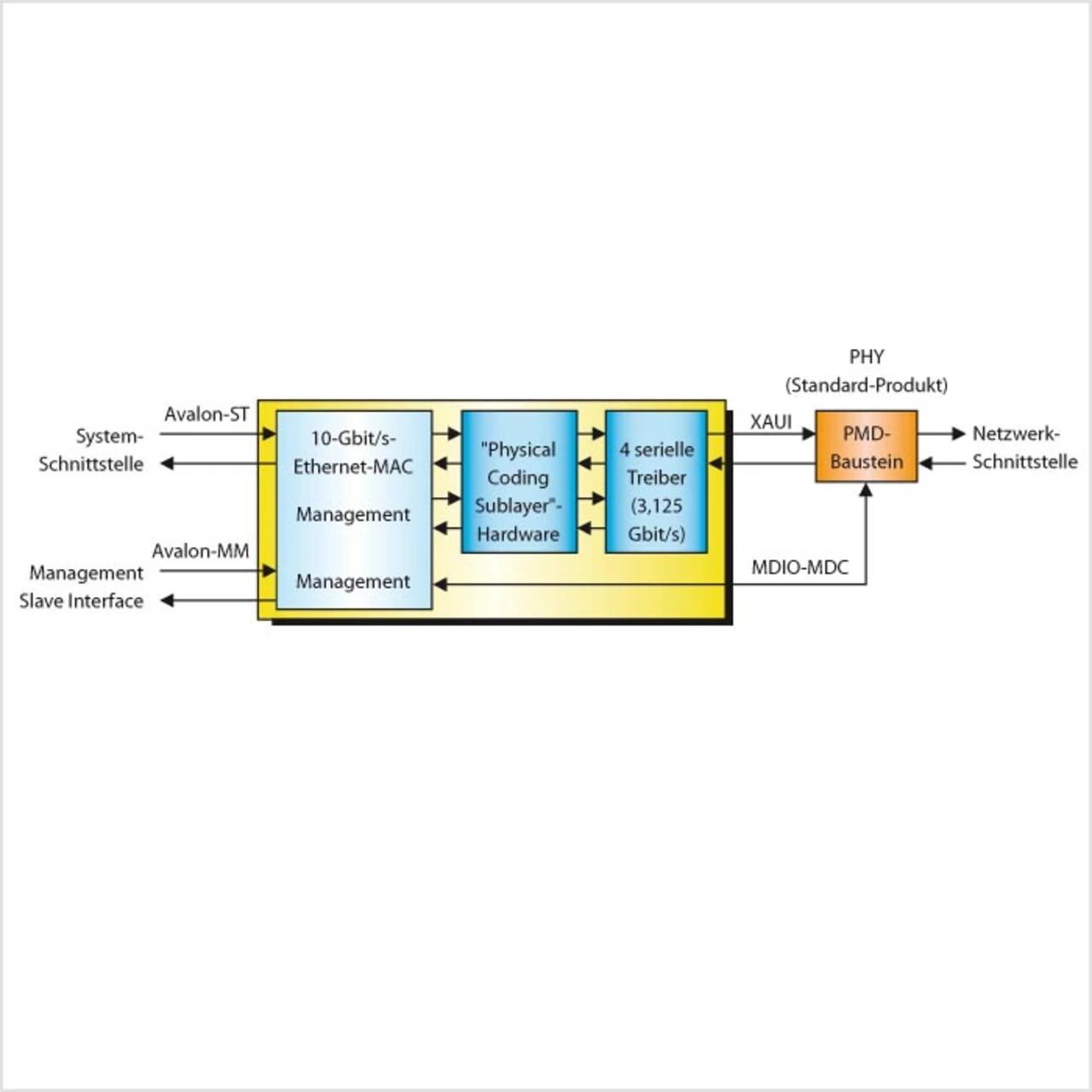

Auf dem FPGA-Chip neuester Technologie lassen sich nun serielle Treiberbausteine realisieren, die eine Datenübertragungsrate von 8 Gbit/s erreichen. Dies genügt, um ein standardgerechtes XAUI-Interface mit vier seriellen SerDes-Treibern mit jeweils 3,125 Gbit/s auf einem FPGA aufzubauen. Folgerichtig bietet Altera [3] ein vollständiges 10-Gbit/s-Ethernet-Referenz-Design als IP für die Realisierung als FPGA (Bild 3). Die entscheidende Baugruppe des Designs ist der Media Access Controller (Ethernet MAC), zu dem je nach Anwendung der Physical Coding Sublayer (PCS) und das Physical Media Attachment (PMA) in Hardware oder als Software realisiert werden können. Dabei kann der externe Treiber zum Netzwerk (PHY) über die XAUI-Schnittstelle (4 × 3,125 Gbit/s) oder als XGMII (Ten Gigabit Media Independent Interface) als 32 bit breiter Bus mit einer Transferrate von 312,5 Mbit/s bedient werden.

Der „10 Gigabit Ethernet MAC Core“ ist konform zu den im Standard IEEE 802.3ae niedergelegten Spezifikationen und kann damit für Anwendungen im WAN, LAN und in Metropolitan-Netzwerken (MAN) genutzt werden. Eine zweite Version lässt sich als Network Interface Card (NIC) ausführen oder in „Ethernet Switching“-Anwendungen betreiben.

Acht Prozessoren simultan

Die RMI Corporation [4] bringt unter der Bezeichnung „XLP832“ die dritte Generation ihre XLP-Serie von Kommunikations-Prozessoren auf den Markt, die in 40-nm-CMOS-Technologie ausgeführt sind und mit Taktfrequenzen bis zu 2 GHz betrieben werden können. Im Vergleich zu den Vorgängergenerationen XLR und XLS soll der XLP bei vergleichbarer Rechenleistung nur ein Drittel der Leistungsverluste produzieren. Dabei bleibt der neue Chip software-kompatibel zu den XLR- und XLS-Systemen, die unter Linux laufen. Monta Vista hat bereits angekündigt, dass die Monta-Vista-Linux-Plattform, die das Carrier Grade Linux (CGL) in der Version 4.0 unterstützt, auf die XLP-Systeme angepasst wird.

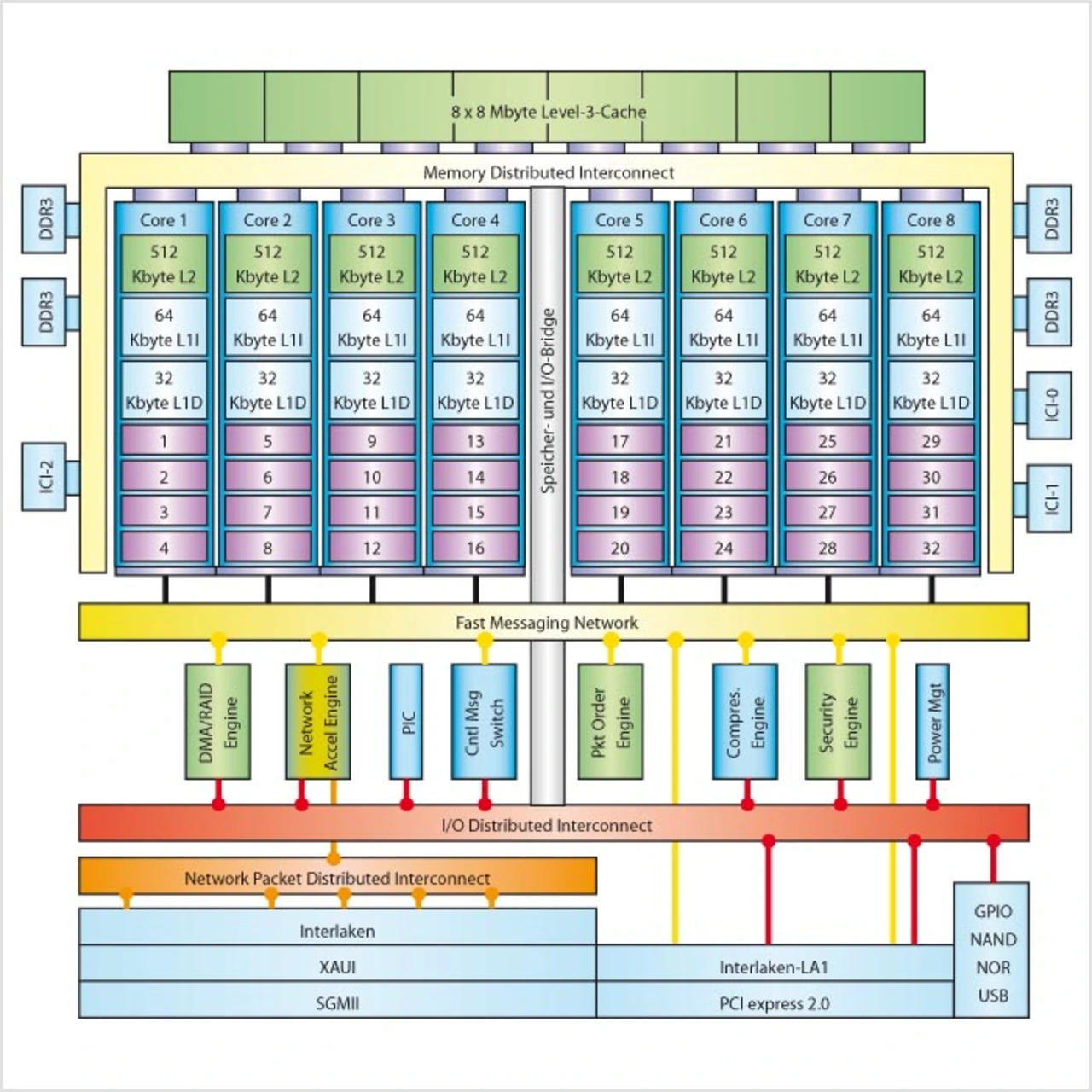

Die als EC4400 bezeichneten Cores sind in superskalarer Architektur aufgebaut (Bild 4). In der aus acht Cores bestehenden Struktur besteht die Möglichkeit, Befehle „out of order“, also außerhalb der durch die Befehls-Pipeline vorgegebenen Reihenfolge abzuarbeiten. Damit kann die auf dem System laufende Software vergleichsweise einfach gehalten werden.

Die aus acht Prozessoren bestehende Struktur kann 32 Threads quasisimultan abarbeiten; jeder der acht 32-bit-Prozessoren ist ausgestattet mit 64 Kbyte L1-Befehls-Cache, 32 Kbyte L1-Daten-Cache und 512 Kbyte L2-Cache, letzterer arbeitet mit achtfacher Satzassoziativität. Über einen speziellen Speicher-Bus, hier „Memory Distributed Interconnect“ genannt, können die Prozessoren auf acht auf dem Chip integrierte „Banked Memory“-Speicher mit einer Kapazität von jeweils 8 Mbyte zugreifen, die als Level-3-Cache mit 16-facher Satzassoziativität organisiert sind. Für die Synchronisation der Prozessoren wurden so genannte „Interchip Coherency Interfaces“ (ICI-0 bis ICI-2) integriert, auf die ebenfalls über den „Memory Distributed Interconnect“zugegriffen wird. Über diesen Bus besteht auch der Zugriff auf vier auf dem Chip integrierte DDR3-Speicher-Controller, die mit externen DDR3-RAMs bei einer Speicherbusbreite von 72 bit einen Durchsatz von 51,2 Gbit/s erreichen.

- Neue Rechnerstrukturen für die Kommunikation

- Am Anfang steht der PHY

- Autor

- Neue Rechnerstrukturen für die Kommunikation

- Neue Rechnerstrukturen für die Kommunikation