Rechnerbussysteme

Wie Software die PCI-Leistung von Intel-Chipsätzen beeinflusst

Fortsetzung des Artikels von Teil 1

Datenübertragung zum PCI-Target mittels programmierter Ein-/Ausgabe

Was geschieht, wenn Daten vom Hauptspeicher mittels programmierter Ein-/Ausgabe zu einem PCI-Target übertragen werden sollen?

Jobangebote+ passend zum Thema

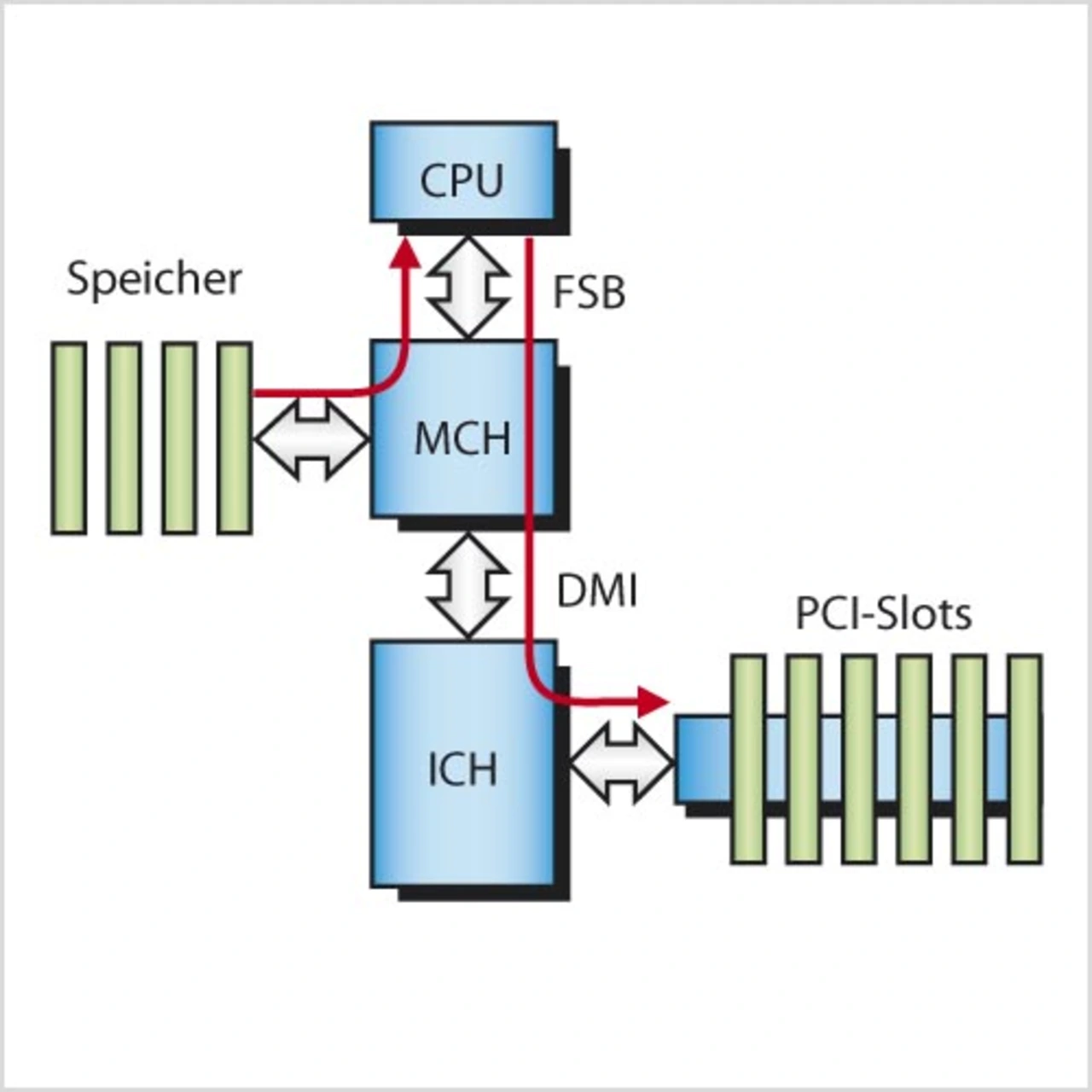

Zunächst muss die CPU 4 byte aus dem Hauptspeicher lesen. Um die Lesezugriffe auf den Speicher zu beschleunigen, wird via Memory-Controller-Hub (MCH) und FSB eine gesamte Cache-Line von 64 byte, die die angeforderten 4 byte beinhaltet, vom Hauptspeicher in den CPU-Cache geladen. Wieder über den FSB werden die 4 byte nun an eine I/O-Adresse des PCI-Targets geschrieben, wobei sie zunächst in einen Puffer innerhalb des MCH übertragen werden.

Sobald der MCH Zugriff auf das Direct Media Interface hat, werden sie dann zum I/O-Controller-Hub (ICH) übertragen. Im ICH werden die 4 byte wieder in einem Puffer gespeichert und zum PCI-Target gesendet, sobald der ICH Zugriff auf den PCI-Bus erhält (Bild 3).

Ein einzelner PCI-Transfer benötigt mindestens einen PCI-Bus-Zyklus, um Zugriff auf den Bus zu erlangen, einen PCI-Bus-Zyklus, um die Adresse zu übertragen, und einen PCI-Bus-Zyklus, um die Daten zu übertragen. Dadurch verringert sich die Datenrate auf weniger als 33 % (<40 Mbyte/s) der theoretischen Bandbreite. Doch nicht einmal diese Übertragungsraten lassen sich erzielen, da normalerweise Leerlaufund Wartezyklen für langsamere Targets hinzukommen.

Wenn der PCI-Transfer beendet ist, liest die CPU die nächsten 4 byte, diesmal jedoch aus dem CPU-Cache. Auch wenn dieser Schritt schneller abläuft, werden die folgenden Schritte (CPU → FSB → MCH → DMI → ICH) auf die gleiche Weise wie zuvor durchgeführt. Leider ist der ICH nicht in der Lage, mehrere PCI-Bus-Transfers zu einem einzelnen PCI-Block-Transfer zusammenzufassen. So überträgt der ICH nur die Daten in einem PCI-Block-Transfer, die er in einem einzelnen Paket über das Direct Media Interface erhalten hat.

Da der PCI-Bus viel langsamer ist als der Front Side Bus (FSB) und auch das Direct Media Interface, und da die CPU an anderen Aufgaben arbeitet, während sie auf das Ende des PCI-Transfers wartet, werden in der Zwischenzeit viele verschiedene Transfer-Operationen über FSB, MCH, Speicherschnittstelle und Direct Media Interface durchgeführt.

Während einer einzigen PCI-Übertragung von 4 byte, die z.B. drei PCI-Buszyklen lang dauert, arbeitet eine heutige 2-GHz-CPU nahezu 180 Befehle ab. Über einen 800 MHz schnellen FSB lassen sich in dieser Zeit bis zu 580 byte übertragen, über eine Dual-Channel-Speicherschnittstelle mit 667 MHz sind es 970 byte, und über ein Direct Media Interface immerhin noch 180 byte (siehe Tabelle).

| Bus | max. theor. Übertragungsrate |

|---|---|

| PCI-Bus (33 MHz) | 132 Mbyte/s |

| Front Side Bus (800 MHz) | 6400 Mbyte/s |

| Dual-Channel-Speicher-Schnittstelle | 10700 Mbyte/s |

| Direct Media Interface | 2000 Mbyte/s |

Vergleich der Übertragungsraten von PC-internen Bussystemen

Der Front Side Bus und das Direct Media Interface sind für einen hohen Datendurchsatz ausgelegt und werden daher nicht durch eine einzelne Übertragung blockiert. Stattdessen überlappen sich viele Übertragungen und verwenden den Bus im Multiplexverfah ren.

Wollte man Datentransfers über diese Schnittstellen zusammenlegen, so bräuchte man riesige Puffer, was sich wiederum in langen Latenzzeiten und in einem verringerten Durchsatz niederschlagen würde. Da weder der MCH noch der ICH Einzeltransfers zusammenfassen, wird für jede 4 byte große Übertragung eine einzelne PCI-Transaktion generiert.

Ein Zyklus zusätzlich beim Lesen

Wenn Daten per programmierter Ein-/ Ausgabe von einem PCI-Target gelesen werden, fordert die CPU 4 byte vom MCH an, der MCH leitet die Anforderung über das Direct Media Interface zum ICH weiter, der dann einen Lese-Transfer auf dem PCI-Bus initiiert. Selbst wenn das PCI-Target in der Lage ist, mehr als 4 byte über einen einzelnen PCI-Block-Transfer zu senden, bricht der ICH den Transfer nach dem ersten Zyklus ab, da nur 4 byte angefordert wurden. Dann werden die 4 byte vom ICH über das Direct Media Interface zum MCH und über den FSB zur CPU gesendet. Nachdem sie im Hauptspeicher abgelegt wurden, indem die CPU diese erneut über den FSB zum MCH übermittelt, können die nächsten 4 byte angefordert werden. Die Daten nehmen den gleichen Weg wie in Bild 3, nur entgegen der Pfeilrichtung.

Ein PCI-Lese-Zugriff benötigt – verglichen mit einem PCI-Schreib-Zugriff – einen PCI-Zyklus mehr, da der PCI-Bus vom Bus-Master für die Datenübertragung an das Target übergeben werden muss. Die erzielbare Datenrate beträgt deshalb weniger als 25 % (<33 Mbyte/s) der theoretischen PCI-Übertragungsrate.

- Wie Software die PCI-Leistung von Intel-Chipsätzen beeinflusst

- Datenübertragung zum PCI-Target mittels programmierter Ein-/Ausgabe

- Leistung erhöhen durch Änderung der Cache-Strategie

- Datenübertragung per Direct Memory Access (DMA)