Rechnerbussysteme

Wie Software die PCI-Leistung von Intel-Chipsätzen beeinflusst

Daten zwischen Hauptspeicher und Peripheriegeräten mit hohem Durchsatz zu übertragen, ist in fast allen Bereichen von Computeranwendungen ausschlaggebend. Eine optimale Leistung ist jedoch nur erreichbar, wenn man geeignete Übertragungsmethoden und -einstellungen anwendet.

Der PCI-Bus (Peripheral Component Interconnect), der mit einer Frequenz von 33 MHz arbeitet, hat eine theoretische Bandbreite von 33 MHz × 32 bit = 132 Mbyte pro Sekunde. Dies könnte man mit einem endlosen Block-Transfer erreichen. Da reelle Block-Transfers in ihrer Länge begrenzt sind, ist die tatsächliche Bandbreite jedoch wesentlich geringer. Wenn die Blocklänge beispielsweise auf neun Zyklen begrenzt ist, also nach jedem 9. Zyklus ein neuer PCI-Block-Transfer angestoßen werden muss, und das Anstoßen eines neuen Transfers einen Zyklus benötigt, reduziert sich die theoretische Leistung auf 90 % (119 Mbyte/s).

Unter optimalen Bedingungen lassen sich solche Übertragungsraten auch in der Praxis realisieren: Ein PCI-Target sendet ununterbrochen und ohne Störungen durch andere PCI-Targets einen großen Datenblock nach dem anderen an ein anderes PCI-Target. Derartige Bedingungen können jedoch nur für extrem kurze Zeit gewährleistet werden.

Typischerweise sind mehrere PCI-Targets mit dem Bus verbunden, und jedes möchte zu irgendeiner Zeit Daten übertragen. Deshalb muss die verfügbare Bandbreite zwischen den Targets aufgeteilt werden.

Motherboard-Aufbau: Von der Bridge zum Hub

Jobangebote+ passend zum Thema

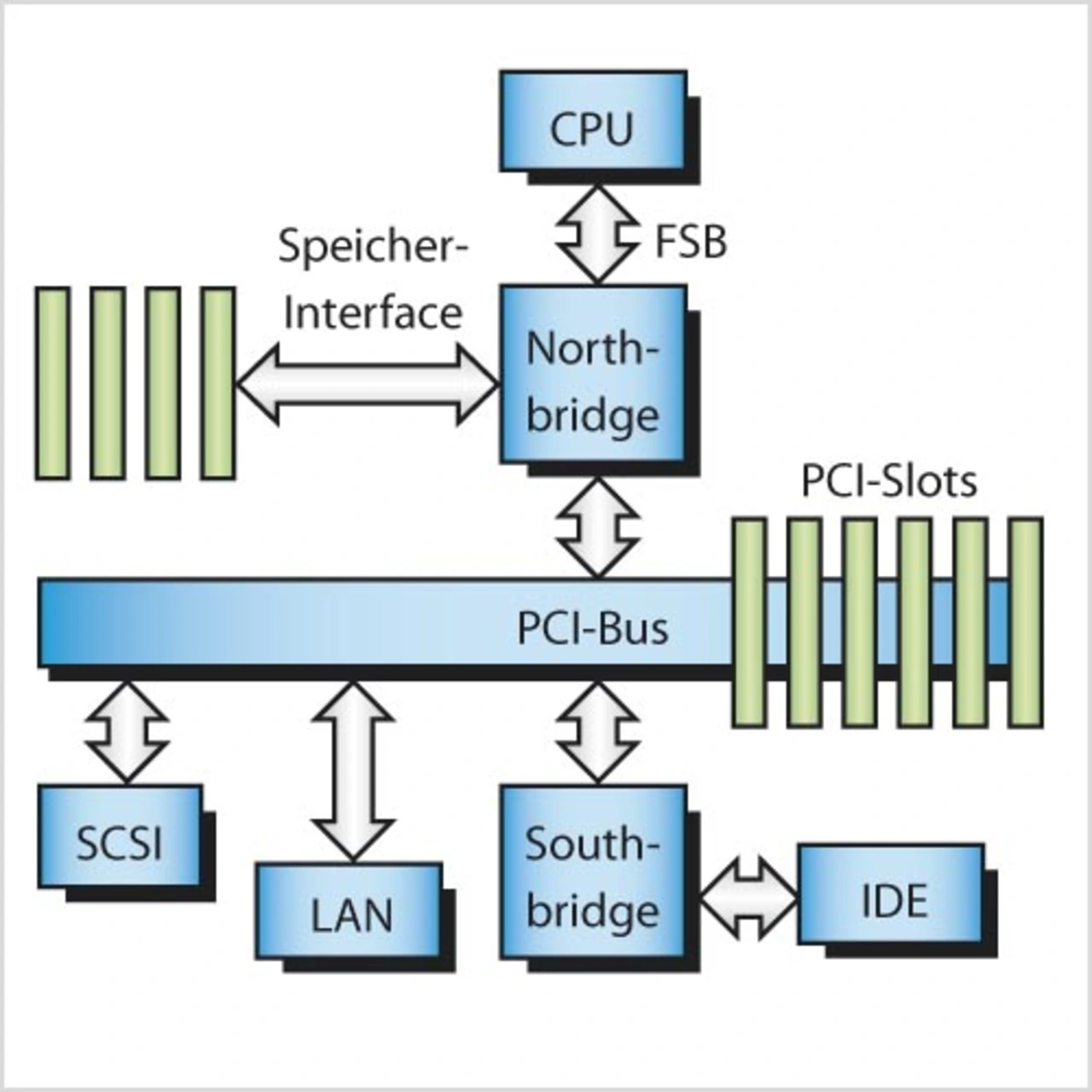

Es gibt jedoch noch weitere Faktoren, die sich auf den PCI-Durchsatz auswirken. Bei früheren Chip-Designs von Intel war der PCI-Bus das Bindeglied zwischen den Hauptbestandteilen des Chipsatzes, und die Leistungsfähigkeit dieses Busses war ausschlaggebend für die Leistung des Gesamtsystems (Bild 1). Um eine optimale Gesamt-Systemleistung zu erreichen, wurden die Schnittstellen der Chips für PCI-Übertragungen optimiert. Der CPU-Cache war ein eigener Speicher und wurde von der so genannten Northbridge verwaltet, dem gleichen Chip, durch den auch die CPU, der Hauptspeicher und der PCI-Bus angebunden wurden. Dieser Chip war in der Lage, einzelne PCI-Bus-Transfers zu einem einzelnen PCI-Block-Transfer zusammenzufassen.

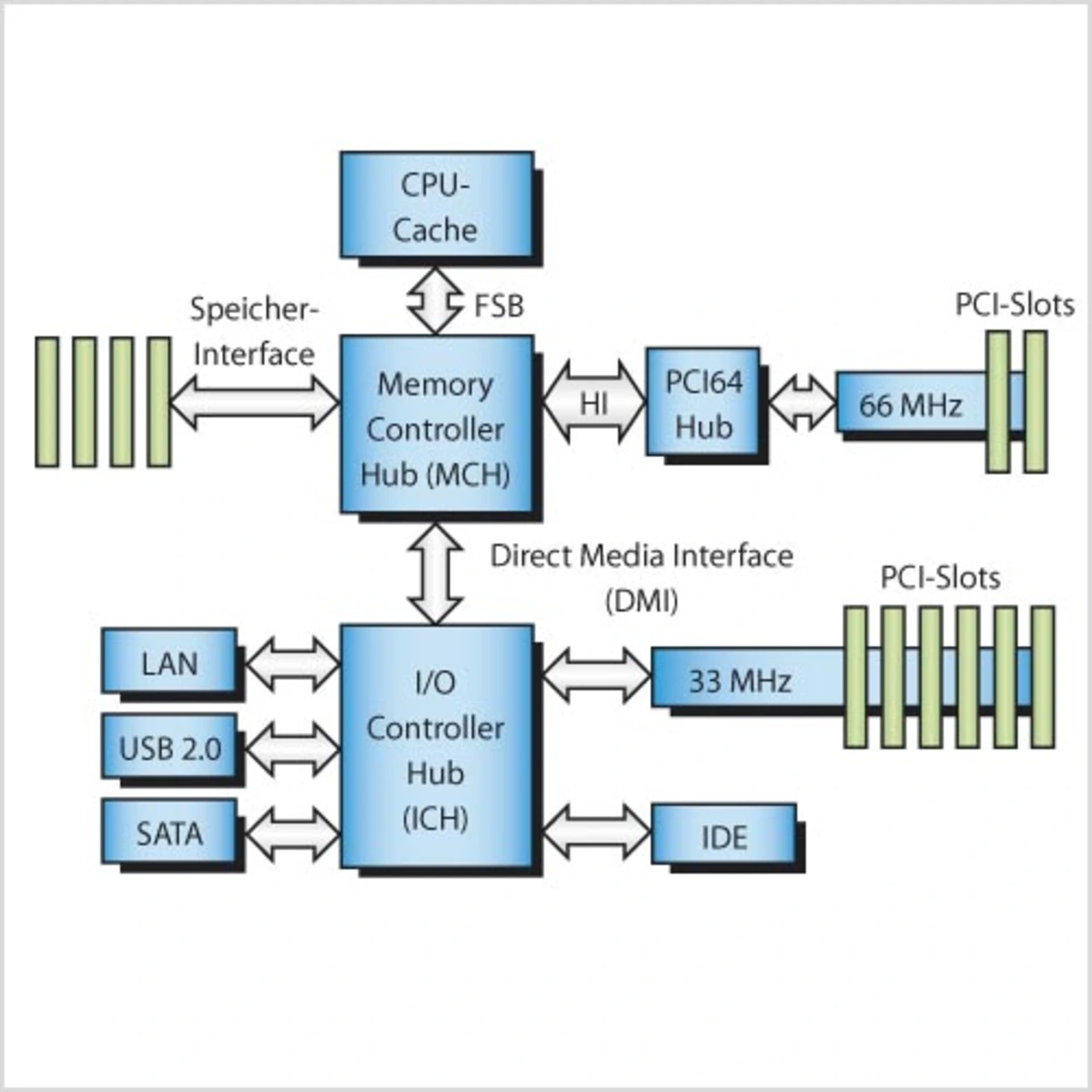

Heutige Chip-Designs von Intel bringen viele Verbesserungen mit sich. Für eine höhere CPU-Leistung wurde der Cache-Speicher auf mehrere Ebenen erweitert und hängt nicht mehr an der Northbridge, sondern befindet sich nun im gleichen Chip-Gehäuse wie die CPU. Durch die direkte Verbindung mit der CPU wird der Cache nicht durch externe Schnittstellen ausgebremst und ist somit wesentlich schneller. Aktuelle CPUs sind außerdem wesentlich schneller, und ihr Out-of-Order-Design erlaubt es ihnen, sich mit zusätzlichen Aufgaben und Operationen zu beschäftigen, während sie auf die Übertragung von Daten warten.

Mittlerweile stellt auch nicht mehr der PCI-Bus die Verbindung zwischen den Bausteinen des Chipsatzes her. Stattdessen wird mit dem „Direct Media Interface“ (DMI) eine schnellere Verbindung genutzt, die ausreichend Bandbreite für Datenübertragungen zu Schnittstellen wie Serial-ATA, Gigabit-Ethernet usw. zur Verfügung stellt. Dies ist die größte Veränderung, die auch einen enormen Einfluss auf die Datenströme hat.

Jedes Direct Media Interface ist unabhängig von allen anderen Schnittstellen und wesentlich schneller als der PCI-Bus, der im wahrsten Sinne des Wortes ein Peripherie-Bus geworden ist. Jetzt stellt der so genannte „I/O Controller Hub“ (ICH) den 33-MHz-PCI-Bus zur Verfügung, und ein PCI64-Hub den 66-MHz-PCI-Bus (Bild 2).

Während sich die Leistungsfähigkeit des Gesamtsystems verbessert hat, ist die Datenübertragung von und zu den PCI-Targets nicht unbedingt schneller geworden. Insbesondere dann, wenn die Daten per programmierter Ein-/Ausgabe (Programmed Input/Output – PIO) übertragen werden, bei der die Daten von der CPU in Einheiten von 4 byte von der Quelle gelesen und zum Ziel gesendet werden, kann der Durchsatz geringer ausfallen.

Abgesehen von Sonderfällen, bei denen z.B. Daten direkt zwischen zwei PCI-Targets ausgetauscht werden, erfolgt die Kommunikation mit einem PCI-Target in der Regel durch einen Gerätetreiber, indem Daten zwischen einem Speicher auf dem PCI-Target und dem Hauptspeicher transferiert werden. Hierfür stehen vor allem die programmierte Ein-/Ausgabe (PIO) und die Datenübertragung per Direct Memory Access (DMA) zur Verfügung. Da bei der programmierten Ein-/Ausgabe reguläre Speicherzugriffe ausgeführt werden, kann außerdem durch Veränderung der Cache-Strategie für die beiden Speicher mittels Einträgen in den „Memory Type Range“-Registern (MTRR) Einfluss auf den Datendurchsatz genommen werden.

- Wie Software die PCI-Leistung von Intel-Chipsätzen beeinflusst

- Datenübertragung zum PCI-Target mittels programmierter Ein-/Ausgabe

- Leistung erhöhen durch Änderung der Cache-Strategie

- Datenübertragung per Direct Memory Access (DMA)