Die Öffnung des Signalauges – Qualitätsmerkmal für High-Speed-Verbindungen und wie sie bei RapidIO gewährleistet werden kann

Sicherung der Signalqualität mit RapidIO

Fortsetzung des Artikels von Teil 1

Sicherung der Signalqualität mit RapidIO

Um sämtliche für das Störrauschen verantwortlichen Effekte unter Kontrolle zu bekommen, muss der Entwickler zuerst sicherstellen, dass die Impedanz der einzelnen Leiterbahnen mithilfe einer korrekten Leiterbahnbreite, des Leiterbahnabstandes und der Topologie auf den Sender abgestimmt ist. Eine Fehlanpassung wirkt sich auf die Qualität von Vorder- und Rückflanke, Einschwingzeit, Crosstalk und auf elektromagnetische Störungen aus.

Es ist auch wichtig, die geeignete Leiterbahnisolierung zwischen synchronen Signalgruppen sicherzustellen und die Leiterbahnlänge zu begrenzen sowie den Taktversatz zwischen Signalen von „differential Pairs“ zu minimieren. Das Routing sollte auch im Hinblick auf eine Begrenzung von Streuungen durchgeführt werden, indem die Layout-Übergänge auf ein Mindestmaß beschränkt werden. Die Anzahl der Vias sollte möglichst gering gehalten werden, um unerwünschte Induktivität und Streukapazität zu vermeiden. Normalerweise sind zusätzlich zu den BGA-Leitungen bis zu zwei Durchkontaktierungen erlaubt.

Jobangebote+ passend zum Thema

Eine gründliche Überprüfung der Signalintegrität ist von höchster Wichtigkeit. Mithilfe eines Schätzwerts für Streuungen können durch eine Analyse im Vorfeld der Layout-Entwicklung die zum Verständnis der Layout-Performance erforderlichen Daten ermittelt werden. Allerdings lassen sich nur mithilfe einer sorgfältigen Simulation im Anschluss an die Layout-Entwicklung jene detaillierten Daten sammeln, die zur Identifizierung möglicher Probleme hinsichtlich der Signalintegrität erforderlich sind. Dazu ist ein Simulationstool für Layouts nötig mit präzisen HSpice-Modellen, um Simulationen durchzuführen und die Ergebnisse grafisch darzustellen.

Eine gute Signalintegrität lässt sich erzielen, indem Leiterbahnen und Signalpfade so kurz wie möglich gehalten werden. Darüber hinaus sollten beide entweder mithilfe von Masseflächen abgeschirmt oder physikalisch voneinander getrennt werden. Gleichzeitig ist das Auftreten einer Fehlanpassung oder jeglicher Konfigurationen zu vermeiden, die zu Resonanz führen könnten.

Auswahl von Serial-RapidIO-Bausteinen

Auf welche Weise wählen Entwickler einen Serial-RapidIO-Switch aus? Der Hardware-Entwickler muss auf die Funktionen zur Taktgenerierung, die Vorverzerrung und auf eine Frequenzentzerrung achten. Mithilfe optimierter Packaging-Technologien, effizienter Ball-Maps und Serial-RapidIOSwitches mit asynchronem Layout lässt sich auf Systemebene ein Layout mit hoher Signalintegrität gewährleisten. Im Hinblick auf die Auswahl serieller Schnittstellen sollte sich der Entwickler für einen Switch mit geeignetem Funktionsumfang entscheiden, der auf die Anforderungen einer High-Speed-Signalübertragung ausgelegt ist.

Tundra Semiconductor bietet aktuell drei Generationen von Serial-RapidIO-Switches mit oben genanntem Funktionsumfang an. Die Tsi57x-Produktreihe umfasst die Modelle Tsi574, Tsi576 und Tsi578, die jeweils über 4 bis 16 Ports verfügen, die mit 1,25 Gbaud bis 3,125 Gbaud betrieben werden. Zu den unterstützten Übertragungsbreiten zählen ×1 und ×4, bei einem Stromverbrauch von 120 bis 200 mW pro Port. Die Tsi57x-Produktreihe verfügt über sämtliche in diesem Artikel beschriebenen Funktionen für die Signalintegrität, einschließlich Vorverzerrung auf Senderseite und Frequenzentzerrung auf Empfängerseite. Zu den neuen Funktionen dieser Produktreihe zählen Multicast, Fabric-Leistungskontrolle und eine Anzahl erweiterter Funktionen für das Traffic-Management, die für höchste Leistungsanforderungen von Anwendungen optimiert wurden. (Joachim Kroll)

| Paul Devashish devashish.paul@tundra.com |

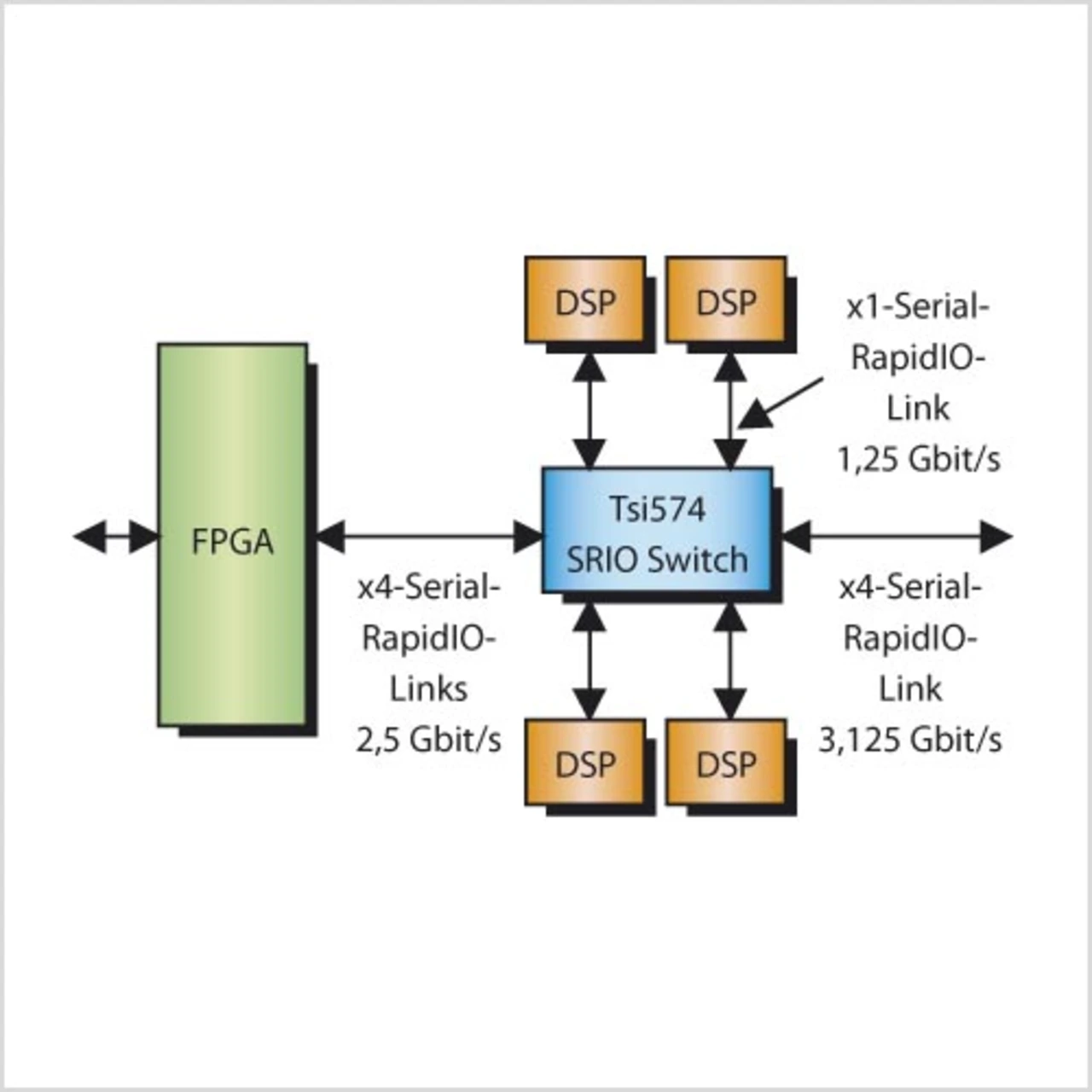

Wie in Bild 3 gezeigt, durchläuft das Signal auf dem Weg zum FPGA verschiedene Bereiche der Leiterplatte und wird unter Umständen durch elektromagnetische Störungen beeinflusst, da es möglicherweise verschiedene Layer durchlaufen muss. Für die Verbindungen zwischen den DSPs und dem Switch sind hingegen geringere Geschwindigkeiten erforderlich, da die Signale nur sehr kurze Distanzen zu überbrücken haben. Für die Verbindung zur Backplane ist unter Umständen auch eine höhere Geschwindigkeit erforderlich, da das Signal auch hier eventuell eine Vielzahl von Steckerverbindern durchlaufen muss.

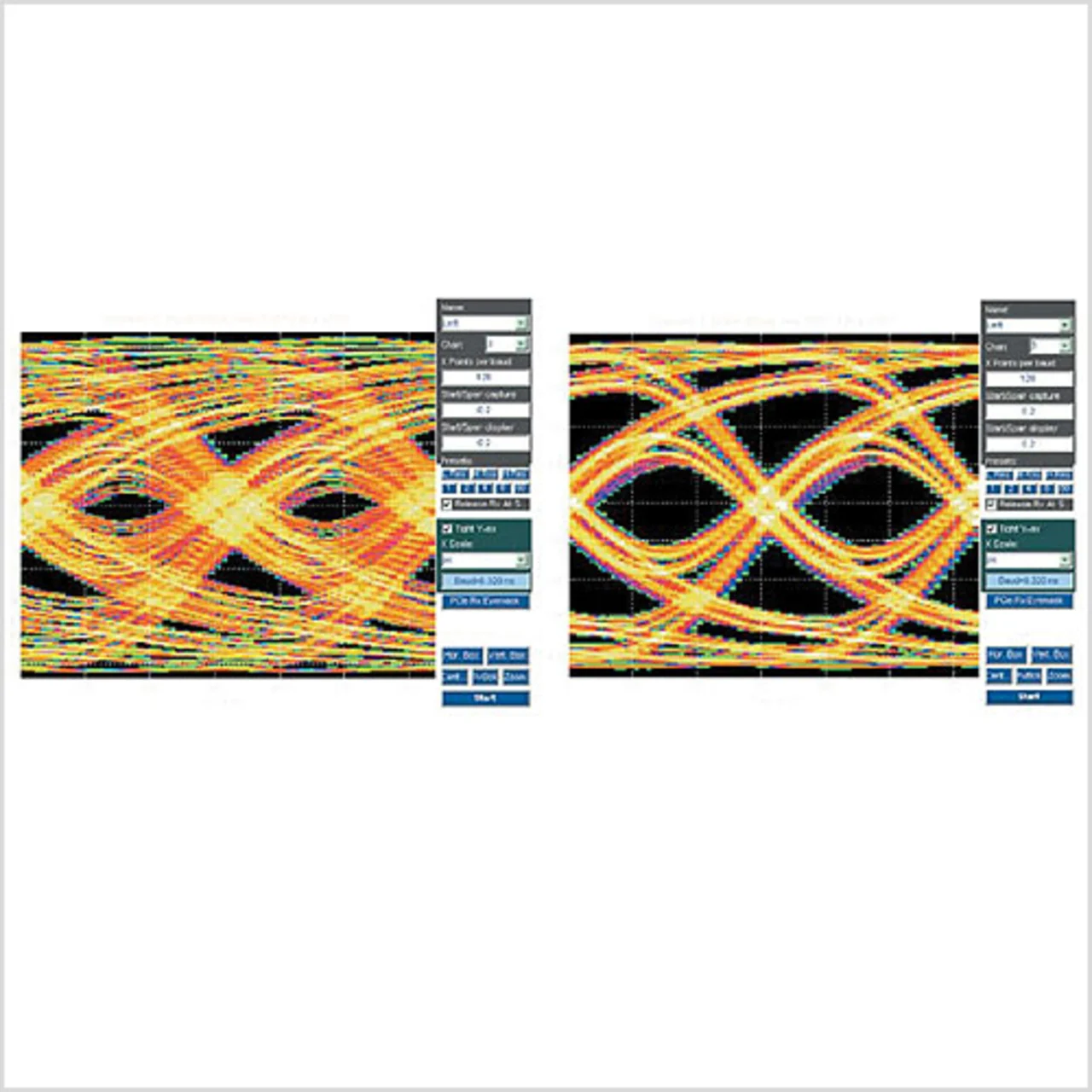

Alle drei Verbindungen haben unterschiedliche Dämpfungseigenschaften sowohl hinsichtlich Amplitude als auch Phase (Bild 4). Daher stellt jede Verbindung eigene Anforderungen hinsichtlich Frequenzentzerrung auf Empfängerseite und ist somit nur von Nutzen, wenn sie auch programmierbar ist. In Bezug auf Systemintegrität erleichtert die Verfügbarkeit dieser Funktion in den Tsi57x-Rapid-IO-Switches von Tundra das Layout auf Systemebene.

Der Serial-RapidIO-Standard unterstützt drei verschiedene Linkgeschwindigkeiten – 1,25 Gbaud, 2,5 Gbaud und 3,125 Gbaud. Ein Switch arbeitet entweder synchron, d.h., sämtliche Ports werden mit der gleichen Geschwindigkeit betrieben, oder asynchron, wobei die einzelnen Ports mit der Frequenz betrieben werden, die für die Traffic-Anforderungen des jeweiligen Links geeignet sind. Für die meisten Anwendungen stellt ein asynchroner Switch die optimale Lösung dar. Ein solcher Switch bietet den Vorteil eines insgesamt niedrigeren Stromverbrauchs durch das System. Er ist auch weniger anfällig für Crosstalk, was hinsichtlich Signalintegrität einen weiteren Pluspunkt darstellt.

Faktoren wie Bestückungsdichte und Auswahl des Substrats können im Hinblick auf die Signalintegrität eine große Rolle spielen. Zum Beispiel bieten Hochleistungs-Flip-Chips im Vergleich zum Wirebonding eine bessere Stromversorgung und verbesserte Reflexionsdämpfung. Bei RapidIO-Switches ist die Impedanzanpassung enorm wichtig, um eine Differenzimpedanz von 100 Ω mit geringer Toleranz zu gewährleisten. Ein Flip-Chip bietet hier die Vorteile verringerter Induktivität und Streukapazität – im Gegensatz zum Wirebonding.

Die Silizium-Lieferanten erleichtern sich das Leben, indem sie „Ball-Maps“ wählen, die für kurze Verbindungen zwischen Silizium-Chip (Die) und Lotperle sorgen. Die Aufgabe des Leiterplattenentwicklers ist alles andere als trivial. Für das Layout der Ball-Map ist die Umsetzung der gesamten Systemebene zu berücksichtigen. Hierfür muss beispielsweise auch die Verbindung der peripheren ICs zum Switch beachtet werden. Diese sollte optimiert werden, um die Anzahl der Layer und den auf der Platine erforderlichen Platz zu minimieren, um somit eine Verbesserung der Signalintegrität für das endgültige Layout zu erreichen. Bei ICs mit sehr dichten Ball-Maps sind viele Layer auf der Platine erforderlich, um die Signale vom IC weg zu leiten, was zu hohen Entwicklungskosten führt. Weitere Punkte, die sich auf die Wechselbeziehung von Crosstalk zwischen Signalweg und effizienten Ball-Maps auswirken, sind die Anzahl sowie die Anordnung von Spannungs- und Masseanschlüssen. Wird ein kleines Gehäuse mit zu vielen Serial-RapidIO-Ports ausgestattet, ergeben sich möglicherweise Probleme hinsichtlich der Signalintegrität aufgrund von Crosstalk. Dies hat zur Folge, dass das Auge geschlossen ist, wenn das vom Switch kommende Signal schließlich den Endpunkt erreicht.

- Sicherung der Signalqualität mit RapidIO

- Sicherung der Signalqualität mit RapidIO

- Sicherung der Signalqualität mit RapidIO

- Leiterplatten-Design: „Schallgrenze“ 300 MHz