Netzwerk- und Speichercontroller

Die Datenflut in den Griff bekommen

Fortsetzung des Artikels von Teil 1

Skalierbare Netzwerke, Intelligenterer Speicher

Skalierbare Netzwerke

Die Rechenzentrumsnetzwerke von morgen müssen sowohl schneller als auch schlanker sein – und aus diesem Grund auch intelligenter als je zuvor. Eine der wichtigsten zu bewältigenden Herausforderungen bei virtualisierten Megarechenzentren ist die Control-Plane-Skalierbarkeit. Um ein Rechenzentrum im Cloud-Maßstab zu ermöglichen, muss die Control-Plane entweder vertikal oder horizontal skaliert werden. Beim herkömmlichen Ansatz der vertikalen Skalierung werden zusätzliche oder leistungsstärkere Rechen-Engines, Beschleunigungs-Engines oder beides implementiert, um die Performance der Netzwerk-Control-Plane zu steigern.

Bei den zunehmend verwendeten Architekturen für eine horizontale Skalierung, z. B. Software Defined Networking (SDN), wird die Control-Plane von der Data-Plane getrennt und dann normalerweise auf Standardservern ausgeführt. Sowohl bei der vertikalen als auch der horizontalen Skalierung können intelligente Mehrkern-Kommunikationsprozessoren, die Universalprozessoren mit speziellen Hardwarebeschleunigungern kombinieren, die Leistung der Control-Plane drastisch verbessern. Einige Funktionen, wie z. B. Paketverarbeitung und Datenverkehrsmanagement, können häufig durch Line-Cards entlastet werden, die mit diesen speziellen Kommunikationsprozessoren ausgestattet sind.

Während die Wirksamkeit der Verteilung der Control- und Data-Planes offenbleibt, lässt sich eindeutig sagen, dass Software Defined Networks intelligente Halbleitertechnologie benötigen, um ihr Versprechen einer skalierbaren Performance einzuhalten.

Intelligenterer Speicher

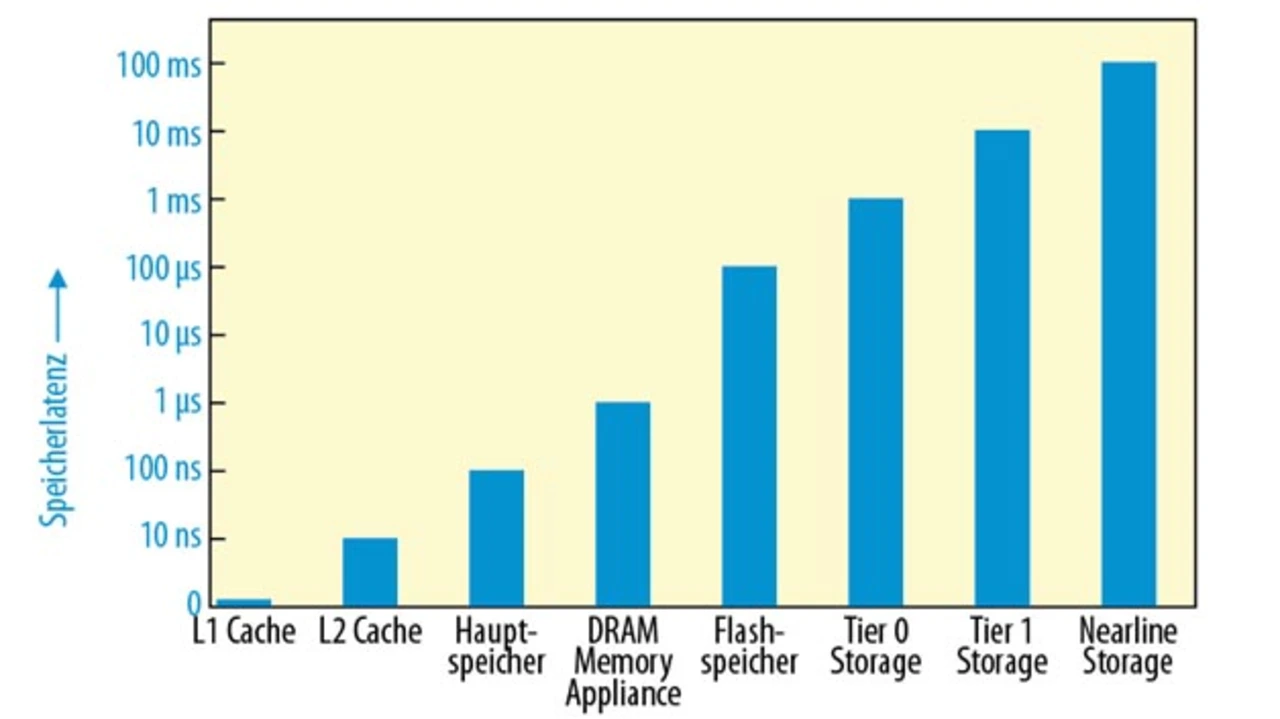

Intelligentere Halbleitertechnologie in Speichern kann ebenso dazu beitragen, die Datenflutlücke zu schließen. Der I/O-Engpass hat seinen Ursprung in der Mechanik traditioneller Festplatten und deren begrenzten Geschwindigkeiten beim Übertragen von Daten von den Laufwerksmedien; der Unterschied beträgt das Hunderttausendfache bei der I/O-Latenz zwischen Speicher (100 Nanosekunden) und Tier-1-Festplatten (10 Millisekunden, siehe Aufmacher-Bild auf Seite 1).

Ein weiterer begrenzender Faktor ist die Speichermenge, die bei herkömmlichen Caching-Systemen unterstützt werden kann (in Gigabyte gemessen); diese entspricht einem Bruchteil der Kapazität eines einzelnen Laufwerks (in Terabyte gemessen). Beides lässt wenig Spielraum für Leistungssteigerungen außer der Erweiterung des Dynamic RAM (DRAM) in Caching-Geräten oder dem Hinzufügen weiterer schnell drehender Festplatten.

Ein Solid-State-Speicher in Form eines NAND-Flash-Speichers hingegen ist besonders effektiv bei der Überwindung dieses Engpasses, da er Hochgeschwindigkeits-I/O ähnlich der von Speicher bietet, bei einer Kapazität, die der von Festplattenlaufwerken gleichkommt. Intelligente Halbleitertechnologie wiederum bietet anspruchsvolles Wear Levelling, Speicherbereinigung und Datenkompression, um die Lebensdauer von Flash-Speichern zu verbessern und erweiterte Fehlerkorrekturalgorithmen für eine RAID-artige Datensicherheit. Flash-Speicher helfen, sowohl die Kapazitäts- als auch die Latenzlücke zwischen DRAM-Caching und HDDs zu überbrücken (siehe Bild).

Jobangebote+ passend zum Thema

Solid-State-Speicher bringen normalerweise die höchsten Leistungszuwächse, wenn die Flash-Cache-Beschleunigungskarte direkt im Server an den PCI-Express-Bus angeschlossen wird. Die Caching-Software befördert Daten in den Flash-Speicher, wo sie binnen 20 Mikrosekunden wieder abgerufen werden können – das ist 140 Mal schneller als bei einer Tier 1-HDD (2.800 Mikrosekunden). Einige dieser Karten unterstützten mehrere Terabyte Solid-State-Speicher, und eine neue Klasse bietet nun sowohl interne Flash- als auch SAS-Schnittstellen (Serial-Attached SCSI), um leistungsstarken Solid-State-Speicher mit RAID-HDD-Speicher zu kombinieren. Eine PCI-Express-basierte Flash-Beschleunigungskarte kann die Datenbankanwendungsperformance in DAS- und SAN-Umgebungen um das 5- bis 10fache verbessern. Intelligente Halbleitertechnologie stellt das Herz all dieser Lösungen dar.

Jim Anderson ist leitender Vizepräsident und General Manager der Networking Components-Abteilung der LSI Corporation. Bevor er im Jahr 2005 zu LSI stieß, war er acht Jahre bei Intel, wo er u.a. Verantwortung für die Roadmap der »Mobile Platform Group« trug. Anderson hat einen MBA von der MIT Sloan School of Management, einen Master in Elektrotechnik und Informatik des MIT, einen Master in Elektrotechnik von der Purdue University und einen Bachelor-Abschluss in Elektrotechnik von der University of Minnesota.

- Die Datenflut in den Griff bekommen

- Skalierbare Netzwerke, Intelligenterer Speicher