Den Umstieg von PCI auf PCI-Express richtig machen

Fortsetzung des Artikels von Teil 3

Den Umstieg von PCI auf PCI-Express richtig machen

Auf der der PCI-Express-Schnittstelle zugewandten Seite besteht die Applikationslogik somit im Wesentlichen aus Paketgeneratoren (z.B. DMA-Controller, der Speicher Schreib-/Lese-Anforderungen initiiert oder Completion-Paket-Generator, der angeforderte Lesedaten zurückliefert) beziehungsweise Paket-Dekodierern, um ankommende Anforderungen zu interpretieren und gegebenenfalls die enthaltenen Nutzdaten in den lokalen Speicher zu übertragen.

Jobangebote+ passend zum Thema

PCI-Express-Core

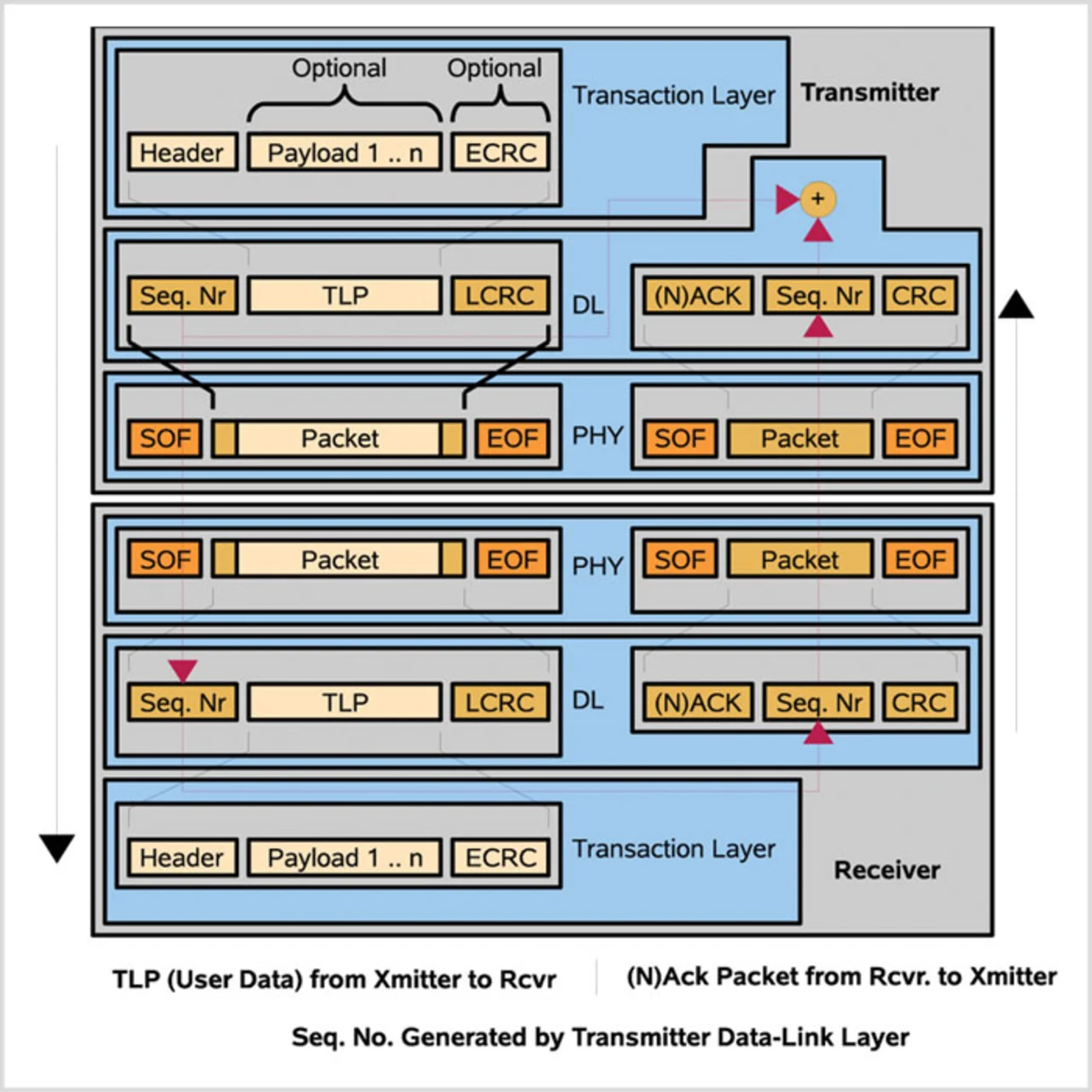

Die IP-Core-Lösung von Lattice enthält eine vollständige Implementierung der physikalischen Schicht (PHY) sowie der Datensicherungsschicht und zusätzlich Teile der Transportschicht wie zum Beispiel die »PCI Configuration Space Register « und die ECRC-Generator beziehungsweise Prüflogik. Konfigurationszugriffe von der PCIe-Schnittstelle werden eigenständig abgewickelt. Als Schnittstelle zur Applikationslogik wird ein einfacher 16-Bit-(x1-Core) oder 64-Bit-DMA-Anschluss (x4-Core) angeboten.

Strukturell besteht der IPCore aus einem SERDES-Modul (PHY-Implementierung) und einem Protokollmodul. Beide kommunizieren miteinander über zwei Zeichenschnittstellen (Eingang/ Ausgang), die aus einem 8-Bit-Datenpfad und einer Steuerzeichenanzeige (K-Leitung) bestehen. Die K-Leitung wird aktiviert, um Sonderzeichen wie zum Beispiel »Rahmenanfang« (Start of Frame, SOF) beziehungsweise »Rahmenende« (End of Frame, EOF) anzuzeigen.

Obwohl es sich bei der FPGA-Familie »LatticeECP2/M« um Low-Cost-Bausteine handelt, bietet sie neben den schon erwähnten SERDES-Blöcken noch einige andere Features, um die Anwenderlogik zu implementieren. Die Familie stellt für die Logikimplementierung beim kleinsten Baustein bereits 19 000 LUT-4 (Look-up Tables) und beim größten Baustein 95 000 LUT-4 zur Verfügung. Im Vergleich zur »LatticeECP2«-Familie wurde die Größe der Speicherblöcke um den Faktor fünf erhöht, sodass nun bis zu 1032 KBit in diskreten Speicherblöcken zur Verfügung stehen. Darüber hinaus lassen sich kleinere Speichereinheiten als Distributed-Memory realisieren. Gerade bei PCIe-Anwendungen besteht oft die Notwendigkeit, Daten zwischenzuspeichern. Hierzu kann in der LatticeECP2/MFamilie die DDR-Schnittstelle mit bis zu 400 MBit/s und die DDR2-Schnittstelle mit bis zu 533 MBit/s betrieben werden.

Bei vielen Anwendungen (Bildverarbeitung, Sensorapplikationen und Telekom) sind auch die fest verdrahteten DSP-Blöcke mit Multiplizierer, Addierern und Akkumulatoren eine große Hilfe, da sie die mögliche Systemfrequenz erhöhen und gleichzeitig die Auslastung des Bausteines verringern.

Speziell für PCI-Express x1 und x4 stehen auch Evaluierungsboards zur Verfügung, mit denen der Anwender den Core gemeinsam mit der Anwenderlogik auch im System testen kann. Dies ist sogar auch ohne IPCore-Lizenz möglich. Das Evaluierungskonzept von Lattice sieht vor, dass noch unlizenzierte Cores mehrere Stunden funktionstüchtig sind, bevor die FPGAs automatisch angehalten werden. Durch Auslösung des Resets kann der Anwender den internen Zähler aber sofort wieder zurück- und die Evaluierung fortsetzen.

Bei PCI-Express bildet ein ganzes Datenpaket eine »atomare « Übertragungseinheit. Nutzpakete bestehen aus einem drei oder vier Doppelworte großen Header und, sofern Daten mit übertragen werden, aus bis zu 1024 Doppelworten großen Nutzdaten (Payload). Ein Doppelwort besteht aus 32 Bit. Die Datensicherungsschicht hat dafür zu sorgen, dass ein Paket vom Sender zum Empfänger sicher übertragen wird. Hierzu werden zweierlei Mechanismen angewendet: das »ACK/NACK«-Protokoll und die »Flow Control«.

Jedes Nutzpaket wird mit einer 12-Bit-Sequenznummer sowie einer 32 Bit großen Prüfsumme (Link Cyclic Redundancy Check, LCRC) erweitert. Die Sequenznummer dient dazu, das Paket zwischen den Link-Partnern eindeutig zu identifizieren. Die LCRC-Prüfsumme sichert die Datenübertragung zwischen den zwei Link-Partnern gegen Datenverfälschung ab. Eine Kopie des Pakets wird im so genannten Replay-Buffer zwischengespeichert. Den Replay-Buffer überwacht außerdem ein Timer. Falls der Link-Partner weder ein ACK- (acknowledge) noch ein NACK-Quittierungspaket (not acknowledge) mit derselben Sequenznummer innerhalb des Timeout-Fensters zurücksendet, wird das Paket aus dem Replay-Buffer erneut gesendet. Das Originalpaket wird ebenso wiederholt, wenn der Link-Partner mit einer NACK-Quittierung reagiert (Bild 1). Die ACK/NACK-Pakete gehören zu den Verwaltungspaketen und haben eine Größe von 6 Byte.

- Den Umstieg von PCI auf PCI-Express richtig machen

- Den Umstieg von PCI auf PCI-Express richtig machen

- Den Umstieg von PCI auf PCI-Express richtig machen

- Den Umstieg von PCI auf PCI-Express richtig machen

- Zehn Übertragungsarten