Den Umstieg von PCI auf PCI-Express richtig machen

Fortsetzung des Artikels von Teil 1

Den Umstieg von PCI auf PCI-Express richtig machen

Nach der Überprüfung werden alle eintreffenden Completion-Pakete automatisch wieder aus der Completion-Liste entfernt. Die im Listing 1 in der Zeile 45 beginnende while-Schleife wartet am Ende der Simulation bis alle erwartete Completion-Pakete eingetroffen sind.

Jobangebote+ passend zum Thema

Der Stimuli-Generator ist in der Lage den gesamten externen Systemspeicher abzubilden. DMA-Controller in der Applikationslogik können damit beliebige Zugriffe ausführen, sowohl in einem 32-Bit-adressierbaren Speicherbereich als auch in einem 64-Bit-adressierbaren Speicherbereich. Das Speichermodell legt aber nur die tatsächlich von der Applikationslogik adressierten Bereichen an – so genanntes »Sparse Memory« –, um Simulatorressourcen zu schonen.

Wenn ein DMA-Controller in der Applikationslogik eine Leseanforderung stellt, generiert das Speichermodel das dazu passende Completion-Paket beziehungsweise -Pakete. Für die Übertragung zur FPGA-Logik muss in diesem Fall, zusammen mit dem Transaktionsgenerator, der Zugang zur Sendeschnittstelle am PCI-Express-Core koordiniert werden, damit Transaktionen, die vom Testszenario ausgelöst werden, die Completion-Paket nicht stören.

Anforderungen an den Simulator

Damit der Entwickler den Simulationsablauf auch betrachten kann, werden die Paketströme am Eingang und am Ausgang vom PCIe-Core im Stimuli-Generator überwacht. Hierbei werden wichtige Informationen wie zum Beispiel Sequenznummer des Pakets, Adresse und Tag-ID des Pakets mit ausgegeben. Im Falle von Datenvergleichsfehlern oder fehlerhaften Paketen lässt sich somit der gesamte dazugehörige Ablauf leichter nachvollziehen.

Da der IP-Core von Lattice nur im Verilog-Format vorliegt, muss der Simulator beide Lizenzen beinhalten. Die Simulatoren der Firma Aldec (»ActiveHDL« für Windows bzw. »Riviera« für Linux/Unix/Windows) unterstützen mit nur einer Lizenz das Simulieren von gemischten Verilog- und VHDL-Projekten. Eine für das Arbeiten mit Lattice-Produkten konfigurierte Version des ActiveHDL-Simulators ist Bestandteil der Entwicklungsumgebung »ispLever«. Eine kostenlose Version von ActiveHDL, die mit der isp-Lever-Starter-Software freigeschaltet werden kann, unterstützt übrigens nur eine Sprache (wählbar) und ist somit nicht geeignet.

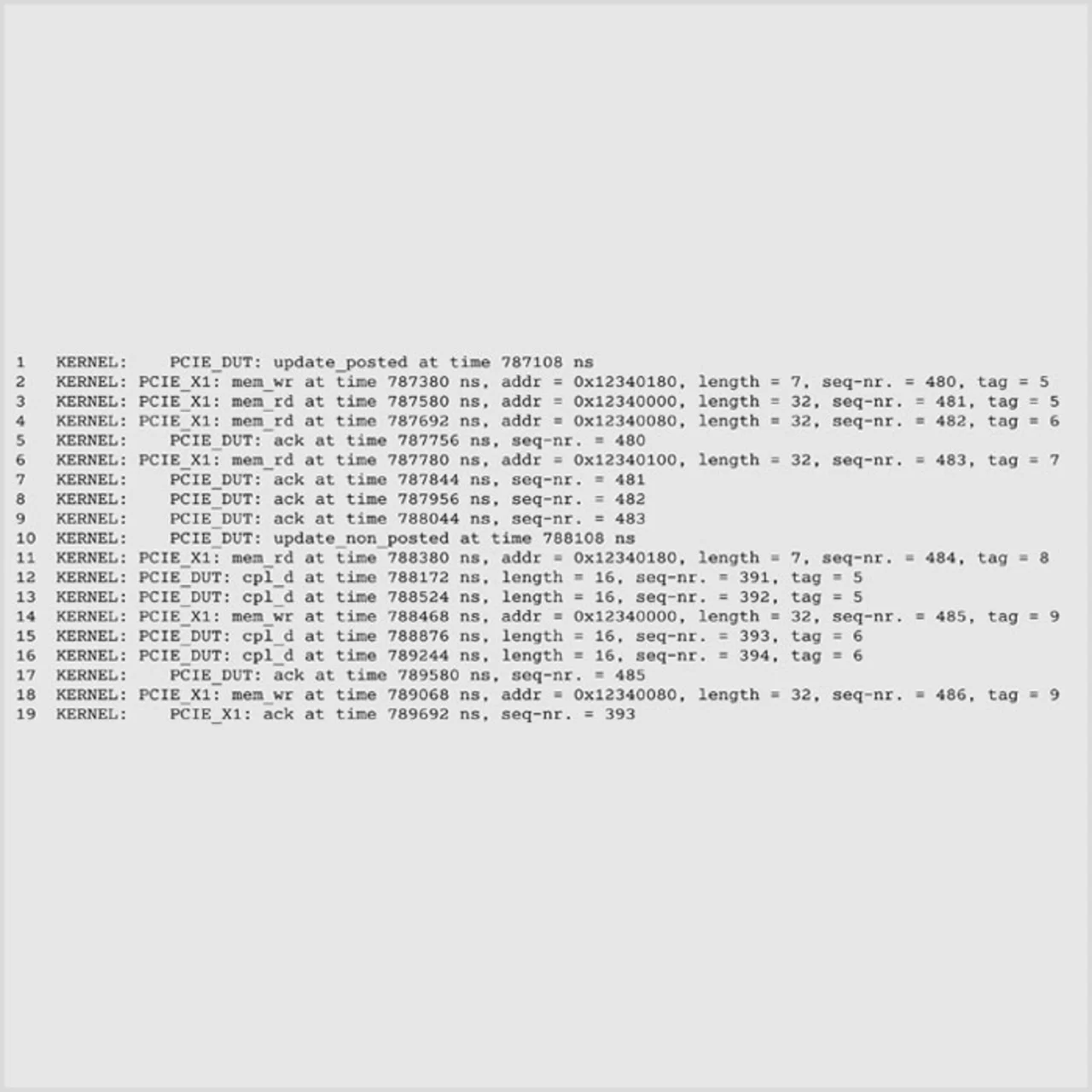

Listing 2 zeigt einen Auszug aus dem Simulationsablauf mit dem Simulator »Riviera«. Die nach links ausgerichteten Zeilen melden Aktivitäten aus der PCIe-Transportschicht, die eingerückten Zeilen zeigen Aktivitäten aus der Datensicherungsschicht, die transparent zur Applikationslogik ausgelöst werden. Die Zeilen 3, 12 und 13 zeigen eine Speicher-Leseanforderung und die zwei dazugehörigen Completion-Pakete. Im hier simulierten System war es eine Designentscheidung, die Latenz zu priorisieren. Größere Leseanforderungen werden mit mehreren kleineren Quittierungen beantwortet. Die Zeilen 9 und 17 zeigen einen Fall, bei dem zwei Memory-Read-Anforderungen mit einem einzigen ACK-Paket quittiert werden. Ein explizites ACK-Paket für die Sequenznummer 484 wird nicht generiert. Dadurch verringert sich der Bandbreitenanteil, der nötig ist, um Verwaltungspakete aus der Datensicherungsschicht auszutauschen. Die Zeilen 1 und 10 protokollieren den Austausch von FC-Paketen (Flow Control). Hier zeigt der PCIe-Core im FPGA an, dass Pufferbereiche in der Anwenderlogik zur Aufnahme von neuen Daten wieder freigegeben worden sind. (rh)

Charles Gardiner

ist unabhängiger Anbieter von Beratungs-, Schulungs- und Entwicklungsdienstleistungen und

Helmut Demel

ist Staff Field Application Engineer bei

Lattice Semiconductor

Telefon 08 11/55 05 60

www.latticesemi.com

- Den Umstieg von PCI auf PCI-Express richtig machen

- Den Umstieg von PCI auf PCI-Express richtig machen

- Den Umstieg von PCI auf PCI-Express richtig machen

- Den Umstieg von PCI auf PCI-Express richtig machen

- Zehn Übertragungsarten