Programmiergerät für I2C und SPI

Scanner steuert Programm

In der modernen Großserienfertigung von »Weißer Ware«, also Haushaltsgeräten, Waschmaschinen, Herden etc. werden häufig programmierbare Steuerungsbausteine verwendet. Scanner identifizieren dort beispielsweise die Produkte, und Programmiergeräte müssen dann flexibel genug sein, die richtige Software innerhalb kürzester Zeit automatisch aufzuspielen. Eine neue Lösung verbessert die Auslastung der Produktionslinien bei Groß- ebenso wie bei Kleinserien.

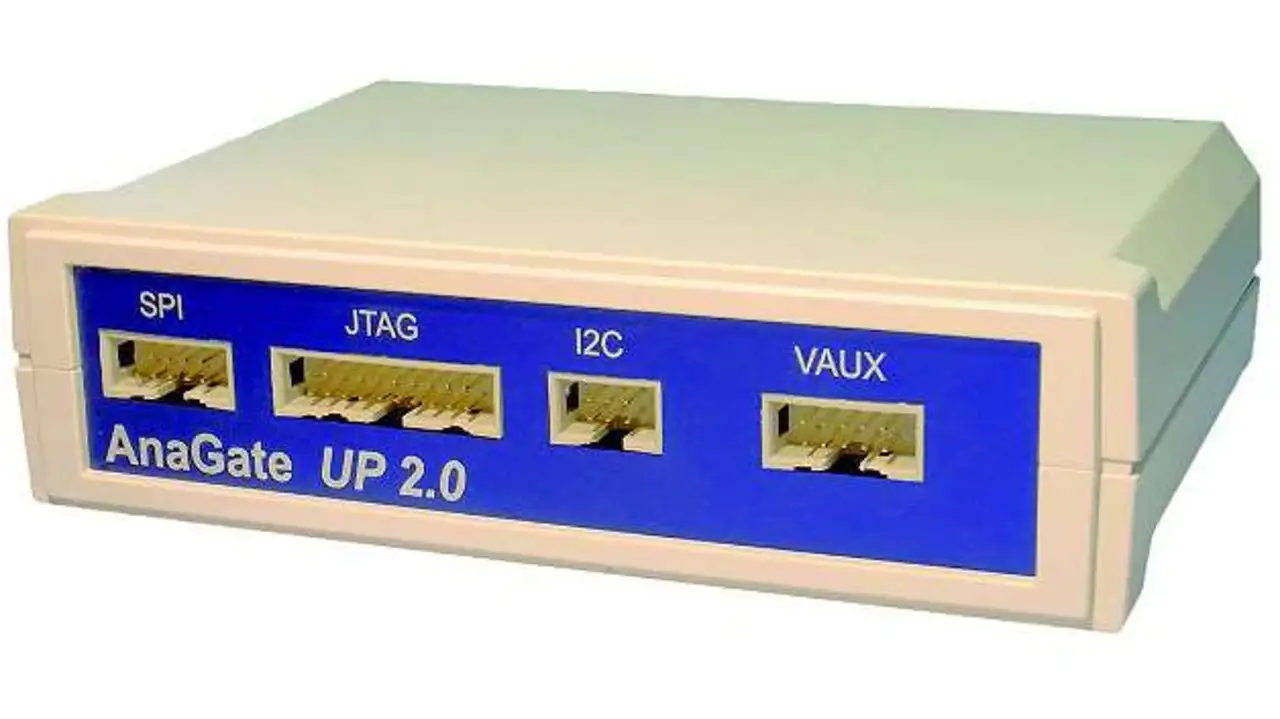

Um den Anforderungen der modernen Fertigung auf Abruf gerecht zu werden, hat Analytica den Universal-Programmer »AnaGate« so ausgelegt, dass er sowohl auf SPI- als auch I2C-Bausteine zugreifen kann.

Jobangebote+ passend zum Thema

Er eignet sich für den 24-Stunden-Einsatz in der Fertigung ebenso wie für Testaufbauten im Entwicklungslabor (Bild 1) und erlaubt je nach Anwenderwunsch den Zugriff sowohl isoliert auf einzelne Bausteine als auch auf bestückte Platinen. Grundsätzlich können dabei wahlfreie Bausteine verwendet werden, wie sie für die Programmierung von seriellen I2C/SPI-EEPROMs und SPI-Flash-Bausteinen üblich sind. Über die JTAG-Schnittstelle (OpenOCD) können auch Flash-Bausteine (NOR/NAND/CPUs) programmiert oder auch CPUs gedebuggt werden.

Die Weiterentwicklung bringt durch Ausnutzen der maximalen Paketgröße von TCP-Frames besonders für SPI Verbesserungen. Die neue Lösung braucht jetzt nur noch ein TCP-Paket, um bis zu 15 Schreibzyklen zum Gerät zu senden. Eine kostenlose, batchfähige Software für Windows und Linux zur Speicherbausteinprogrammierung, in der die einzelnen Algorithmen hinterlegt sind, ergänzt die Hardware. Bei nicht unterstützten Bausteinen lassen sich neuer Algorithmen per SPI implementieren. Standardmäßig erlaubt die Software den Zugriff auf alle gängigen I2C-EEPROM-Bausteine. Alle Zugriffsbefehle für EEPROMs sind vollständig abgebildet und lassen sich über die Programmiersoftware abrufen.

Kommunikations-Spezialitäten

Bei SPI (Serial Peripheral Interface) können theoretisch beliebig viele Teilnehmer an den Bus angeschlossen werden, wobei es jedoch immer genau einen Master geben muss, der seinerseits das Taktsignal an SCK erzeugt. Der Master legt so fest, mit welchem Slave er kommunizieren will, das geschieht über die Leitung »Slave Select«. Wird sie auf Masse gezogen, ist der jeweilige Slave aktiv und lauscht an MOSI (Master Out, Slave In), anschließend legt er seine Daten im Takt von SCK an MISO (Master In, Slave Out). Es wird ein Byte vom Master zum Slave und ein anderes Byte vom Slave zum Master transportiert.

Es ist zwar kein Protokoll für die Datenübertragung festgeschrieben, doch haben sich in der Praxis vier verschiedene Modi durchgesetzt. Diese werden durch die Parameter Clock-Polarität (CPOL) und Clock-Phase (CPHA) festgelegt. Bei CPOL=0 ist der Clock Idle-Low, bei CPOL=1 ist der Clock Idle-High. CPHA gibt nun an, bei der wievielten Flanke die Daten übernommen werden sollen. Bei CPHA=0 werden sie bei der ersten Flanke übernommen, nachdem SS (Slave Select) auf Low gezogen wurde, bei CPHA=1 bei der zweiten. Somit werden die Daten bei CPOL=0 und CPHA=0 mit der ersten Flanke übernommen, die nur eine High-Flanke sein kann. Bei CPHA=1 wäre es die zweite, also eine Low-Flanke. Bei CPOL=1 ist es folglich genau andersherum, bei CPHA=0 die Low-Flanke und bei CPHA=1 die High-Flanke.

Der Slave legt bei CPHA=0 seine Daten schon beim Runterziehen von SS an MISO an, damit der Master sie beim ersten Flankenwechsel übernehmen kann. Bei CPHA=1 werden die Daten vom Slave erst beim ersten Flankenwechsel an MISO gelegt, damit sie beim zweiten Flankenwechsel vom Master übernommen werden können. Der Master hingegen legt seine Daten immer zum gleichen Zeitpunkt an, meist kurz nach der Flanke auf Low von SCK. Mit jeder Taktperiode wird ein Bit übertragen. Beim üblichen Bytetransfer sind also acht Taktperioden für eine vollständige Übertragung nötig. Es können auch mehrere Bytes hintereinander übertragen werden, wobei in der Spezifikation nicht festgelegt ist, ob zwischen jedem Byte das SS-Signal kurz wieder auf High zu ziehen ist. Eine Übertragung ist beendet, wenn das Slave-Select-Signal endgültig auf High gesetzt wird.

Der I2C-Bus ist von der Definition her recht einfach, aber auch störanfällig. Diese Tatsache schränkt die Verwendung auf störungsarme Anwendungsbereiche ein, wo weder mit Übersprechen, Rauschen oder EMV-Problemen noch mit Kontaktproblemen (Stecker, Buchsen) zu rechnen ist. Eine Eigenschaft von I2C ist die Tatsache, dass ein Mikrocontroller ein ganzes Netzwerk an integrierten Schaltungen mit nur zwei I/O-Pins und einfacher Software steuern kann. Busse dieses Typs wurden realisiert, da ein nicht unerheblicher Teil der Kosten einer integrierten Schaltung und der verwendeten Leiterplatte von der Größe des Gehäuses und der Anzahl der Pins abhängt. Ein großes Gehäuse hat mehr Pins, braucht mehr Platz auf der Leiterplatte und hat mehr Verbindungen, die versagen können. All das steigert die Entwicklungs-, Produktions- und Testkosten.

Obwohl langsamer als neuere Bus-Systeme, ist I2C wegen des geringen Aufwands vorteilhaft für Peripheriegeräte, die nicht schnell sein müssen. Häufig wird er für die Übertragung von Steuer- und Konfigurationsdaten verwendet. Beispiele sind Lautstärkeregler, Analog/Digital- oder Digital/Analog-Wandler mit niedriger Abtastrate, Echtzeituhren, kleine, nichtflüchtige Speicher oder bidirektionale Schalter und Multiplexer. Auch elektronische Sensoren haben oft einen A/D-Wandler mit I2C-Schnittstelle integriert. Während des Betriebes können Chips zum Bus hinzugefügt oder entfernt werden (Hot-Plugging).

Der Programmer im Detail

Das Tischgehäuse des AnaGate misst 155 mm x 105 mm x 40 mm (Bild 2) und ist mit einem Adapter auch auf Hutschiene montierbar. Die Versorgungsspannung darf im Bereich von 9 V bis 28 V liegen (bei 350 mA), die Einsatztemperatur liegt zwischen 0 °C und +60 °C. Die integrierte I2C-Schnittstelle unterstützt »I2C Fast Mode Plus«, also Taktraten bis 1 MHz, sowie I2C-Read- und -Write-Befehle für sämtliche I2C-Devices im 7-Bit- und 10-Bit-Format. Einstellbare Baudraten (50 kBit/s, 100 kBit/s, 200 kBit/s, 400 kBit/s und 1000 kBit/s) sowie galvanisch getrennte SCL/SDA-Leitungen erlauben die optimale Anpassung an die Anwendung. Die SPI-Schnittstelle bietet ebenfalls individuell einstellbare Baudraten von 200 kBit/s bis 10 000 kBit/s, unterstützt sämtliche SPI-Devices und arbeitet mit galvanisch getrennten CLK/MISO/MOSI/CS-Leitungen. Auch die JTAG-Schnittstelle verwendet galvanisch getrennte TRST-, SRST-, TDI-, TMD-, TCK- und TDO-Leitungen.

Die einstellbare Geschwindigkeit beträgt 10 kBit/s bis 8333 kBit/s. Sie unterstützt die Standard-JTAG-Schnittstelle, um Flash-Bausteine zu programmieren beziehungsweise JTAG-fähige CPUs zu debuggen. Das Gerät bietet außerdem je vier digitale Ein/Ausgänge, galvanisch getrennt (3,3 V bis 24 V), und eine LAN-Schnittstelle mit 10/100 MBit/s.

Über die Autoren:

Axel Schmidt ist Geschäftsführer von Analytica und Andreas Zeiff schreibt für das Redaktionsbüro Stutensee.