Parallel-Programmierung mit bekannten Mitteln

Fortsetzung des Artikels von Teil 1

Parallel-Programmierung mit bekannten Mitteln

In einem Embedded-SoC kann ein wesentlicher Bestandteil der gesamten Berechnungen auf Interrupt-Services entfallen. Eine optimale Lastverteilung und Performance-Anpassung erfordert damit eine Steuerung – nicht nur dort, wo Programm-Tasks laufen dürfen, sondern auch dort, wo der Interrupt-Service ausgeführt wird. Linux verfügt über eine »IRQ Affinity«-Steuerschnittstelle, über die Anwender und Programme festlegen können, welche Prozessoren für einen bestimmten Interrupt zu verwenden sind, um diesen zu bearbeiten. Ein Interrupt-Controller im 1004K bietet dieses Leistungsmerkmal.

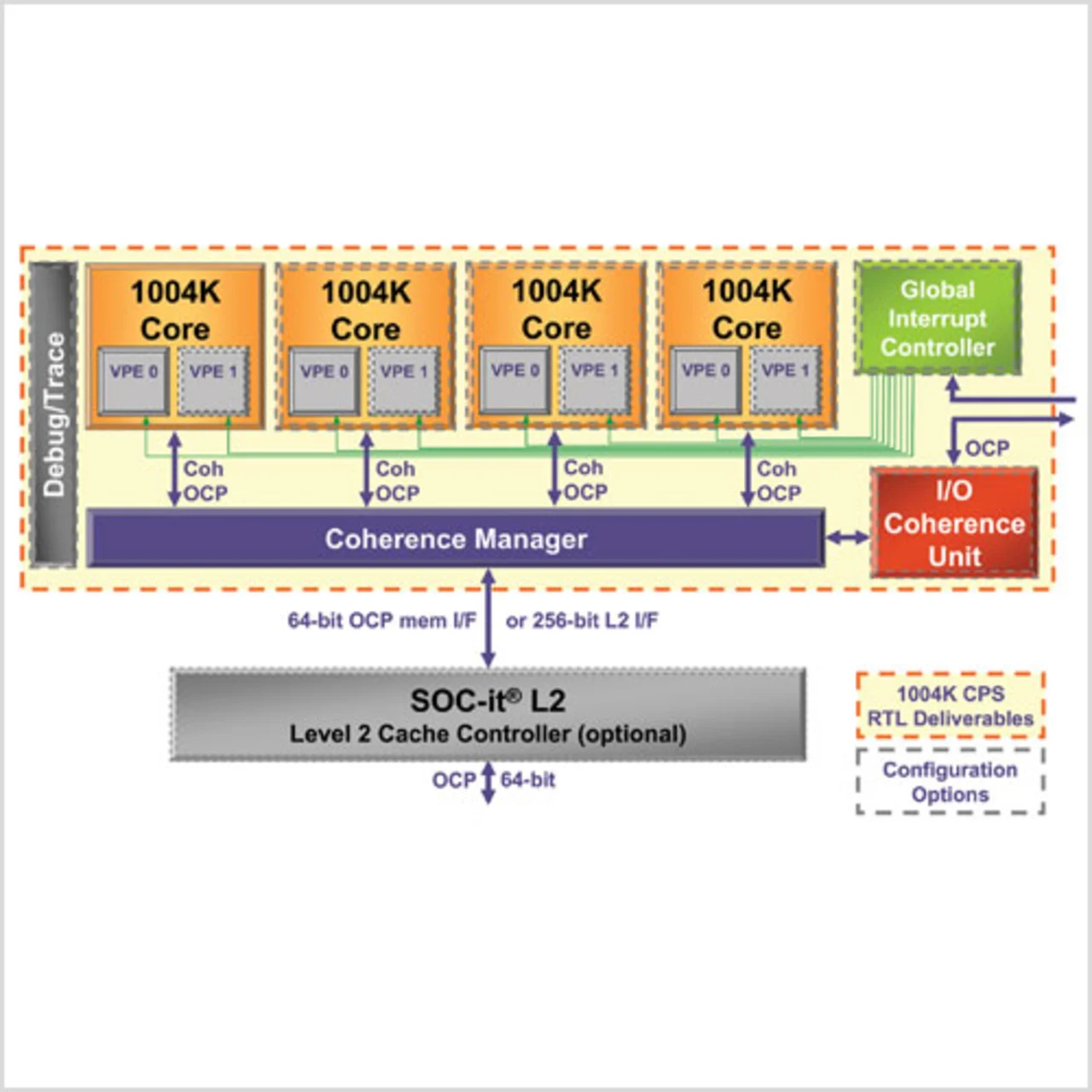

Eine Cache-Kohärenz-Infrastruktur ist von Vorteil – nicht nur zwischen Prozessoren für symmetrisches Multiprocessing, sondern auch zwischen Prozessoren und I/O-DMAKanälen. RISC-Architekturen wie »MIPS32« unterstützen softwarebasierte I/O-Kohärenz. Dies setzt voraus, dass die DMA-Puffer vor oder nach jeder I/O-DMA-Operation von der CPU verarbeitet werden, was sich messbar auf I/O-intensive Applikationen auswirkt. Beim »1004K CPS« erlaubt die Speicheranbindung des I/O-DMA über eine I/O-Kohärenzeinheit, dass der DMA-Datenverkehr mit dem kohärenten Last/Speicherfluss geordnet und integriert werden kann. Damit erübrigt sich der Software-Overhead.

Jobangebote+ passend zum Thema

Abwägungen treffen – Vorteile nutzen

Auch beim SoC-Design müssen die Entwickler wie immer Abwägungen treffen. Der Kohärenz-Manager des 1004K ordnet den Speicherdatenverkehr zwischen Prozessoren, I/O und Speicher (Bild 5). Dabei werden Zyklen zur Speicherzugriffszeit des Prozessors hinzugefügt, was normalerweise zusätzliche, verlorene Prozessorzyklen verursacht, sobald die Pipeline stehen bleibt und auf das Füllen des Caches mit Befehlen oder Daten wartet. Die 1004K-Plattform verwendet jedoch die Multithreading-Architektur von MIPS, die erstmals mit der »MIPS32 34K«-Corefamilie eingeführt wurde. Damit kann ein einziger Core mehrere gleichläufige Befehlsströme ausführen. Jeder einzelne Core des »1004K CPS« unterstützt zwei Hardware-Threads über VPEs (Virtual Processing Elements), die für die Betriebssystemsoftware wie eine einzige CPU erscheinen. Die beiden virtuellen Prozessoren teilen sich die gleichen Cache- und Funktionseinheiten und verschachteln ihre Ausführung auf der Pipeline. Bleibt ein VPE stehen, um auf ein Auffüllen des Caches seitens des Speichers zu warten, läuft das andere VPE weiter, um die Pipeline weiter zu beschäftigen. Damit erlaubt das Multithreading des 1004K, Zyklen zurückzugeben, die sonst durch die Latenz des kohärenten Speicher-Subsystems verloren gegangen wären.

Da die VPEs des 1004K für die Software wie komplette Prozessoren aussehen, inklusive unabhängiger Interrupts, lässt sich zur Verwaltung der einzelnen VPEs die gleiche SMP-Betriebssystemlogik nutzen, die auch mehrere Cores verwaltet. In der höchsten Systemverwaltungsebene sieht ein Dual-Core-1004K-System mit allen aktiven VPEs wie ein Vier-Wege-SMP-System aus. Software, die zur Nutzung von symmetrischem Multiprocessing geschrieben oder umkonfiguriert wurde, kann also auch Multithreading ausführen und umgekehrt. Während die Ansicht der Systemressourcen symmetrisch bleibt, wetteifern zwei Threads um die Nutzung einer Single-Prozessor-Pipeline. Ihre Leistungsfähigkeit ist daher geringer als die von zwei Threads, die auf unabhängigen Cores laufen. Eine solche Situation besteht in Serversystemen seit Jahren. Dort sind kohärente Cluster von Multithreaded-CPUs vorhanden, und der SMP-Linux-Kernel für den 1004K führt die erforderlichen Optimierungen zum Lastausgleich durch. Zur Optimierung der Stromaufnahme kann der Scheduler Arbeit an die virtuellen Prozessoren eines Cores verteilen, sodass die anderen Prozessoren im Low-Power-Status verbleiben. Für mehr Leistungsfähigkeit kann die Last über verschiedene Cores zuerst verteilt werden, wobei mehrere VPEs pro Core nur dann geladen werden, wenn alle Cores eine aktive Task bearbeiten.

On-Chip-Multiprocessing für hohe SoC-Leistungsfähigkeit lässt sich auf verschiedene Arten bewerkstelligen. Die statische Zerlegung der Rechenlast nach Eingabedaten oder Prozessorfunktion kann effizient sein, ist aber auch sehr unflexibel. SMP-Plattformen und -Software bieten eine flexible und leistungsfähige Rechnerplattform, die im Vergleich zu Single-Prozessoren eine erhebliche Geschwindigkeitssteigerung ermöglicht – und das mit nur wenigen oder gar keinen Veränderungen des Applikationscodes. Multithreading ergänzt SMP-Parallelismus ideal und erlaubt die größtmögliche Ausnutzung der Pipeline-Ressourcen jedes Prozessors. Das kohärente Processing-System »MIPS32 1004K« vereint Multithreading und kohärentes SMP in einem einzigen IP-Block und stellt somit eine skalierbare und hohe Embedded-Rechenleistung zur Verfügung. (rh)

Chris Berg ist Solutions Architect bei

MIPS Technologies

Telefon 0 21 91/90 02 00

mips.com/>www.mips.com

Siehe auch:

Multi-Core-Systeme sinnvoll nutzen

- Parallel-Programmierung mit bekannten Mitteln

- Parallel-Programmierung mit bekannten Mitteln

- Linux bietet SMP

- Steuerungsparallele Programmierung