Motoransteuerung

FPGA und Mikrocontroller - die Mischung machts

Fortsetzung des Artikels von Teil 1

Motorsteuerung mit SmartFusion

Für die Realisierung der Motorsteuerung wurde ein SmartFusion-Chip von Microsemi verwendet. Der Chip besteht aus einem ProASIC3-FPGA, einem ARM-Cortex-M3-Mikrocontroller und einer „Analog Compute Engine“. Die Kommunikation der Einzelsysteme findet in hierarchischer Master-Slave-Anordnung über den APB3-Bus statt. In unserer Realisierung übernimmt der Mikrocontroller die Rolle des Masters. Durch diese Kombination können die jeweiligen Stärken des FPGAs und des Mikrocontrollers optimal genutzt werden.

Der Vorteil des SmartFusion-Bausteins ist, dass für die Kommunikation zwischen den Komponenten keine externen Pins benötigt werden. Zusätzlich gibt es von Microsemi einen IP-Core für den FPGA, der die Dekodierung für Adress- und Datenbus vornimmt. Der Anwender muss lediglich einen Zustandsautomat zur Zwischenspeicherung und Weiterleitung der Daten erstellen. Der AMBA-Bus des ARM-Controllers ist ab Speicheradresse 0x40050000 erreichbar, kann also auch ohne Aufwand beschrieben werden. Der APB3-Bus des SmartFusion hält sich an die AMBA-Spezifikationen.

Grafische Konfiguration des Chips

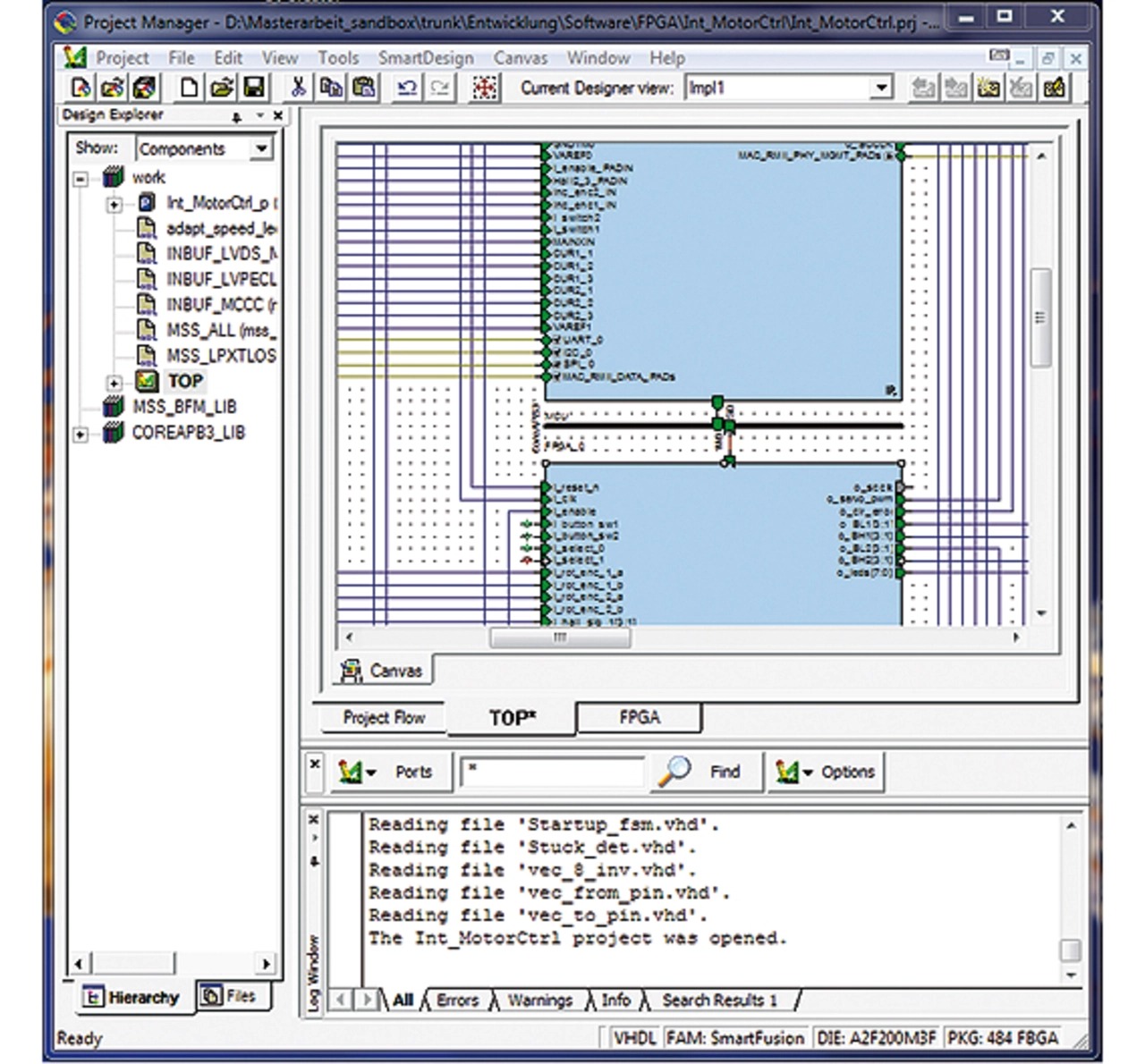

Im FPGA können so neue Peripherieeinheiten für den Mikrocontroller erstellt werden. Über den APB3-Bus können sie ebenso einfach angesprochen werden wie eine fest integrierte Einheit, z.B. UART#1. Die Konfiguration des SmartFusion-Chips erfolgt über den Libero Project Manager (Bild 2). Mit diesem von Microsemi frei erhältlichen Software-Paket, in dem mehrere Tools enthalten sind, werden die einzelnen Einheiten des FPGA/MCU-Hybriden aktiviert und je nach Bedarf auch grundlegend konfiguriert.

Die Arbeitsschritte zur Konfiguration des Chips sind:

- Erstellung eines neuen Projekts im Libero-Project-Manager,

- Parametrieren des Mikrocontrollers mit MSS Configurator (im Lieferumfang des Tools von Microsemi enthalten) sowie Festlegen des Takts für den FPGA-Teil,

- Erstellen des VHDL-Codes in Libero,

- Instanzieren der FPGA-Blöcke und Verbindung untereinander,

- Synthetisierung des VHDL-Codes mit Simplify,

- Überspielen der Logik auf dem Chip und Zuweisung des Ausgangs-Pins; das Tool dafür heißt Designer und ist im Lieferumfang des Libero Project Managers enthalten,

- Überspielen der Konfiguration auf den FPGA mit FlashPro,

- Erstellen des Mikrocontroller-Codes mit Softconsole; die Low-Level-Treiber für den Mikrocontroller erstellt der MSS Configurator automatisch.

|

01 ... 02 constant c_REG_servo_pos_ADDR : 03 std_logic_vector(23 downto 0) := x"000008"; 04 ... |

Listing 1. Beispiel für die Definition einer APB-Registeradresse im VHDL-Code.

Im ersten Schritt wird der Mikrocontroller-Anteil des Hybriden über den „Microcontroller Sub-System Configurator“ (MSS) parametriert. Unter Clock Management wird in diesem Schritt auch der Takt für den FPGA-Anteil eingestellt. Im nächsten Schritt wird über eine GUI der Mikrocontroller mit dem FPGA verbunden (Bild 2). Die Kommunikation erfolgt über den APB3-Bus. Ein Logik-Modul im FPGA, das den APB3-Bus an die weiteren FPGA-Komponenten anbindet, interpretiert die über den Bus gesendeten Daten des Mikrocontrollers und leitet sie an das jeweilige Empfängermodul des FPGA weiter. Die Registeradressen werden im VHDL-Package des Gesamtsystems festgelegt (Listing 1).

|

01 signal s_REG_systems_status : std_logic_vector(31 02 downto 0); 03 ... 04 case U_WR_ADDR is 05 when c_REG_system_status_ADDR => 06 s_REG_system_status <= U_WR_DATA; 07 ... 08 -- Motor 1 09 when c_REG_motor1_status_ADDR => 10 s_REG_motor1_status <= U_WR_DATA; 11 ... 12 when others => null; 13 end case; |

Listing 2. Master-zu-Slave Write Code im FPGA. Mit diesem Signal (Zeile 1) wird der Registerinhalt geschrieben.

Zusätzlich muss ein Signal (Listing 2) zur Speicherung des Registerinhalts angelegt werden und die neue Adresse in der Read- (Listing 3, Zeile 6) und Write-State-Machine (Listing 2, Zeile 6) des Blocks eingetragen werden. Die Software für den Mikrocontrollerteil wurde mit Microsemi SoftConsole erstellt, einem freien, auf Eclipse basierenden Software-Paket. Der MSS Configurator erstellt die Treiber für den größten Hardware-Anteil des SmartFusion-Chips automatisch. Dadurch müssen Register nicht umständlich aus Datenblättern herausgesucht werden; stattdessen kann man sich auf die Erstellung der High-Level-Funktionen konzentrieren. dann wird mit Eclipse der Mikrocontroller programmiert und das FPGA/MCU-Projekt auf den SmartFusion-Chip überspielt.

|

01 case PADDR is 02 -- INSERT NEW REGISTER-ADRESSES HERE 03 ... 04 when c_REGsysem_cmd_ADDR => 05 v.apb_rsm_state := data_phase; -- change state 06 v.prdata_ff := s_REG_system_cmd; -- assign 07 NEW data 08 ... 09 end case; |

Listing 3. Master-zu-Slave Read Code aus der State Machine des FPGA. Mit diesem Code (Zeile 6) wird zusammen mit dem Write Code (Listing 2, Zeile 6) die neu angelegte Adresse eingetragen.

- FPGA und Mikrocontroller - die Mischung machts

- Motorsteuerung mit SmartFusion

- Der Demonstrator