Vielfältiger Funktionsumfang von Hard- und Software erleichtert und beschleunigt Tests

Neue Möglichkeiten mit Boundary Scan

Fortsetzung des Artikels von Teil 2

Dipl.-Ing. (FH) Wolfgang Hascher

Das gleiche Unternehmen hat auch eine Familie von Programmier-Werkzeugen für eine große Zahl von Controllern mit integriertem Flash-Speicher von Freescale Semiconductor entwickelt. Diese Tools erlauben eine effiziente On-Board-Programmierung, so dass nicht programmierte Controller auf den Baugruppen bestückt und erst später konfiguriert sowie beliebig oft umprogrammiert werden können. Derzeit werden die folgenden Freescale-Bauteil-Familien unterstützt: ColdFire-Controller, Power-Architecture-Prozessoren, die 16-bit-Controller MC56F8000 und MC9S12 sowie die 8-bit-Controller MC68HC908 und MC9S08. Eine Unterstützung für weitere Komponenten von Freescale ist momentan noch in Entwicklung.

Lauffähig sind die erzeugten Prüf-Applikationen unter allen eigenständig arbeitenden wie auch unter den integrierten Runtime-Umgebungen von JTAG Technologies. Zum Beispiel können die Programme für die Freescale-Komponenten in die Software gängiger Testsysteme, wie z.B. In-Circuit-Tester von Agilent oder Teradyne, integriert werden. ha

ist verantwortlicher Redakteur der Elektronik für die Bereiche Messen & Testen sowie Drahtlos-Kommunikation.

whascher@elektronik.de

Ground Bounce – die Pest des Testens?

Jobangebote+ passend zum Thema

Boundary Scan – was dahinter steckt

Vor allem die hohe Packungsdichte auf modernen Leiterplatten macht es beispielsweise dem mit Nadelbett-Adaptern kontaktierenden In-Circuit-Verfahren unmöglich, in einer eng gepackten Schaltung rein physikalisch/mechanisch einen IC-Pin oder einen anderen Prüfpunkt für Messzwecke zu kontaktieren. Ganz zu schweigen von Prüfpunkten in Multilayer-Boards oder für BGA-ICs, deren Anschlusspunkte überhaupt nicht direkt zugänglich sind, weil unter dem Bauelement angeordnet.

Mit Boundary Scan steht jedoch ein standardisiertes Verfahren (IEEE-Standard 1149.x) zum Testen digitaler und analoger Bausteine (und auch zum Programmieren) ohne direkten mechanischen Zugriff auf diese Bauelemente zur Verfügung.

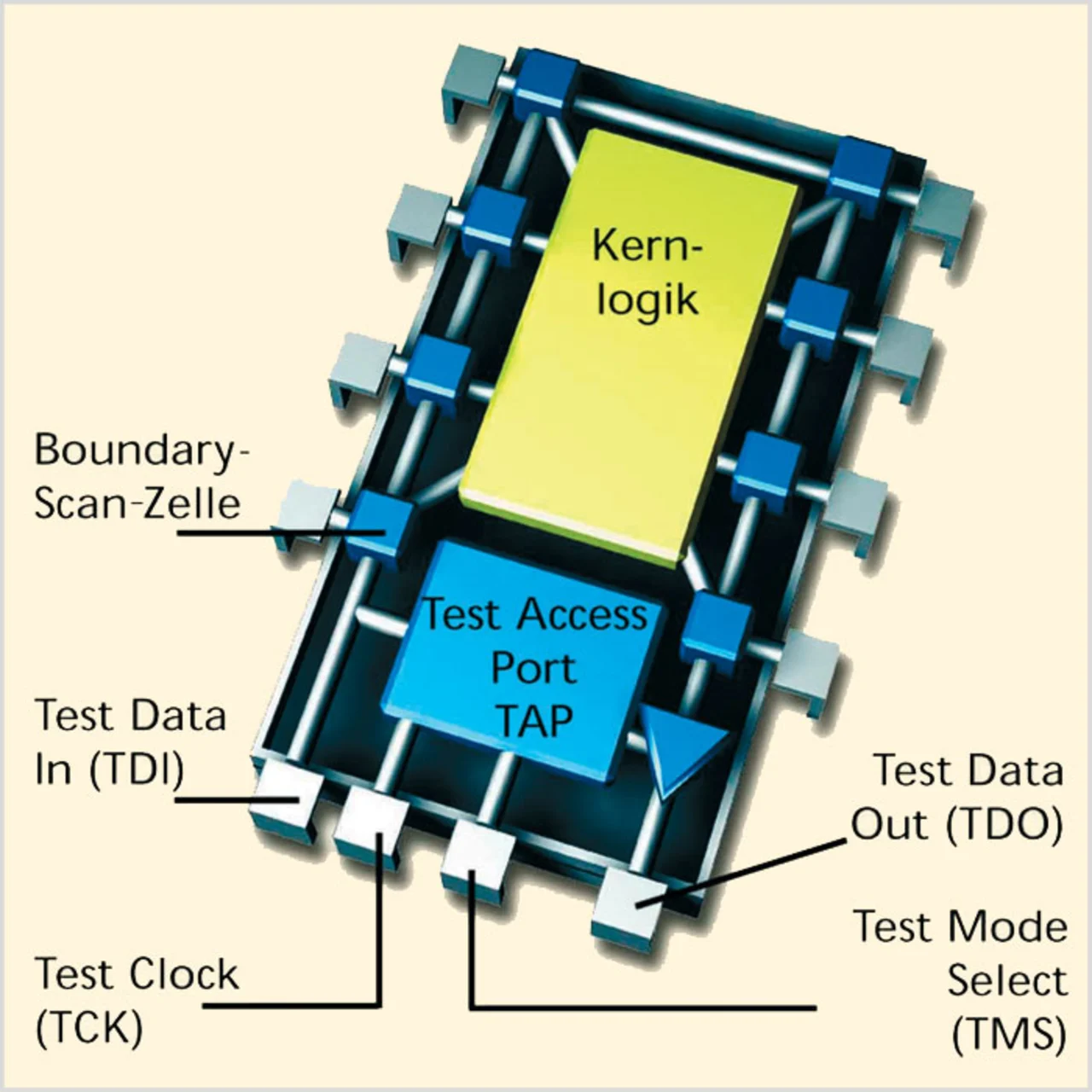

Außer der Kernlogik eines ICs ist in einem Boundary-Scan-fähigen Chip zusätzliche Logik implementiert. Diese Testlogik-Einheiten sind zwischen Kernlogik und physikalische Pins des Schaltkreises integriert; sie nennen sich „Boundary-Scan-Zellen“ (Bild) und bestehen aus einer Anordnung von Registern und Multiplexern. Um die Funktion des Anschlusses, in den hinein die Boundary-Scan-Zellen geschaltet sind, nicht zu beeinträchtigen (Input, Output, bidirektionaler Anschluss), sind gewöhnlich mehrere Boundary-Scan-Zellen mit einem einzigen physikalischen Pin verbunden. Sämtliche Boundary-Scan-Zellen sind seriell zu einem Schieberegister hintereinandergeschaltet und bilden den seriellen Scanpfad. Längen von mehreren tausend Bits für den Scanpfad sind heutzutage nicht mehr ungewöhnlich.

Um die Zellen zu stimulieren und auszulesen, ist in jedem Boundary-Scan-IC eine Steuerlogik, der Test Access Port (TAP), integriert. Diese Logik besteht aus einer „Finite State Machine“ mit 16 Zuständen, die im Wesentlichen die Umschaltung zwischen Funktions- und Testmodus sowie die Ansteuerung der verschiedenen Register realisiert.

Beim Boundary-Scan-Test nach JTAG werden Spannungs- bzw. definierte Logik-Pegel seriell durch die Boundary-Scan-Zellen „durchgetaktet“. Durch das Vorhandensein bzw. durch die Veränderung der eingetakteten Prüfmuster, jeweils gemessen an anderen Schaltungspunkten, kann man Kurzschlüsse/Unterbrechungen in der Baugruppe (an Lötverbindungen), die Spannungsversorgung sowie in gewissem Umfang auch die innere Funktion von Bauelementen und die Arbeit von Speicherzellen in Flash- oder PLD-Komponenten analysieren. Sogar analoge und nicht „Boundary-Scan-fähige“ Komponenten sind mittlerweile mit testbar.

Aufgrund des getakteten Einlesens zeitlich definierter Spannungspegel in den Baustein beim Test kann man z.B. Flash- oder PLD-Bauelemente auch gleich programmieren (In-System-Programmierung). Sie müssen jedoch hierfür konzipiert sein.

Im Standard IEEE 1149.x sind in diesem Zusammenhang die Spezifikationen des TAP-Busses sowie der Scan-Zellen festgelegt. Die zugehörigen Standards:

- IEEE 1149.1: Statischer, digitaler Verbindungstest;

- IEEE 1149.4: Analoger Verbindungs- und Parametertest;

- IEEE 1149.6: Dynamischer, digitaler Verbindungstest;

- IEEE 1532: Standard zur In-System-Programmierung.

- Neue Möglichkeiten mit Boundary Scan

- Neue Möglichkeiten mit Boundary Scan

- Dipl.-Ing. (FH) Wolfgang Hascher