Test von PCI-Express-2.0-Produkten

Fortsetzung des Artikels von Teil 1

Test der Jittertoleranz

Eine der wichtigsten Messungen der physikalischen Schicht ist die der Jittertoleranz eines PCIe-Empfängers. PCIe 2.0 legt die zulässige Jittertoleranz eines Empfängers genauer fest und berücksichtigt dabei speziell eine neue Art Jittererzeugung zum Empfängertest, die Spectrally Distributed Random Jitter (RJ), Dual Tone Deterministic Jitter (DJ) und Residual Spread Spectrum Clocking (SSC) umfasst.

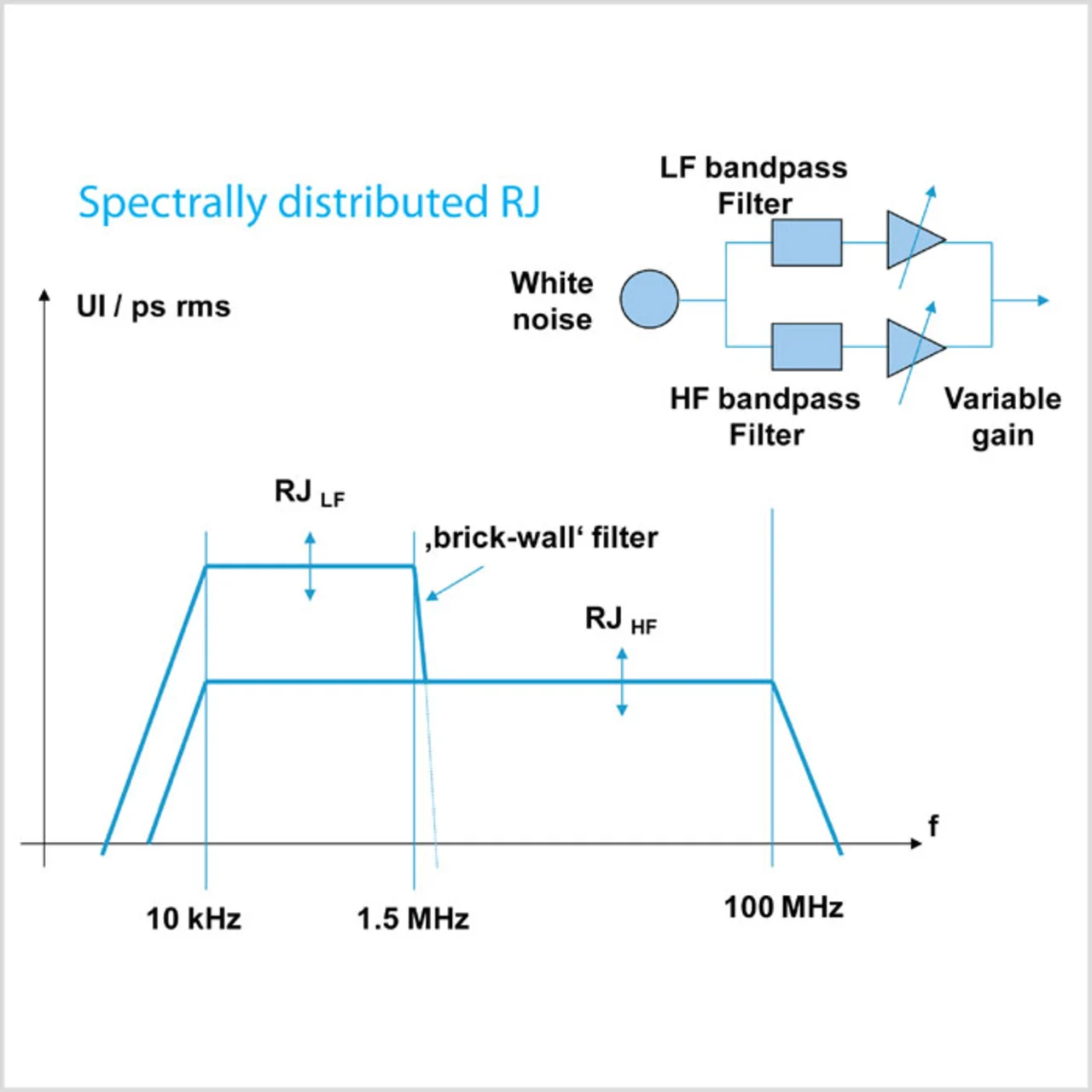

Bild 1 zeigt Spectrally Distributed Random Jitter über der Frequenz. Weißes Rauschen (unbegrenzte Bandbreite) enthält bei allen Frequenzen die gleiche Energie. Die Spezifikation nimmt hier an, dass bei niedrigeren Frequenzen mehr Random Jitter auftritt, bei höheren Frequenzen weniger. Der tatsächliche Betrag hängt vom Testfall ab. Die Eckfrequenz beträgt 1,5 MHz. Hier erfolgt ein abrupter Abfall der Filterkurve (»Brickwall Filter«).

Jobangebote+ passend zum Thema

Bild 2 zeigt das Prinzip des Dual Tone Deterministic Jitter. Normalerweise würde Deterministic Jitter als sinusförmiger Jitter zugefügt, wobei die Jitter-Frequenz über die Zeit verändert würde. Beim Dual Tone Deterministic Jitter werden zwei sinusförmige Jitter gleichzeitig zugefügt, einer mit niedriger Frequenz, einer mit höherer Frequenz. Nach Wahl kann das niedrigfrequente Signal kontinuierlich über den Frequenzbereich zwischen Minimal- und Maximalfrequenz gewobbelt werden. Der aktuelle Betrag beider Signale hängt von der Testeinstellung ab.

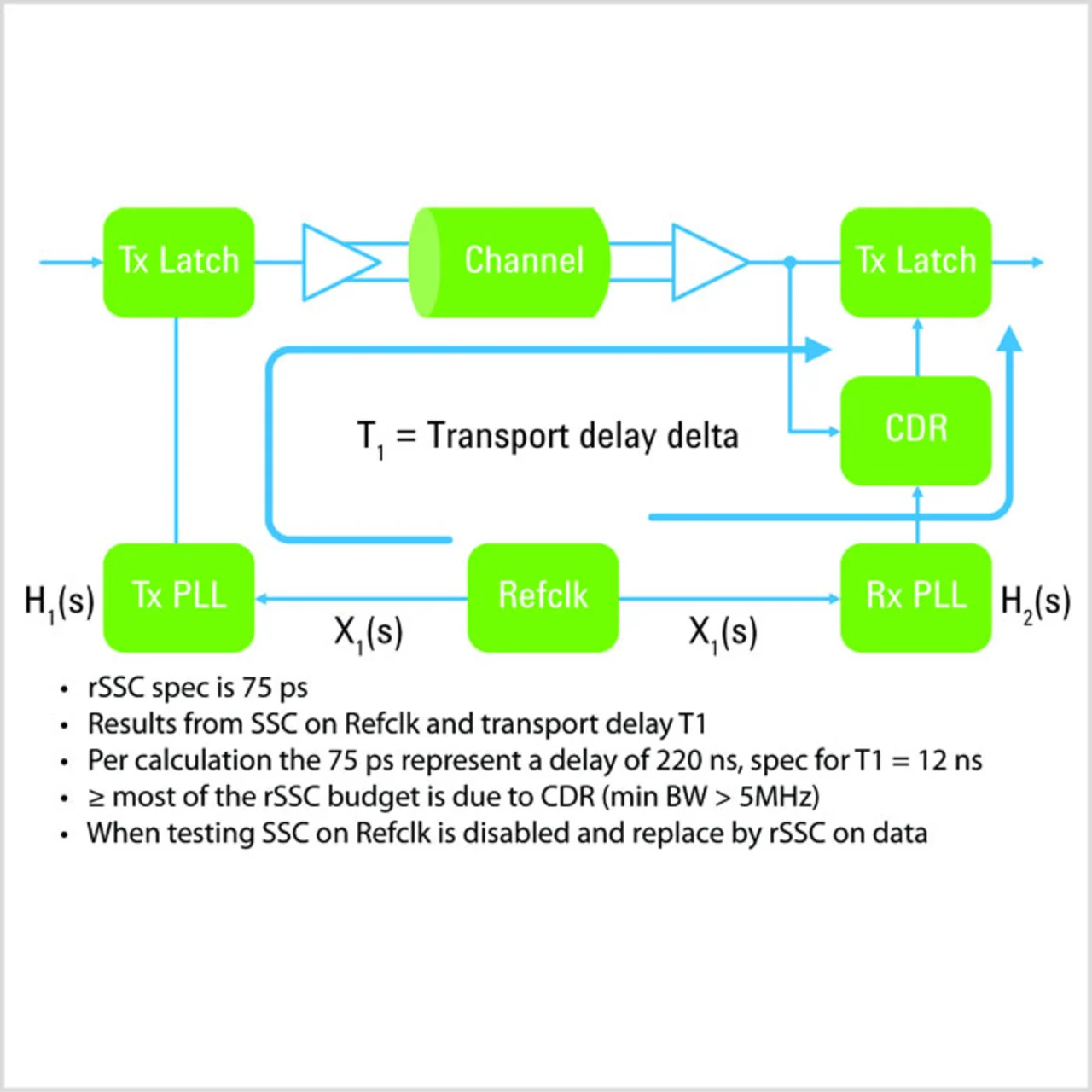

Bild 3 zeigt die Spread-Spectrum-Modulation (SSC). Eine solche Modulation wird definiert durch die SSC-Abweichung (typisch 500 ppm) und die SSC-Frequenz (typisch 30 bis 33 kHz). Die Abweichung erfolgt typischerweise nach unten: Für eine Nominaldatenrate von 5 GB/s bedeutet eine Abweichung von 500 ppm, dass die Datenrate mit einer Frequenz von 30 bis 33 kHz zwischen 5 und 4,975 GB/s schwankt. Im Idealfall ist die Modulation dreieckförmig, in der Praxis kommt aber alles zwischen Sinusform und Dreieck vor.

Bitfehlerratentester wie etwa der serielle Hochleistungs-BERT Agilent J-BERT N4903B erlauben die Charakterisierung der Jittertoleranz am Eingang des Testgeräts. Der Tester prüft die Standardkonformität, indem er Belastungssituationen gemäß Norm erzeugt, etwa einen PICe-2.0-Random Jitter nach Norm, Dual Tone Periodic Jitter, Intersymbolinterferenz (ISI), Sinusinterferenz, SSC und Residual-SSC. Man muss hierzu die Testgeräte im Loop-Back-Mode betreiben, den der Bitmustersequenzer des J-BERTs stimulieren kann. Entwicklungsingenieure sparen wertvolle Messzeit, wenn sie die Jittertoleranz mit dem automatischen Messprogramm erfassen.

Zur Signalanalyse verfügt der Agilent BERT über interne Taktrückgewinnung, schnelle Jittermessungen, einen BERT-Scan, Augendiagramm und Maskentests zur Bewertung des PCIe-2.0-Designs.

- Test von PCI-Express-2.0-Produkten

- Test der Jittertoleranz

- Testen unter Fehlerbedingungen