Bitmustergenerator und Logikanalysator im Verbund

Stimulieren und Erfassen

Fortsetzung des Artikels von Teil 2

Stimulieren und Erfassen

Aus Zeit- und Ressourcengründen ist bei komplexen Systemen ein vollständiger Test oft nicht möglich. Die Entwicklungsingenieure testen in diesen Fällen typischerweise die Grenzen des Betriebsbereichs oder Worst- Case-Kombinationen. Beispiele für Worst-Case-Bedingungen bei Hochgeschwindigkeitsdigitaltests sind etwa:

- Man legt an den Eingang des Testobjekts einen Stimulus an, der den Eingang mit der schnellsten spezifizierten Datenrate zwischen bestimmten Werten umschaltet, und beobachtet am Ausgang mit einem Logikanalysator, ob Funktionsfehler auftreten. Gängige Testmuster sind das Umschalten zwischen den Hexwerten 5 und A sowie »wandernde Einsen«. Dabei handelt es sich um ein Testmuster, mit dem sich jedes Bit eines Busses einzeln testen lässt. Der Test beginnt mit einer 1 im niedrigstwertigen Bit. Alle anderen Bits sind 0. Mit jedem Taktzyklus wandert die einzelne 1 auf dem Bus eine Stelle höher.

- Bei Übertragungsleitungen, Puffern oder anderen Schaltungen, die Signale unverändert durchlassen sollen, testet man auf ungewollte Signalbeeinflussungen durch Übersprechen, indem man ein Signal (das »Opfer«) auf 1 oder 0 hält, während man Signale in räumlicher Nähe (»Angreifer«) mit Mustern beschickt, die häufig zwischen 0 und 1 umschalten. In einer Worst-Case-Situation sind alle Signale eines Busses außer dem Testsignal »Angreifer«, das heißt: jedes andere Signal in einem Design kann das Testsignal ungünstig beeinflussen. Der Anwender konfiguriert den Bitmustergenerator so, dass er das Testmuster kontinuierlich auf den Eingang des Testobjekts gibt und beobachtet am Ausgang der Schaltung, ob Fehler auftreten, oder lässt den Logikanalysator auf Änderungen des Opfersignals triggern. Um das Übersprechen auf einem Opfersignal zu sehen, verwendet man ein Oszilloskop oder einen Logikanalysator, der Analogsignale erfassen und darstellen kann.

Jobangebote+ passend zum Thema

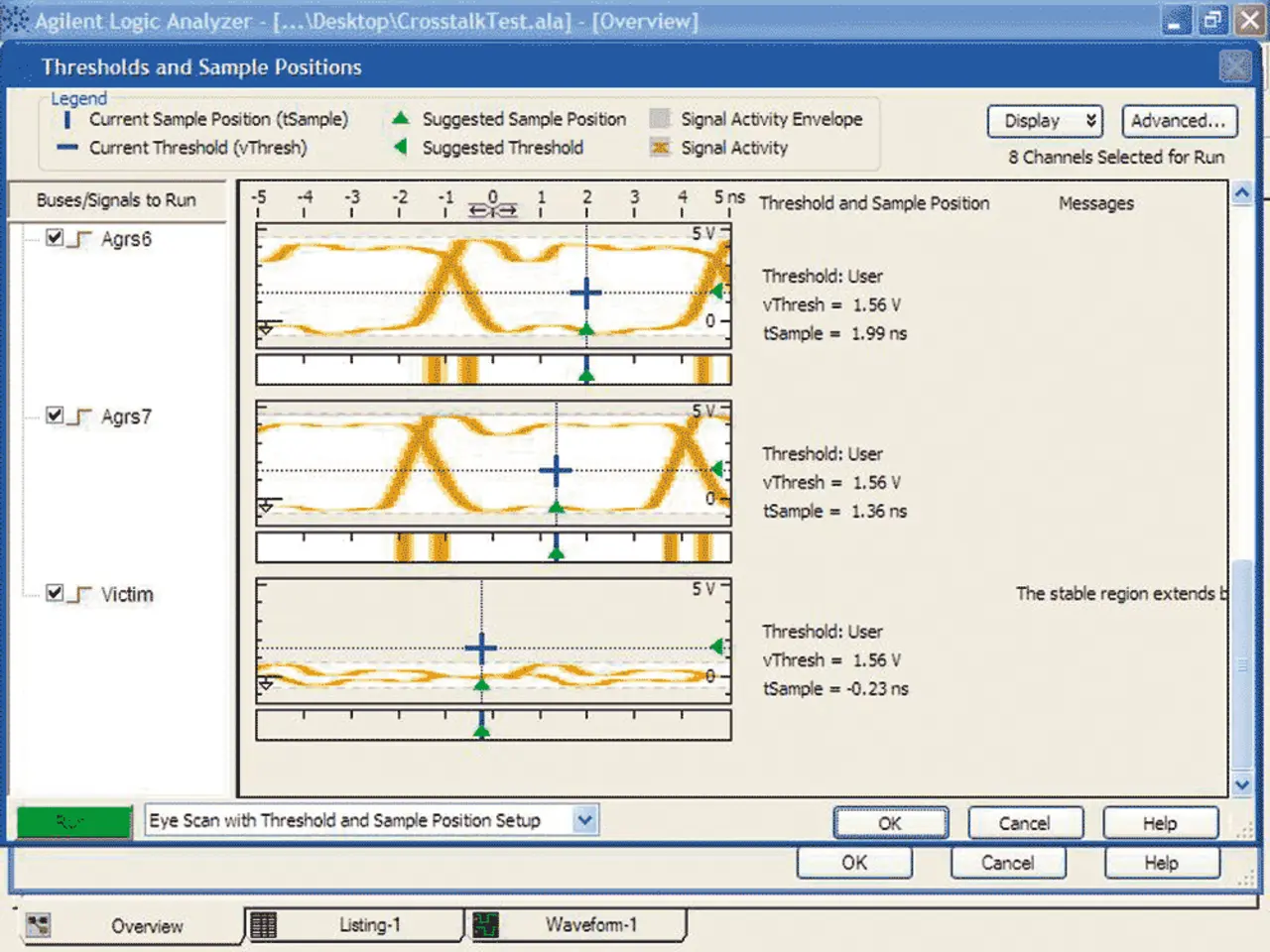

Die Augendiagrammdarstellung des Digitalsignals in Bild 2 auf einem Logikanalysator »16903A« zeigt, wie ein Logikanalysator das Ausmaß des Übersprechens bei einem Opfersignal mit normalem Signalhub visualisieren kann. Sieben Angreifersignale wurden mit dem gleichen alternierenden Signal angesteuert, das jeweils auf der ansteigenden Flanke eines 180-MHz-Taktes den Logikwert wechselte. Das Opfersignal lag räumlich in der Mitte eines 8-Bit-Busses, der auf einer kleinen Leiterplatte durch ein FPGA geführt wurde. Man sieht, dass das Übersprechen etwa 20% des TTL-Signalhubs (0 V bis 5 V) der Angreifersignale beträgt.

- Intersymbolinterferenz (ISI) tritt auf, wenn eine Signalleitung aufgrund unzureichender Treiberleistung oder ungeeigneter Terminierung nicht genügend Zeit hat, sich auf Logikpegel 1 aufzuladen oder auf Logikpegel 0 zu entladen. Mit dem Bitmustergenerator lassen sich Muster einspeisen, die Worst-Case-Bedingungen für ISI schaffen. Ein Muster, mit dem sich eine mögliche ISI auf einer einzelnen Datenleitung erkennen lässt, besteht beispielsweise aus zwölf Einsen, gefolgt von einer einzelnen 0 und so weiter (1111111111110111111 1111110...). Man kann auch das umgekehrte Muster benutzen (00000000 00001000000...). Diese Muster sorgen für maximale Ladung oder Entladung der Datenleitung und versuchen dann, mit einem Einzelbit den gegenteiligen Logikzustand zu erreichen. Bei unzureichender Treiberleistung erreicht der Ausgang der Übertragungsleitung beim Umschalten nur eines Bits den korrekten Spannungspegel möglicherweise nicht.

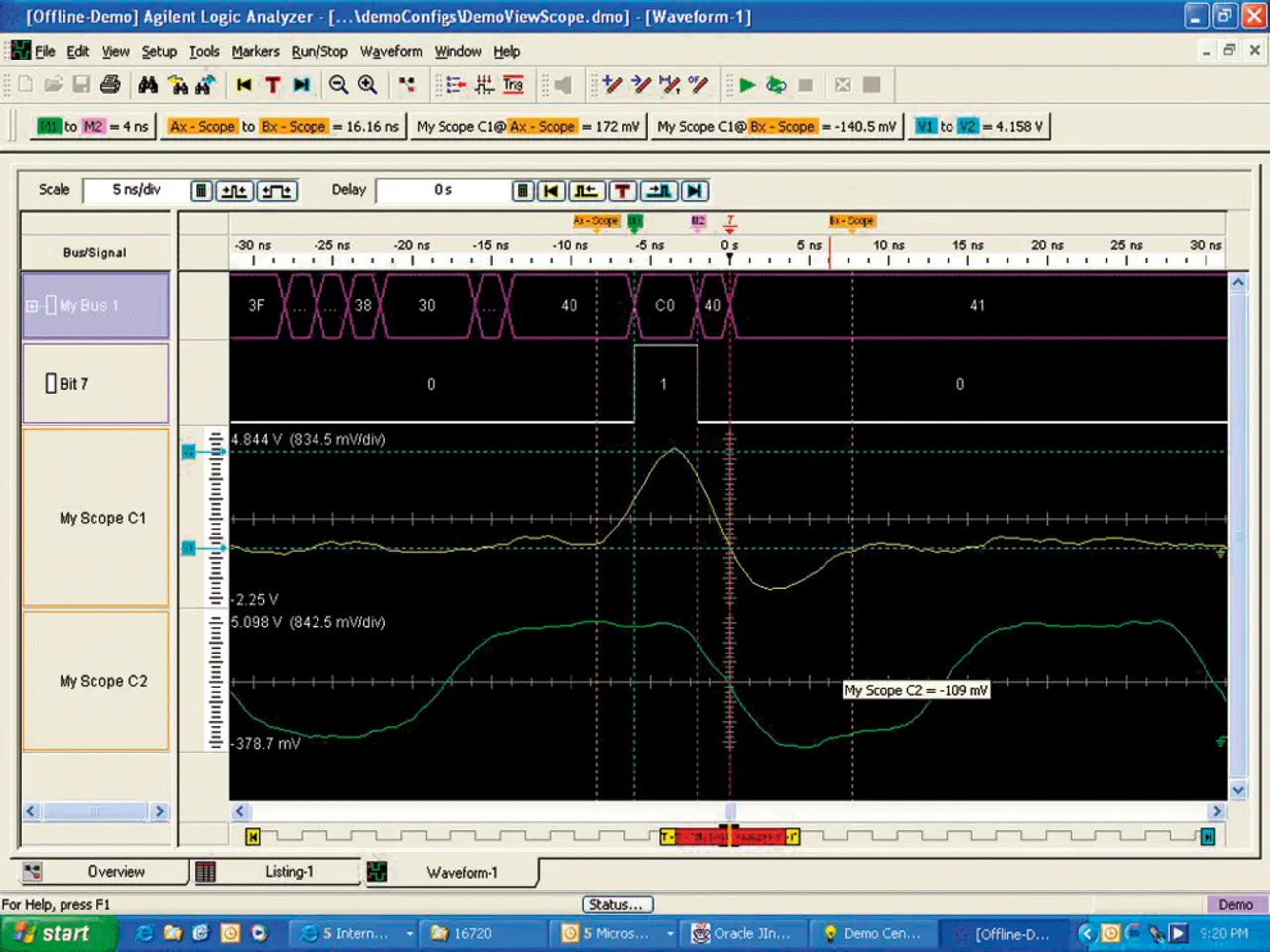

Robuste Systeme kommen problemlos auch mit schwierigen Bitmustern zurecht. Programme zur Testautomatisierung können Messgeräte fernsteuern – auch eine Kombination von Logikanalysator und Bitmustergenerator. Wenn der Anwender beim Debugging von Systemen nach intermittierenden Phänomenen sucht, die sich nicht recht fassen lassen, ist es sinnvoll, die oben beschriebene Technik (Eingangssignale simulieren und Ausgangssignale beobachten) nach dem Motto »Teile und herrsche« anzuwenden. Dabei wird das Testsystem in einzelne Funktionseinheiten aufgeteilt und diese einzeln mit Bitmustergenerator und Logikanalysator durchgemessen. So lassen sich in einem fehlerhaft arbeitenden System verdächtige Funktionseinheiten einzeln als Fehlerursache ausschließen. Eine weitere Einsicht in physikalische Parameter bei »zweifelhaften« Systemen bietet ein Oszilloskop, das Signale analog darstellt. Bild 3 zeigt eine zeitkorrelierte Oszilloskop-Darstellung eines Signals.

- Stimulieren und Erfassen

- Methode 2: Erfassen und stimulieren

- Stimulieren und Erfassen