Kompakt-Oszilloskope für den USB können immer mehr

Fortsetzung des Artikels von Teil 1

Kompakt-Oszilloskope für den USB können immer mehr

Zum Lieferumfang gehört als Software „PicoScope 6“ für Windows, die die Verarbeitungsleistung des PCs, dessen Speicherkapazität, die grafischen Möglichkeiten und die Netzwerkfähigkeit für das Oszilloskop nutzbar macht. Laut Vertriebsunternehmen benötigen selbst Einsteiger nur wenig Zeit, um die Benutzeroberfläche umfassend zu beherrschen, obwohl diese auch für professionelle Benutzer viele verschiedene Funktionen und Optionen bereitstellt. Dazu zählen die Spektralanalyse, eine Persistenzanzeige, automatische Messungen, erweiterte Triggerfunktionen und mehrere mathematische Auswerte-Algorithmen. Interessant auch die Aufzeichnungsfunktionen: Das Gerät speichert Wellenformdaten in mehreren Text- und binären Datenformaten, inkl. CSV, PNG, BMP und Matlab. Die exportierten Daten können daraufhin mit anderen Anwendungen weiterverarbeitet werden. Zum Lieferumfang gehören auch eine API und Beispiele für LabVIEW, C, C++, Delphi und Visual Basic. Über diese Software-Schnittstellen können Benutzer eine Integration in die eigene Software realisieren.

Jobangebote+ passend zum Thema

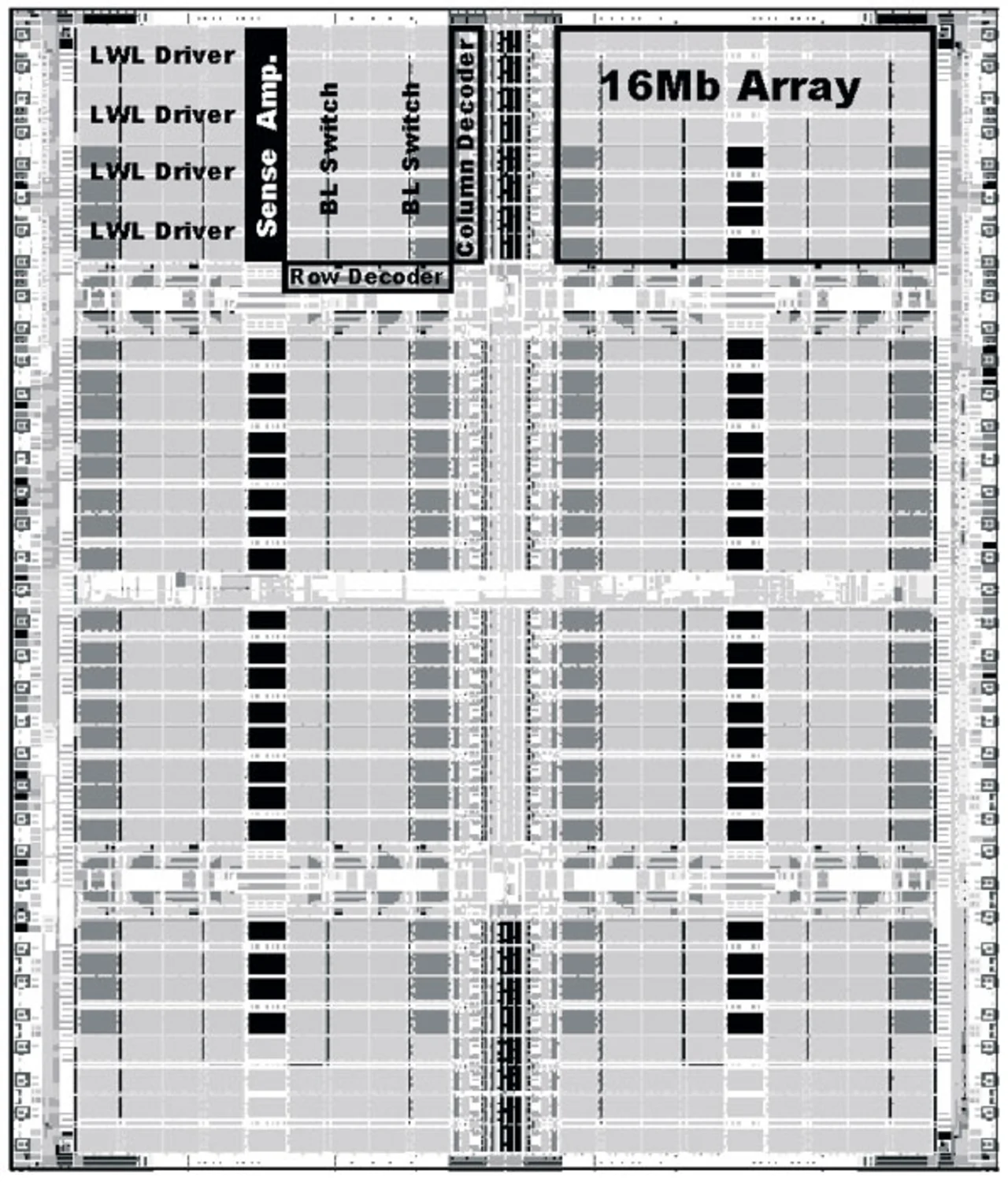

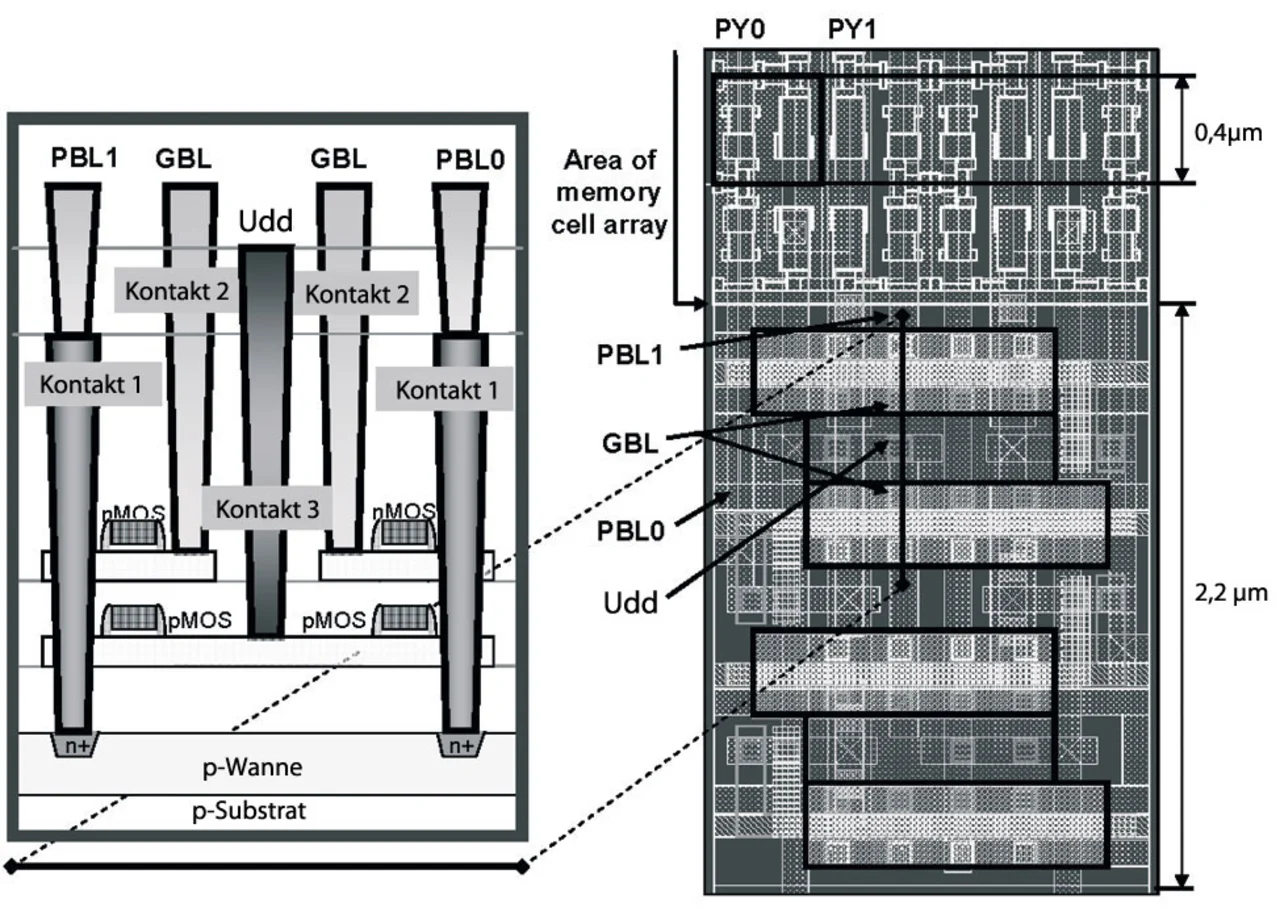

Eine höhere Programmiergeschwindigkeit bei Flash-Speichern lässt sich mit der parallelen Programmierung mehrerer Zellen erreichen. Ein typischer Flash-Speicher, der mit einer Betriebsspannung von 1,8 V versorgt wird, braucht in der Regel eine Spannung von 6 V bei hohen Strömen zur Programmierung der Speicherzellen. Normalerweise erzeugt eine kapazitive Ladungspumpe die über der Betriebsspannung liegende Programmierspannung. Wollte man auf diese Weise mehrere Zellen parallel programmieren, würden schnell Chipfläche und Leistungsaufnahme drastisch zunehmen. Eine ungewöhnliche Konstruktion hat Intel bei einem 128-Mbyte-NOR-Flash-Speicher gewählt, bei dem eine Induktivität auf den Flash-Speicher-Chip gebondet wurde, die die Betriebsspannung erhöht und die Energie auf einen Kondensator überträgt. Die dazugehörige Steuerschaltung ist auf den Die integriert. Vorteile dieses Ansatzes sind – dank ei-nes höheren Wirkungsgrades von 85 % – eine niedrigere Stromaufnahme von 47,5 mA im Vergleich zu einer kapazitiven Lösung (Wirkungsgrad 20 %) sowie eine kleinere Chipfläche. Mit der induktiven Spannungsverstärkung lassen sich 16 bis 32 Zellen parallel programmieren anstelle von 2 bis 4 bei einer rein kapazitiven Lösung, so dass nun eine Programmiergeschwindigkeit von 3 Mbyte/s bei einem Programmierstrom von 21 mA möglich wird.

Dynamische Speicher – hohe Bandbreiten und hohe Speicherdichten

Kombination aus Scope und Signal-GeneratorNicht jede Anwendung erfordert ein High-End-Oszilloskop; oft schon genügt ein einfacheres Gerät, das dafür zusätzliche Betriebsarten mitbringt. Wenn es zum Beispiel um den mobilen Einsatz in Wartung und Service geht oder um die Ausstattung von Arbeitsoder Praktikumsplätzen in der Ausbildung: Hier zählen nicht zuletzt auch Eigenschaften wie Multifunktionalität, Transportierbarkeit (inklusive Zubehör), einfache Handhabung und auch ein günstiger Preis. Mit dem „Red-Scope 25 MHz“ ist ebenfalls bei Meilhaus ein weiteres USB-Gerät im Angebot, das für diese Bereiche bestimmt ist. Das handliche Modul (Bild 4) vereint ein 2-Kanal-Oszilloskop, einen Spektrum-Analysator, einen Datenlogger und einen 8-bit-Arbiträr-Waveform-Generator. Die Bandbreite beträgt 25 MHz, die Echtzeit-Samplingrate bis zu 200 MS/s (1 Kanal; 4 GS/s für repetierende Signale) und die Tiefe des Sample-Pufferspeichers bis zu 16 000 Samples. An den PC/Notebook wird es über USB 2.0 angeschlossen, die Versorgung erfolgt vom PC über diesen Bus.

Im Lieferumfang enthalten sind eine praktische Transporttasche, zwei Tastköpfe, das USB-Kabel, eine Installationsanleitung sowie die CD mit Gebrauchsanleitung und einer Software für Windows XP SP2 und Vista (32 bit). Die Software bildet ein komplettes Oszilloskop am PC-Bildschirm nach und unterstützt unter anderem die Datensicherung in diversen Formaten inkl. CSV, PNG-/BMP-Bilder und Matlab-Binär-Dateien. Außerdem gibt es Treiber und Beispiele für LabVIEW, C/C++, Delphi, Visual Basic.

Bus-Spezialist am USB

Eine Scope-Box mit speziellen Bus-Analyse-Fähigkeiten ist ein anderes Gerät der PicoScope-Reihe, der Typ 4423 (www.priggen.com). Das buchgroße und via USB an einen Rechner koppelbare Scope ist gedacht für die Analyse an CAN-Bus- und FlexRay-Architekturen, es hat einen Speicher mit 64-fach höherer Kapazität als in den früheren Versionen. Ein erweiterter Eingangsbereich von ±100 V macht externe Spannungsteiler bei den meisten Tests überflüssig. In Kombination mit einem Diagnose-Kit kann man mit dem Oszilloskop nahezu alle elektrischen Komponenten an Antrieben und in Fahrzeugen prüfen, einschließlich aller gängigen Sensoren, ebenso die CAN-Bus-Integrität. Die Software ermöglicht auch Prüfungen beispielsweise an Batterien. Das USB-Scope wird mit praxisgerechter Software geliefert; ein Kit im Koffer mit nützlichen Sonden und Zubehör ist ebenso verfügbar wie weitere Sets für Tests an der Kfz-Elektronik.

Dipl.-Ing. (FH) Wolfgang Hascher

ist verantwortlicher Redakteur der Elektronik für die Bereiche Messen & Testen sowie Drahtlos-Kommunikation.

whascher@elektronik.de

Siehe auch:

USB in der Messtechnik

Wer braucht Oszis?

Dynamische Speicher haben in jüngster Zeit bedeutende Fortschritte im Einsatz in Applikationen gemacht, die hohe Übertragungsbandbreiten erfordern. Neben konventionellen DRAMs lassen sich auch Entwicklungsansätze in Richtung von Silicon-on-Insulator- (SOI) und Dual-Ported-DRAMs sowie in Richtung besonders schneller und besonders sparsamer DRAMs beobachten. Mit weiter schrumpfenden Strukturen spielen auch die Prozessabweichungen eine immer größere Rolle. Aufwendige statistische Analysen korrelierter Prozessparameter ermöglichen eine genauere Modellierung der „Worst-case“-Bedingungen in der Variation der Bauelemente-Parameter.

Einen skalierbaren kondensatorlosen 128-Mbit-DRAM-Baustein mit „Floating Body Cell“ stellte Toshiba vor (Bild 6). Der auf SOI-Basis hergestellte, 64,6 mm2 große Chip verfügt über eine Ladungsauffüll-Funktion (charge-replenishing), die das Datenerhalt-Verhalten verbessert. Die Zugriffszeiten liegen bei 18,5 ns im Normalbetrieb. Ferner gibt es einen virtuellen SRAM-Mode (VSRAM), der sich auf die Eigenschaft des quasi nichtdestruktiven Lesevorganges stützt, wobei hier die Zugriffszeit bei 25,7 ns liegt.

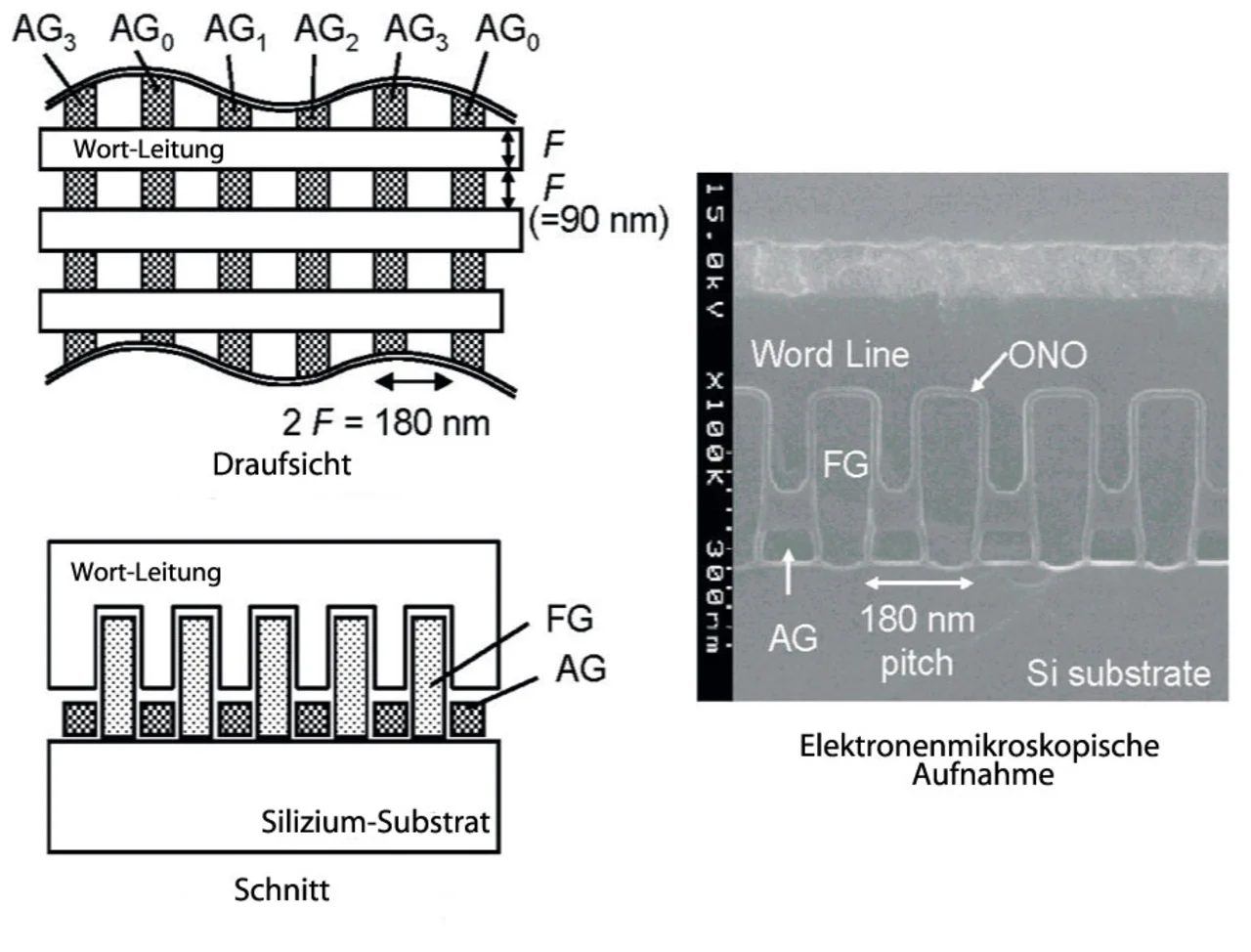

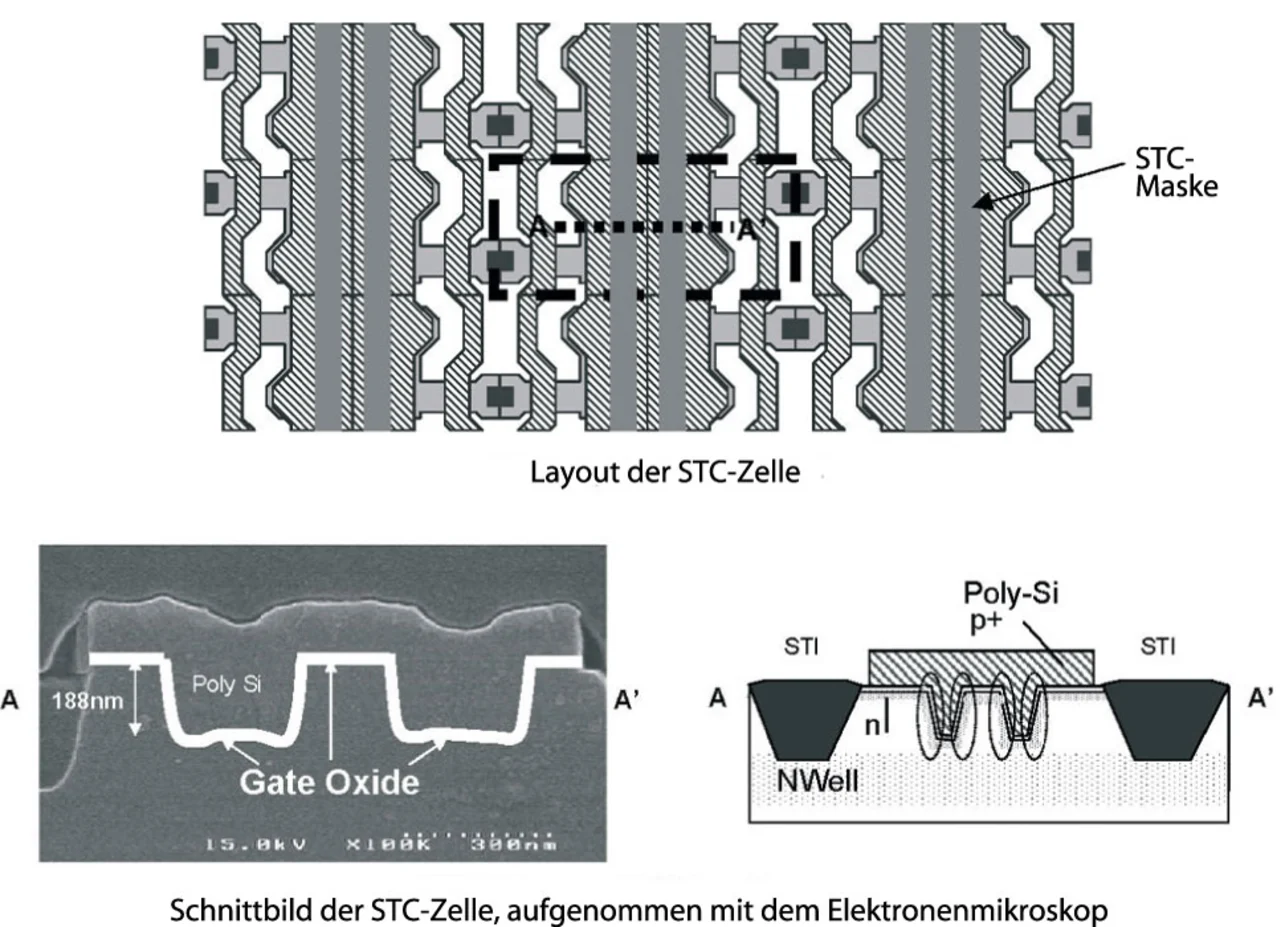

Zufallszugriffe bei einer Taktfrequenz von 300 MHz sind heute bei Embedded DRAMs Stand der Technik. Dass die präzise Abstimmung von Schaltungen die Erfassungsmargen erheblich erhöhen kann, zeigte ein 322-MHz-Embedded-DRAM von Matsushita. Der in einem 90-nm-Logikprozess realisierte Baustein ist durch eine rauscharme Architektur und eine hochgenaue Abstimmung nach der Fertigung gekennzeichnet. Mit einer Kapazität der Zelle von 5 fF, einer Verbesserung von 61 % bezüglich der Erfassungsgenauigkeit (sensing accuracy), lässt sich der Chip mit 322 MHz betreiben und benötigt nur eine Leistung von 60 µW für die Datenauffrischung. Gleichzeitig hat Matsushita noch ein 400-MHz-Dual-Port-Interleaved-DRAM mit „Striped Trench“-Kondensator-Zelle (Bild 7) und einer Kapazität von 10 fF vorgestellt, das in einem 0,15-µm-Prozess realisiert wurde. Zu den Spezialitäten gehören bei diesem Chip eine „sense-signal-loss“-Kompensation, die auf dem genauen Rauschverhalten basiert, sowie eine „write-before-sensing“-Schaltung.

Richtig Messen mit dem USB-Scope

Ein die USB-Boxen fundiert erläuterndes Buch ist unter der ISBN 978-3-7723-4307-0 im Franzis-Verlag erschienen und kostet 19,75 Euro. Es nennt sich „Richtig Messen mit dem USB-Scope“, der Autor ist Frank Sichla. Das Buch beschreibt, wie USBScopes ein Notebook oder den PC zum leistungsfähigen Oszilloskop, dem Allround-Messgerät in der Elektronik, erweitern. Der Autor vermittelt in diesem Buch nicht nur praktisches Rundumwissen zu den USB-Scopes, zu Grundtypen, Technik und Anwendungsmöglichkeiten sowie -grenzen, sondern liefert auch praktische Bauanleitungen und interessante Schaltungen für sinnvolles Zubehör. Damit kann man das Scope beträchtlich aufwerten. Die Vorstellung einiger USB-Scopes anhand wichtiger Daten und Testergebnisse rundet das Thema ab. Dabei wird deutlich, wie vielseitig USB-Scopes sein können. Einige Kapitel:

- Der Universal Serial Bus (USB)

- Tipps für die Messung mit dem USB-Scope

- Einfache aktive Tastköpfe

- Mehrkanalschalter-Vorsätze

- Wobbeln mit dem USB-Scope

- Schaltungen für Wobbelzusätze

- Grafik auf dem Scope-Schirm

- Prüfen und Testen von USB-Scopes

Zu den klassischen DRAM-Bausteinen gehören zwei von Samsung vorgestellte Bausteine, die beide in 80-nm-DRAM-Prozessen hergestellt wurden: Bei einem Baustein handelt es sich um ein 2-Gbit-DDR2-SDRAM mit einer Datenübertragungsrate von 800 Mbit/s pro Pin, das in einem Triple-Metal-Prozess für eine Betriebsspannung von 1,8 V gefertigt wurde. Beim Entwurf des 195,6 mm2 großen DRAM wurde von statistischer Schaltungsanalyse und einem „NMOS-Precharge-I/O-Scheme“ Gebrauch gemacht. Die Speicherzelle auf Basis eines MIM-Kondensators misst 0,054 µm2. Der zweite DRAM-Baustein mit einer Speicherkapazität von 256 Mbit zeichnet sich durch eine Datenübertragungsrate von 20 Gbyte/s aus. Eine präzise Quadratur-PLL, die von einem induktivitätslosen tetrahedralen Oszillator gesteuert wird, erzeugt inhärente Quadratur-Phasen, die zusammen mit einem kaskadierten „Pre-Emphasis-Transmitter“ eine Datenrate von 10 Gbit/s pro Pin ermöglichen.

Etwas exotischere Vertreter der dynamischen Speicher sind die CAMs (content addressable memories), die auf die Eingabe von Daten zugehörige Speicheradressen ausgeben. Für diese, typischerweise in Vernetzungsanwendungen eingesetzten Bausteine sind eine hohe Suchgeschwindigkeit und eine niedrige Leistungsaufnahme wichtig. Forscher von der Cheng-Chung-Universität in Taiwan haben dazu einen CAM-Chip in einem 0,18-µm-CMOS-Prozess mit einer Betriebsspannung von 1,8 V realisiert. Der CAM-Baustein mit einer Organisation von 256 x 128 bit auf Basis einer AND-Architektur bietet eine kürzere Suchzeit von 1,75 ns bei einem um rund 20 % reduzierten Energieverbrauch von 0,57 fJ/bit/Suche im Vergleich zu NOR- und NAND-Architekturen.

Bei den statischen Speichern (SRAMs) ist das Ende der Entwicklung nicht abzusehen. Die klassische 6-Transistor-Zelle ist nach wie vor weit verbreitet und doch zeigen die Papers auf der ISSCC Fortschritte bei der Dichte, bei der Reduzierung der Leckströme, beim Betrieb mit immer niedrigeren Spannungen sowie bei der Leistungsaufnahme.

Intel stellte ein 70-Mbit-SRAM vor, das in einem 65-nm-Prozess gefertigt wurde und sich bei einer Betriebsspannung von 1,1 V mit einer Taktfrequenz von 3 GHz betreiben lässt. Eine dynamische Umschaltung zwischen zwei Stromversorgungen optimiert – abhängig von den Betriebsarten Schreiben, Lesen und Stand-by – die Leistungsaufnahme und Performance des Speichers.

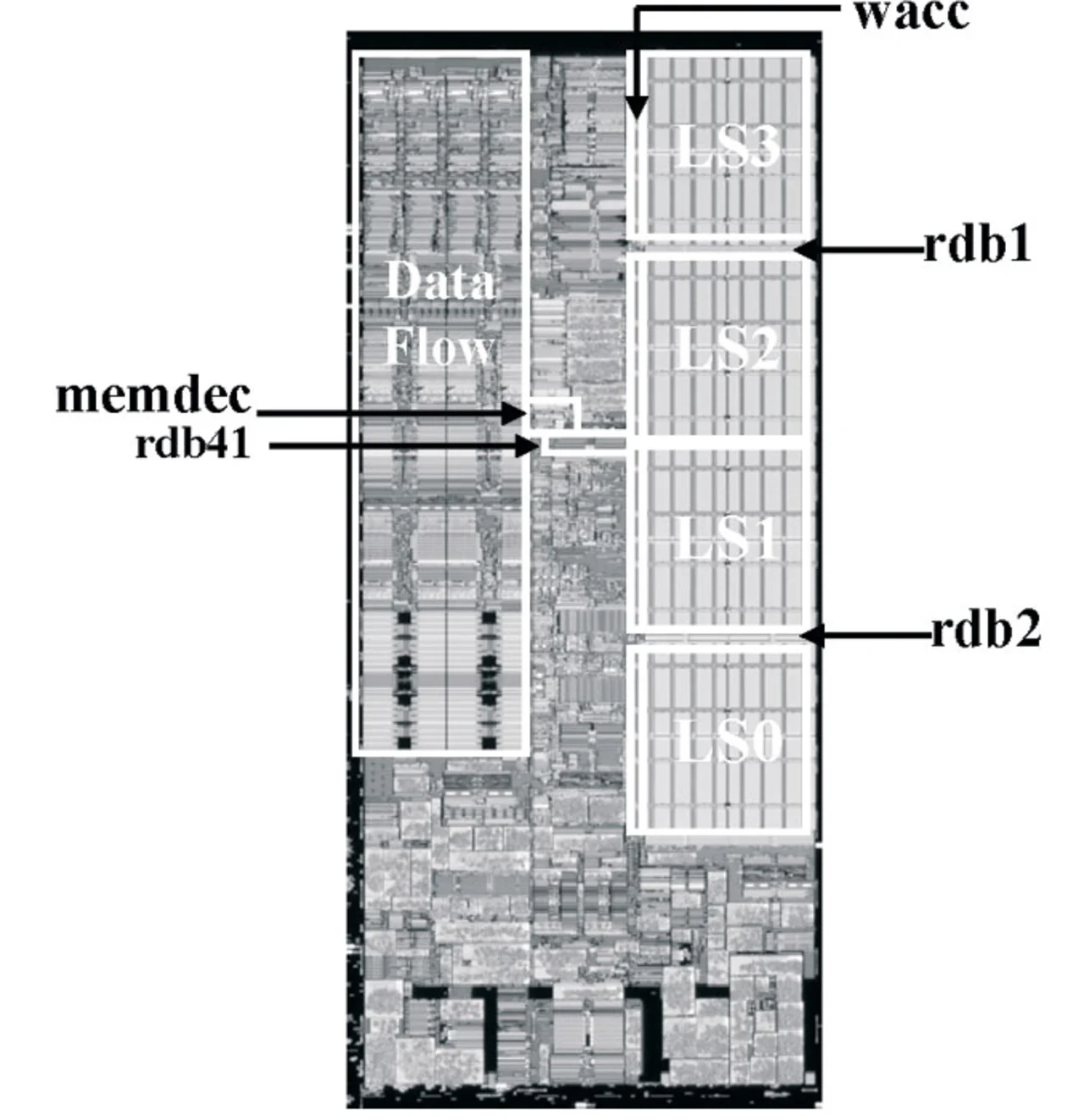

Einen mit einer Taktfrequenz von 4,8 GHz besonders schnellen SRAM-Cache präsentierte IBM (Bild 8). Der Cache mit 6-stufiger Pipeline ist Teil des Cell-Prozessors und wurde in einem 90-nm-SOI-Prozess realisiert [3].

Samsung berichtete von einem 256-Mbit-DDR-SRAM mit hierarchischer Bit-Leitungs-Architektur. Im Gegensatz zum planaren Aufbau norma-ler SRAM-Zellen stapelte man Einkristall-Silizium-Dünnschicht-Transistoren(single-crystal-silicon TFT), womit man eine kompakte Zellenfläche von 0,16 µm2 erzielen konnte (Bild 9). Der in einem 80-nm-Prozess realisierte, 61,1 mm2 große Chip erreicht eine Datenrate von 280 Mbit/s bei einem Strom von 17 mA.

Einen neuen Rekord bezüglich niedriger Betriebsspannungen dürfte Matsushita mit einem 32 kbit großen SRAM-Block zum Einsatz in 0,13-µm-CMOS-Prozessen aufgestellt haben: Das SRAM arbeitet schon mit Spannungen von 0,3 V, allerdings dann nur mit Taktfrequenzen von 6,8 MHz. Für 30 MHz sind bereits 0,4 V erforderlich und bei 1,5 V steigt die maximale Taktfrequenz auf 960 MHz. Zwei Entwurfsmaßnahmen ermöglichen die niedrigen Spannungswerte: ein Zugriffsverfahren, das Baustein-Streuungen toleriert, und ein gegen kosmische Einstrahlung immunes Fehlerkorrekturverfahren (ECC). Nicht weit weg davon ist das 64-Kbit-Makro für 90-nm-Designs von NEC: Das SRAM-Makro kommt mit einer minimalen Betriebsspannung von 440 mV aus. Im typischen Betrieb mit 0,5 V beträgt die Zugriffszeit 20 ns. Ebenfalls auf eine niedrige Spannung von minimal 0,8 V ist das 512 Kbit große Embedded-SRAM-Modul von Hitachi getrimmt. Bei einem Leckstrom von 7,8 µA lässt sich der Speicherblock immerhin mit 450 MHz takten.

Ein echtes Schwergewicht ist der SRAM-Cache auf dem neuesten Dual-Core-Itanium-Prozessor von Intel und HP: Der 24 Mbyte große L3-Cache umfasst mehr als 1,47 Mrd. Transistoren [3]. Der Cache stützt sich auf asynchrone Schaltungstechniken, um Latenzzeiten und die Leistungsaufnahme möglichst niedrig zu halten. Das 5-Zyklen-Array arbeitet mit 2 GHz bei 0,8 V und 85 °C und nimmt weniger als 4,2 W auf.

- Kompakt-Oszilloskope für den USB können immer mehr

- Kompakt-Oszilloskope für den USB können immer mehr

- Literatur